Académique Documents

Professionnel Documents

Culture Documents

Adelanto Atraso

Transféré par

Mario Alberto GodoyTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Adelanto Atraso

Transféré par

Mario Alberto GodoyDroits d'auteur :

Formats disponibles

DISEO CON EL CONTROLADOR DE ADELANTO DE FASE El controlador PID (proporcional, integral y derivativo) En general, el diseo de controladores en sistemas de control

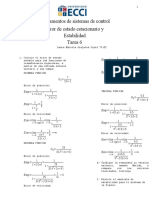

se puede ver como un problema de diseo diseo de filtros; entonces existe un gran numero de esquemas posibles. El filtro paso altas a menudo se denomina como controlador de adelanto de fase ya que se introduce fase positiva al sistema en algn intervalo de frecuencias. El filtro paso ajas tambin se conoce como controlador de atraso de fase, ya que la fase correspondiente introducida es negativa. La funcin de transferencia de un controlador e adelanto o atraso sencillo se expresa como:

en donde el controlador es paso altas o de adelanto de fase si p1>z1, y paso bajas o de atraso de fase si p1<z1. La implementacin del circuito con amplificadores operacionales de la ecuacin presenta en la fig. siguiente con un amplificador inversor. La funcin e transferencia del circuito es:

Al comparar las dos ultimas ecuaciones, se tiene: Kc=c1/C2 Z1=1/R1C1 P1=1/R2C2 Se puede reducir el nmero de parmetros de diseo de cuatro a tres al hacer que C=C1=C2 entonces la ecuacin se escribe como:

Interpretacin y diseo en el dominio del tiempo del control de adelanto de fase Para que el controlador de adelanto de fase no degrade el error en estado estable, el factor a de la ecuacin anterior debe ser absorbido por la ganancia de la trayectoria directa K. Entonces, para propsitos de diseo, Gc(s) se puede escribir como:

Se observa que el controlador de adelanto de fase puede mejorar la estabilidad del sistema en lazo cerrado si sus parmetros se escogen en forma adecuada. En resumen, el diseo de control de adelanto de fase consiste en colocar el polo y el cero de Gc(s) para que las especificaciones de diseo sean satisfechas. DISEO CON EL CONTROLADOR DE ATRASO DE FASE La funcin de transferencia de la ecuacin

representa un controlador de atraso de fase o filtro pasa bajas cuando a<1. La funcin de transferencia se repite como sigue:

La configuracin de polos y ceros de Gc(s) se muestra en la siguiente figura. Contrario al controlador PI, el cual provee un polo en s=0, el controlador de atraso de fase afecta el error en estado estable solamente en el sentido de que la ganancia en frecuencia cero de Gc(s) es mayor que la unidad.

Por tanto, cualquier constante de error que sea finita y no cero ser incrementada por el factor 1/a del controlador de atraso de fase. Ya que el polo en s=-1/T esta a la derecha del cero en 1/aT, el empleo efectivo del controlador de atraso e fase para mejorar el amortiguamiento podra tener que seguir el mismo principio de diseo el control PI. Por lo tanto, la forma adecuada de aplicar el control e atraso de fase es colocar el polo y el cero muy cercanos. Para sistemas de tipo 0 y de tipo 1 la combinacin debe estar ubicada cercana al origen en el plano s.

Vous aimerez peut-être aussi

- Ing Control-CompensacionDocument38 pagesIng Control-CompensacionManuel LaguadoPas encore d'évaluation

- Análisis y Diseño de Un Controlador Pid AnalógicoDocument8 pagesAnálisis y Diseño de Un Controlador Pid AnalógicoWences LaoPas encore d'évaluation

- Cap9 CompensacionDocument43 pagesCap9 CompensacionCelula CarlosPas encore d'évaluation

- Tif Compnsador de Un Generador SincronoDocument10 pagesTif Compnsador de Un Generador SincronoDaniel PeñaPas encore d'évaluation

- 9 Diseño Compensacion Sistemas Control RealimentacionDocument43 pages9 Diseño Compensacion Sistemas Control RealimentacionestefaPas encore d'évaluation

- Informe PDDocument10 pagesInforme PDERICK JES�S TAMAYO LLANTOPas encore d'évaluation

- Informe PDDocument10 pagesInforme PDERICK JES�S TAMAYO LLANTOPas encore d'évaluation

- Diseño Control Prop. Adelanto de FaseDocument66 pagesDiseño Control Prop. Adelanto de Fasemayquer lin delgadillo perezPas encore d'évaluation

- Control AdoresDocument12 pagesControl AdoresedgonPas encore d'évaluation

- Diseño de Compensadores en Atraso-AdelantoDocument8 pagesDiseño de Compensadores en Atraso-AdelantoKOCOEDITH50% (2)

- Resumen Libro OgataDocument12 pagesResumen Libro OgataOscar VeraPas encore d'évaluation

- 1.1-TEC - DEL DIS DE COMP EN SERIE EN Dom TiempoDocument126 pages1.1-TEC - DEL DIS DE COMP EN SERIE EN Dom TiempoDanny Erquinio LopezPas encore d'évaluation

- Proceso de Diseño Con Controladores PDDocument27 pagesProceso de Diseño Con Controladores PDMoises Cruz MostacedoPas encore d'évaluation

- 1.1-Tec - Del Dis de Comp en Serie en Dom TiempoDocument139 pages1.1-Tec - Del Dis de Comp en Serie en Dom TiempoFSaul LazaroPas encore d'évaluation

- Laboratorio 2Document11 pagesLaboratorio 2ELIAN EDMUNDO ARENAS YATACOPas encore d'évaluation

- CTRL P Pi PidDocument16 pagesCTRL P Pi PidJoan Sebastian Ortiz TrujequePas encore d'évaluation

- Análisis y Diseño de Controladores en El TiempoDocument23 pagesAnálisis y Diseño de Controladores en El Tiemporoberto roblesPas encore d'évaluation

- Control PidDocument18 pagesControl PidMiguelSalgadoPas encore d'évaluation

- Investigación Control DifusoDocument17 pagesInvestigación Control DifusoRenato Angel Basurto MonteroPas encore d'évaluation

- Descripcion Simulacion PidDocument7 pagesDescripcion Simulacion PidJohn Alexander HidalgoPas encore d'évaluation

- Tarea 10, Ingenieria, Daniel HernandezDocument21 pagesTarea 10, Ingenieria, Daniel HernandezPepsy MendezPas encore d'évaluation

- 3.-Diseño e ImplementacionDocument30 pages3.-Diseño e ImplementacionOscar CristianPas encore d'évaluation

- Caracterización de Una PlantaDocument6 pagesCaracterización de Una PlantacalietzchePas encore d'évaluation

- Diseño Por Retardo de Fase Utilizando El Diagrama de BodeDocument30 pagesDiseño Por Retardo de Fase Utilizando El Diagrama de BodeVikthor Lopez100% (1)

- Guia 7Document15 pagesGuia 7FabianBañoPas encore d'évaluation

- Electronica PidDocument6 pagesElectronica PidTony Sanchez ChambaPas encore d'évaluation

- Compensadores Adelanto de FaseDocument14 pagesCompensadores Adelanto de FaseDavid GerardoPas encore d'évaluation

- Parte BDocument20 pagesParte BBenny Samir Bauitsta EscobarPas encore d'évaluation

- Practica 1 Compensador de Tipo Pasivo de Adelanto de FaseDocument14 pagesPractica 1 Compensador de Tipo Pasivo de Adelanto de FaseDaniel Reyes Vasquez100% (1)

- Proyecto de Motor CDDocument14 pagesProyecto de Motor CDAlexFernandoAlexParedesPas encore d'évaluation

- Tarea 3 Ing. Control (Respuesta de Frecuencia) Yaniel Leliebre PelaezDocument10 pagesTarea 3 Ing. Control (Respuesta de Frecuencia) Yaniel Leliebre PelaezYaniel LeliebrePas encore d'évaluation

- Ziegler NicholsDocument27 pagesZiegler NicholsJessPas encore d'évaluation

- Laboratorio 4 - Diagramas de BodeDocument10 pagesLaboratorio 4 - Diagramas de Bodemaria_carbajal_390% (1)

- Análisis Dinámico de Un ControladorDocument32 pagesAnálisis Dinámico de Un ControladorJuan Roldán Castillo100% (1)

- Pid 8Document10 pagesPid 8Marco DominguezPas encore d'évaluation

- Control AdoresDocument11 pagesControl AdoresMARIA VALERIA QUILUMBA RUIZPas encore d'évaluation

- 1.1-TEC - Diseño de Compensadores en El Dominio Del TiempoDocument129 pages1.1-TEC - Diseño de Compensadores en El Dominio Del TiempoChristian DanielPas encore d'évaluation

- PreguntasDocument8 pagesPreguntasBartomeuPas encore d'évaluation

- Diseño de CompensadorDocument13 pagesDiseño de CompensadorErlanDuartePas encore d'évaluation

- Control PDDocument12 pagesControl PDrodrigoPas encore d'évaluation

- 1.1-Tec - Del Dis de Comp en Serie en Dom TiempoDocument138 pages1.1-Tec - Del Dis de Comp en Serie en Dom TiempoGisela Nateros MartinezPas encore d'évaluation

- Resumen de Controles NicoleDocument6 pagesResumen de Controles NicoleNICOLE VALENCIAPas encore d'évaluation

- FrecuencímetroDocument6 pagesFrecuencímetroJohn Alexander ArévaloPas encore d'évaluation

- 3.2 Sintonización de ControladoresDocument8 pages3.2 Sintonización de ControladoresKarla TorresPas encore d'évaluation

- Proyecto de Controladores en El Dominio Del TiempoDocument25 pagesProyecto de Controladores en El Dominio Del TiemponelsonPas encore d'évaluation

- Ingenieria de ControlDocument74 pagesIngenieria de ControlStalin YaguanaPas encore d'évaluation

- Reporte P7 John PozoDocument12 pagesReporte P7 John PozoJohn Andrés Pozo VillónPas encore d'évaluation

- Articulo IEEE PDFDocument7 pagesArticulo IEEE PDFabhywaPas encore d'évaluation

- Informe 5 Sistemas de ControlDocument15 pagesInforme 5 Sistemas de ControlPablo Sandoval UrionaPas encore d'évaluation

- Proyecto Control de Procesos IIDocument19 pagesProyecto Control de Procesos IIHikari Ayame FloresPas encore d'évaluation

- Informe Control Practica5Document16 pagesInforme Control Practica5Andrew Israel QPas encore d'évaluation

- Control Automatico de Generacion, AcgDocument3 pagesControl Automatico de Generacion, Acgnectelur_1990100% (1)

- Control de PosicionDocument17 pagesControl de PosicionDaniel Rocha UgaldePas encore d'évaluation

- Consulta RagazziniDocument7 pagesConsulta RagazziniAna Montaño Vizcaíno100% (1)

- Diseño de Lazoz Pid Por Polos y CerosDocument19 pagesDiseño de Lazoz Pid Por Polos y Cerosavengers vengadorPas encore d'évaluation

- Ejercicios de Integrales de Línea, Superficie y VolumenD'EverandEjercicios de Integrales de Línea, Superficie y VolumenÉvaluation : 4 sur 5 étoiles4/5 (2)

- Corrección gamma: Mejora de la claridad visual en la visión por computadora: la técnica de corrección gammaD'EverandCorrección gamma: Mejora de la claridad visual en la visión por computadora: la técnica de corrección gammaPas encore d'évaluation

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaD'EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaPas encore d'évaluation

- Armónicas en Sistemas Eléctricos IndustrialesD'EverandArmónicas en Sistemas Eléctricos IndustrialesÉvaluation : 4.5 sur 5 étoiles4.5/5 (12)

- Servicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoD'EverandServicios complementarios en sistemas eléctricos de potencia: Análisis y modelamientoÉvaluation : 5 sur 5 étoiles5/5 (1)

- Prevención de Accidentes Con GasesDocument50 pagesPrevención de Accidentes Con GasesAlejandro Alan Rozas CorralesPas encore d'évaluation

- Informe Poisson Lab. CalidadDocument12 pagesInforme Poisson Lab. CalidadDaniel Carvajal Tinoco100% (2)

- Vigas Isostatica e Hiperestaticas - (PDF Document) .HTMLDocument27 pagesVigas Isostatica e Hiperestaticas - (PDF Document) .HTMLwendy quispePas encore d'évaluation

- Sobre La VariabilidadDocument17 pagesSobre La VariabilidadEDUARDO ESCOTO MARTINEZPas encore d'évaluation

- Universidad Nacional de ChimborazoDocument7 pagesUniversidad Nacional de ChimborazoMayte MielesPas encore d'évaluation

- Diagrama de Bode DiscretoDocument4 pagesDiagrama de Bode DiscretoOmar Lopez Arias0% (1)

- Cinemática Del TraumaDocument18 pagesCinemática Del Traumajhony bedoyaPas encore d'évaluation

- Principio Del Trabajo VirtualDocument7 pagesPrincipio Del Trabajo VirtualJhon AguilarPas encore d'évaluation

- El VentiladorDocument5 pagesEl VentiladorFernanda LealPas encore d'évaluation

- Identificaciones Cationes Del Cuarto GrupoDocument6 pagesIdentificaciones Cationes Del Cuarto GrupoSamuel Arizmendi Martínez60% (5)

- Cuadernillo Practicas GeografiaDocument36 pagesCuadernillo Practicas GeografiaBetoPas encore d'évaluation

- La Paradoja Del Gato de SchrödingerDocument3 pagesLa Paradoja Del Gato de SchrödingerBenito TenebrosusPas encore d'évaluation

- Tarea4-Fundamentos de Sistemas de ControlDocument7 pagesTarea4-Fundamentos de Sistemas de ControlLaura Marcela Grajales LópezPas encore d'évaluation

- ALÓTROPOSDocument5 pagesALÓTROPOSElena Borrego BlancoPas encore d'évaluation

- Problemas Ut7Document12 pagesProblemas Ut7Edwin FazPas encore d'évaluation

- Filtros HepaDocument7 pagesFiltros Hepacavasque100% (2)

- Exparc RM 2020 1Document2 pagesExparc RM 2020 1Jose Villarreal OroscoPas encore d'évaluation

- Catarinas y CadenasDocument26 pagesCatarinas y CadenasAmado Fco MorenoPas encore d'évaluation

- Desinfección Por Luz UltravioletaDocument8 pagesDesinfección Por Luz UltravioletaDaniel DacostaPas encore d'évaluation

- Análisis PVTDocument3 pagesAnálisis PVTDaniel RamirezPas encore d'évaluation

- Fluidos Fracturantes Equipo 5Document34 pagesFluidos Fracturantes Equipo 5Gerardo Reyes100% (5)

- Tipos y Clasificación de Cable, Fusibles, Relés y 2Document9 pagesTipos y Clasificación de Cable, Fusibles, Relés y 2jean vicuña mirandaPas encore d'évaluation

- Ecuacier 7abril RJL FVDocument12 pagesEcuacier 7abril RJL FVFernando VacaPas encore d'évaluation

- Estudio Climatográfico de La Ciudad de ConcepciónDocument7 pagesEstudio Climatográfico de La Ciudad de ConcepciónEdwarhor100% (1)

- Las Aguas Subterraneas en Los DeslizamientosDocument65 pagesLas Aguas Subterraneas en Los DeslizamientosYoan Barriga BerriosPas encore d'évaluation

- Catalogo de Arandelas NORD LOCKDocument16 pagesCatalogo de Arandelas NORD LOCKWilfordPas encore d'évaluation

- 3000P - 4500 Español PDFDocument72 pages3000P - 4500 Español PDFGuStavoBobadilla86% (7)

- Bombas GeneralDocument24 pagesBombas GeneralJonas BorjasPas encore d'évaluation

- Utilizacion de Reconectador Por Pulsos en Alimentadores Aereos de Media TensionDocument24 pagesUtilizacion de Reconectador Por Pulsos en Alimentadores Aereos de Media TensionRicardo DoldanPas encore d'évaluation

- Actividad de Aprendizaje 4Document4 pagesActividad de Aprendizaje 4luis HernándezPas encore d'évaluation