Académique Documents

Professionnel Documents

Culture Documents

Diagrama Procesador

Transféré par

Ana PimentelTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Diagrama Procesador

Transféré par

Ana PimentelDroits d'auteur :

Formats disponibles

El microprocesador 80386

Introduccin

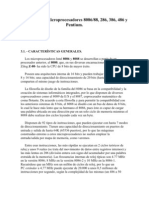

El 80386 consiste en una unidad central de proceso (CPU), una unidad de manejo de memoria (MMU) y una unidad de interfaz con el bus (BIU). La CPU est compuesta por la unidad de ejecucin y la unidad de instrucciones. La unidad de ejecucin contiene los ocho registros de 32 bits de propsito general que se utilizan para el clculo de direcciones y operaciones con datos y un barrel shifter de 64 bits que se utiliza para acelerar las operaciones de desplazamiento, rotacin, multiplicacin y divisin. Al contrario de los microprocesadores previos, la lgica de divisin y multiplicacin utiliza un algoritmo de 1 bit por ciclo de reloj. El algoritmo de multiplicacin termina la iteracin cuando los bits ms significativos del multiplicador son todos ceros, lo que permite que las multiplicaciones tpicas de 32 bits se realicen en menos de un microsegundo. La unidad de instruccin decodifica los cdigos de operacin (opcodes) de las instrucciones que se encuentran en una cola de instrucciones (cuya longitud es de 16 bytes) y los almacena en la cola de instrucciones decodificadas (hay espacio para tres instrucciones). El sistema de control de la unidad de ejecucin es el encargado de decodificar las instrucciones que le enva la cola y enviarle las rdenes a la unidad aritmtica y lgica segn una tabla que tiene almacenada en ROM llamada CROM (Control Read Only Memory). La unidad de manejo de memoria (MMU) consiste en una unidad de segmentacin (similar a la del 80286) y una unidad de paginado (nuevo en este microprocesador). La segmentacin permite el manejo del espacio de direcciones lgicas agregando un componente de direccionamiento extra, que permite que el cdigo y los datos se puedan reubicar fcilmente. El mecanismo de paginado opera por debajo y es transparente al proceso de segmentacin, para permitir el manejo del espacio de direcciones fsicas. Cada segmento se divide en uno o ms pginas de 4 kilobytes. Para implementar un sistema de memoria virtual (aqul donde el programa tiene un tamao mayor que la memoria fsica y debe cargarse por partes (pginas) desde el disco rgido), el 80386 permite seguir ejecutando los programas despus de haberse detectado fallos de segmentos o de pginas. Si una pgina determinada no se encuentra en memoria, el 80386 se lo indica al sistema operativo mediante la excepcin 14, luego ste carga dicha pgina desde el disco y finalmente puede seguir ejecutando el programa, como si hubiera estado dicha pgina todo el tiempo. Como se puede observar, este proceso es transparente para la aplicacin, por lo que el programador no debe preocuparse por cargar partes del cdigo desde el disco ya que esto lo hace el sistema operativo con la ayuda del microprocesador. La memoria se organiza en uno o ms segmentos de longitud variable, con tamao mximo de 4 gigabytes. Estos segmentos, como se vio en la explicacin del 80286, tienen atributos asociados, que incluyen su ubicacin, tamao, tipo (pila, cdigo o datos) y caractersticas de proteccin.

La unidad de segmentacin provee cuatro niveles de proteccin para aislar y proteger aplicaciones y el sistema operativo. Este tipo de proteccin por hardware permite el diseo de sistemas con un alto grado de integridad. El 80386 tiene dos modos de operacin: modo de direccionamiento real (modo real), y modo de direccionamiento virtual protegido (modo protegido). En modo real el 80386 opera como un 8086 muy rpido, con extensiones de 32 bits si se desea. El modo real se requiere primariamente para preparar el procesador para que opere en modo protegido. El modo protegido provee el acceso al sofisticado manejo de memoria y paginado. Dentro del modo protegido, el software puede realizar un cambio de tarea para entrar en tareas en modo 8086 virtual (V86 mode) (esto es nuevo con este microprocesador). Cada una de estas tareas se comporta como si fuera un 8086 el que lo est ejecutando, lo que permite ejecutar software de 8086 (un programa de aplicacin o un sistema operativo). Las tareas en modo 8086 virtual pueden aislarse entre s y del sistema operativo (que debe utilizar instrucciones del 80386), mediante el uso del paginado y el mapa de bits de permiso de entrada/salida (I/O Permission Bitmap). Finalmente, para facilitar diseos de hardware de alto rendimiento, la interfaz con el bus del 80386 ofrece pipelining de direcciones, tamao dinmico del ancho del bus de datos (puede tener 16 32 bits segn se desee en un determinado ciclo de bus) y seales de habilitacin de bytes por cada byte del bus de datos. Hay ms informacin sobre esto en la seccin de hardware del 80386.

Diagrama en bloques del 80386

Vous aimerez peut-être aussi

- Arquitectura Del Microprocesador 80286Document20 pagesArquitectura Del Microprocesador 80286Richard vega marcelo100% (1)

- Microprocesadores y Su Administracion de La MemoriaDocument9 pagesMicroprocesadores y Su Administracion de La MemoriaKarlita M.Pas encore d'évaluation

- Intel 386Document26 pagesIntel 386joseph_arce_7Pas encore d'évaluation

- Segmentacion 80386Document4 pagesSegmentacion 80386Ivans GonzalezPas encore d'évaluation

- Semana02 38697Document26 pagesSemana02 38697Mariela AcostaPas encore d'évaluation

- MicrocontroladoresDocument10 pagesMicrocontroladoresJHONATAN PAREDES EQUISEPas encore d'évaluation

- Administración de Memoria Del Microprocesador 80386Document10 pagesAdministración de Memoria Del Microprocesador 80386Karlita M.Pas encore d'évaluation

- El Modo RealDocument3 pagesEl Modo RealFraanz EzpiRithuuPas encore d'évaluation

- Arquitectura y Diseño de Seguridad Resumen 3Document16 pagesArquitectura y Diseño de Seguridad Resumen 3Miguel Angel Vargas ReynosoPas encore d'évaluation

- 1.3 Arquitectura Interna Del MicroprocesadorDocument51 pages1.3 Arquitectura Interna Del MicroprocesadorBandini ArturoPas encore d'évaluation

- Micros Lista 06Document19 pagesMicros Lista 06pmfornerisPas encore d'évaluation

- Capítulo III. - MicroprocesadoresDocument15 pagesCapítulo III. - MicroprocesadoresShirohimePas encore d'évaluation

- Interrupciones y TemporizaciÓnDocument9 pagesInterrupciones y TemporizaciÓningzepe100% (3)

- Familia Microprocesadores X86Document12 pagesFamilia Microprocesadores X86Lucas Matías JuarezPas encore d'évaluation

- CUESTIONARIO PARA Examen-Mantenimiento-Reparacion-ComputadorasDocument53 pagesCUESTIONARIO PARA Examen-Mantenimiento-Reparacion-ComputadorasBlut NashiPas encore d'évaluation

- 02 Unidad IIDocument25 pages02 Unidad IIBraian Stalin Pineda ReyesPas encore d'évaluation

- Procesadores 1Document29 pagesProcesadores 1KELSOFT CAPas encore d'évaluation

- El UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Document4 pagesEl UP 8086 Fue de Los Primeros en Utilizar Un Bus de 16Annie UniPas encore d'évaluation

- Capítulo 2 El Microcontrolador y Su ArquitecturaDocument37 pagesCapítulo 2 El Microcontrolador y Su ArquitecturaKvtz AydynPas encore d'évaluation

- Unidad Central de ProcesamientoDocument18 pagesUnidad Central de ProcesamientoJaime Hernnadez LopezPas encore d'évaluation

- Gestión de Memoria en El Pentium II y en El powerPCDocument8 pagesGestión de Memoria en El Pentium II y en El powerPCmargutierrezPas encore d'évaluation

- Arquitectura MicroprocesadoresDocument16 pagesArquitectura MicroprocesadoresMonserrat MejíaPas encore d'évaluation

- Direccionamiento en Modo RealDocument4 pagesDireccionamiento en Modo RealJulio QuintanaPas encore d'évaluation

- Tema 8. Arquitectura - GST 2019-2020 - GUÍA - v1 PDFDocument13 pagesTema 8. Arquitectura - GST 2019-2020 - GUÍA - v1 PDFAlphaxinoPas encore d'évaluation

- Modalidades de OperacionDocument5 pagesModalidades de OperacionEdgar Dante AllighieriPas encore d'évaluation

- Arquitectura de Computadoras 2018Document26 pagesArquitectura de Computadoras 2018CarlosPas encore d'évaluation

- Administracion de MemoriaDocument58 pagesAdministracion de MemoriaDaniel Omar GarciaPas encore d'évaluation

- Unidad 5. Los Procesadores - Arquitectura de ComputadorasDocument26 pagesUnidad 5. Los Procesadores - Arquitectura de ComputadorasJuan CarlosPas encore d'évaluation

- A3. Resumen Del Tema Arquitecturas x86-64 ANMV 3612Document3 pagesA3. Resumen Del Tema Arquitecturas x86-64 ANMV 3612Angela Nereida MVPas encore d'évaluation

- Microprocesador Intel 4004Document3 pagesMicroprocesador Intel 4004Erick MontoyaPas encore d'évaluation

- Tarea de Arquitectura.1Document12 pagesTarea de Arquitectura.1Anonymous P0PJwz1Pas encore d'évaluation

- Micro Proce Sad orDocument82 pagesMicro Proce Sad orOscar Duque SuarezPas encore d'évaluation

- Sistemas Operativos - Capitulo IIIDocument11 pagesSistemas Operativos - Capitulo IIILuis Fernando JimenezPas encore d'évaluation

- Como Funciona El Procesamiento en ParaleloDocument4 pagesComo Funciona El Procesamiento en ParaleloFrancesco RuggieroPas encore d'évaluation

- Arquitectura IA 32Document12 pagesArquitectura IA 32Ivonne DíazPas encore d'évaluation

- Registro de Segmento Del MicroprocesadorDocument6 pagesRegistro de Segmento Del MicroprocesadorStevenFelipeQuinteroMartínezPas encore d'évaluation

- Aspectos Internos de Las ComputadorasDocument18 pagesAspectos Internos de Las ComputadorasDoña HimchanPas encore d'évaluation

- Direccionamiento de MemoriaDocument10 pagesDireccionamiento de MemoriaGustavo Joaquín Bustamante JaurePas encore d'évaluation

- CgrwyDocument17 pagesCgrwyKevin SosaPas encore d'évaluation

- Contenido Clase 2 MicrocontroladoresDocument11 pagesContenido Clase 2 MicrocontroladoresEdith Roa LegalPas encore d'évaluation

- Banco 8088 y 8086Document12 pagesBanco 8088 y 8086Brayhan Torres100% (1)

- Microprocesadores de 16 y 32 BitsDocument13 pagesMicroprocesadores de 16 y 32 BitsLuis Angel Casados Rodriguez100% (1)

- Reloj Del SistemaDocument11 pagesReloj Del SistemaSandra Gabriela Coca OrtizPas encore d'évaluation

- Diferencia Entre Un Microprocesador y Un MicrocontroladorDocument7 pagesDiferencia Entre Un Microprocesador y Un MicrocontroladorIrving Jesus Sanchez CamposPas encore d'évaluation

- Controlador 1.0Document6 pagesControlador 1.0Jose David FloresPas encore d'évaluation

- Microprocesadores UNIDAD IDocument10 pagesMicroprocesadores UNIDAD IDarwin DorantePas encore d'évaluation

- Informe Memoria 3x4Document10 pagesInforme Memoria 3x4Andresinho SievchenkoPas encore d'évaluation

- Tipos y Velocidades de ProcesadoresDocument12 pagesTipos y Velocidades de ProcesadoresJuan ValenciaPas encore d'évaluation

- Funciones y Operaciones Del Administrador de MemoriaDocument46 pagesFunciones y Operaciones Del Administrador de MemoriaOberto Jorge Santín CuestaPas encore d'évaluation

- Foro de Reforzamiento. Los Microprocesadores y Su EstructuraDocument8 pagesForo de Reforzamiento. Los Microprocesadores y Su EstructuraHugo Alberto Ortiz Anaya100% (1)

- Cuestionario MicroprocesadoresDocument6 pagesCuestionario MicroprocesadoresGénesisAndrimarPas encore d'évaluation

- Microprocesador, Memoria RAM y Disco Duro, Requerimientos Básicos de Los Sistemas Operativos.Document18 pagesMicroprocesador, Memoria RAM y Disco Duro, Requerimientos Básicos de Los Sistemas Operativos.Yajaira Soledad Chipantiza FreirePas encore d'évaluation

- MicroprocesadoresDocument17 pagesMicroprocesadoresYlenni Pimentel ReyesPas encore d'évaluation

- Foro de Reforzamiento. Los Microprocesadores y Su EstructuraDocument9 pagesForo de Reforzamiento. Los Microprocesadores y Su EstructuraHugo Alberto Ortiz AnayaPas encore d'évaluation

- Unidad 2 Estructura y Funcionamiento deDocument15 pagesUnidad 2 Estructura y Funcionamiento dejua carlosPas encore d'évaluation

- Capítulo N°2Document7 pagesCapítulo N°2Juan Francisco Herrera y MorejonPas encore d'évaluation

- MicrocontroladoresDocument13 pagesMicrocontroladoresLajuh PeñaPas encore d'évaluation

- Administracion de La Memoria (Windows & Android)Document15 pagesAdministracion de La Memoria (Windows & Android)Josue Garcia LaraPas encore d'évaluation

- Resumen Procesadores IA-32 e Intel C 64Document17 pagesResumen Procesadores IA-32 e Intel C 64Scofield MichaelPas encore d'évaluation

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Lab 04 - PrototipadoDocument4 pagesLab 04 - PrototipadoKevin BarredaPas encore d'évaluation

- C1 Qué Son Los MicroserviciosDocument26 pagesC1 Qué Son Los MicroserviciosDaniel GiardiniPas encore d'évaluation

- Ejercicio de Le Verbe FAIREDocument1 pageEjercicio de Le Verbe FAIRELía Hernández OchoaPas encore d'évaluation

- Aplicacion de Fotogrametria Digital en A PDFDocument1 pageAplicacion de Fotogrametria Digital en A PDFLaura OspinaPas encore d'évaluation

- Guia de Datos para ComputadoraDocument5 pagesGuia de Datos para ComputadoraJorge Matius SánchezPas encore d'évaluation

- Preparatorio 2 Marcos PazmiñoDocument3 pagesPreparatorio 2 Marcos PazmiñoSebastian PazmiñoPas encore d'évaluation

- MetaforaDocument7 pagesMetaforaGustavo Adolfo Peña MarínPas encore d'évaluation

- Formato para TrabajoDocument23 pagesFormato para TrabajoCesar CanabalPas encore d'évaluation

- Universidad Tecnica de LojaDocument220 pagesUniversidad Tecnica de LojaVanessa GutierrezPas encore d'évaluation

- Excel PythonDocument13 pagesExcel PythonDanna GarciaPas encore d'évaluation

- Proyecto Robot Resuelve LaberintosDocument8 pagesProyecto Robot Resuelve LaberintosCarlos De La Rosa Sanchez100% (2)

- 238 709 1 PBDocument35 pages238 709 1 PBCrovisa01Pas encore d'évaluation

- Trabajo de Investigacion Windows XPDocument5 pagesTrabajo de Investigacion Windows XPPerla Duarte CPas encore d'évaluation

- Revista Internacional de Tecnología Web y SemánticaDocument19 pagesRevista Internacional de Tecnología Web y SemánticaAlfonso NoriegaPas encore d'évaluation

- Figura 1 Representación Esquemática de Los Elementos de Un ProcesoDocument1 pageFigura 1 Representación Esquemática de Los Elementos de Un ProcesoLuz Angela Guerra UstarizPas encore d'évaluation

- Diseño de InterfazDocument3 pagesDiseño de Interfazhack gamePas encore d'évaluation

- Software de Aplicación - Sem II - Ver00 S1 PDFDocument10 pagesSoftware de Aplicación - Sem II - Ver00 S1 PDFLeticia Del Pilar CamposPas encore d'évaluation

- Edinson Castillo López - Alimentos en La Agricultura CaseraDocument33 pagesEdinson Castillo López - Alimentos en La Agricultura CaseraEdinson Castillo LopezPas encore d'évaluation

- Diseno Detallado Simulador Aguirre 2008 PDFDocument128 pagesDiseno Detallado Simulador Aguirre 2008 PDFRamiro Osorio DiazPas encore d'évaluation

- Entrevista A Un ProgramadorDocument3 pagesEntrevista A Un ProgramadorIndira FloresPas encore d'évaluation

- Programacionweb - Implementar Una Solución Web Mediante El Uso de Un CRUD en PHP, MySql y ApacheDocument4 pagesProgramacionweb - Implementar Una Solución Web Mediante El Uso de Un CRUD en PHP, MySql y ApachePaul AnthonyPas encore d'évaluation

- Soluciones de BI & BADocument33 pagesSoluciones de BI & BAJose Luis Castilla100% (1)

- Memorias CIIIS2014Document215 pagesMemorias CIIIS2014Gabriel SaavedraPas encore d'évaluation

- IndesignDocument2 pagesIndesignMartin Grima del MoralPas encore d'évaluation

- MM VL31N Creación de Entrega EntranteDocument11 pagesMM VL31N Creación de Entrega EntranteRodolfo ChungPas encore d'évaluation

- Aplicaciones OfimáticasDocument22 pagesAplicaciones OfimáticasFelix Juan Prieto MartínezPas encore d'évaluation

- Asterisk Allietti DraftDocument14 pagesAsterisk Allietti Drafthenry1234565Pas encore d'évaluation

- Actividad Diseño de SistemasDocument19 pagesActividad Diseño de SistemasHugo NakamuraPas encore d'évaluation

- Mastering RequirementsDocument47 pagesMastering RequirementsCarlos EduardoPas encore d'évaluation

- S1 Análisis Del Negocio y RequerimientosDocument70 pagesS1 Análisis Del Negocio y RequerimientosOmar Manzano CaceresPas encore d'évaluation