Académique Documents

Professionnel Documents

Culture Documents

Lab Module 3 - Logic Gate Application

Transféré par

Fahmi Faiz RosliDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Lab Module 3 - Logic Gate Application

Transféré par

Fahmi Faiz RosliDroits d'auteur :

Formats disponibles

UNIVERSITI MALAYSIA PERLIS

DIGITAL SYSTEM I (DKT122) SEMESTER 2, 2011-2012 LAB 3: LOGIC GATE APPLICATION

LECTURER: MOHAMAD RIZAL BIN ABDUL REJAB MOHD FISOL BIN OSMAN

1|Page m.rizal@unimap.edu.my

OBJECTIVES To describe the operation of the Inverter, the AND gate, and the OR gate. To verify the operation of OR, AND, NOT (Inverter) gates. To implement the operation of NAND gate and NOR gate. To construct a simple combinational logic circuits.

EQUIPMENTS AND COMPONENTS DC Power Supply (fixed 5V) Oscilloscope Multi-meter Broad Board Logic gates IC :1) 74 XX 04 - 1 unit 2) 74 XX 08 - 1 unit 3) 74 XX 32 - 1 unit 4) 74 XX 11 - 1 unit 5) 74 XX 27 - 1 unit Resistor (330 ) - 2 unit LED - 2 unit SPDT Switches - 4 unit

INTRODUCTION Digital circuits are often referred as a switching circuits because their control devices (examples, diodes and transistors) are switches between the two (2) extremes of ON and OFF functions. Logic gates have one or more inputs with one output. They respond to various input combinations. A truth table show this relationship between circuits input combinations and its output. To determine the total number of different combinational to be listed in the truth table, the equation must be presented : Number of combinations = 2n , where n is number of inputs The truth table for a particular circuit explains how the circuit behaves under normal condition. In this lab experiment, the five (5) logic gates had covered like NOT gate, AND gate, OR gate, NAND gate, NOR gate. You should recall that the logic levels either 0 or 1 have voltage assignment. For TTL circuits, a logic 0 can be anywhere from 0V to +0.8V and logic 1 is in the range of +2.0V to +5.0V.

2|Page m.rizal@unimap.edu.my

3.1 NOT Operation The NOT operation consist of:

(a) Truth table, (b) symbol and (c) sample waveform for the NOT circuit.

3.2 AND Operation The AND operation AND Operation = Produces HIGH (1) output when all input are HIGH

(a) Truth table and (b) circuit symbol for a two input AND gate are shown.

3.3 OR Operation The OR Operation Produces HIGH ouput when one or more inputs are HIGH

(a) Truth table and (b) circuit symbol for a two input OR gate

3|Page m.rizal@unimap.edu.my

PROCEDURE

PART 1: Combinational Logic Gate (1)

A B

X1

X2

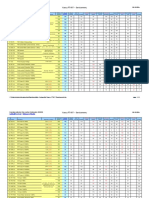

Figure 3.1 : Combinational Logic circuit (TASK1) 1) The Figure 3.1 is shown an example of combinational logic, draw the schematic diagram for the circuit. 2) Draw the for wiring connection by using Logic ICs (74XX04, 74XX08, 74XX32, 74XXXX) and others component (SPDT switches, resistor, LED etc) . 3) Construct the circuit based on Procedure (2). 4) Verify the operation by completing the truth table in Table 3.1. 5) Demo the result to Instructor. Table 3.1 : Truth Table (TASK1) Input A B 0 0 0 1 1 0 1 1 Theory Result X1 X2 Y Experiment Result X1 X2 Y

4|Page m.rizal@unimap.edu.my

PART 2: Combinational Logic Gate (2)

A B C

X1 X2 Y X3

Figure 3.2 : Combinational Logic circuit (TASK2)

1) The Figure 3.2 is shown an example of combinational logic, draw the schematic diagram for the circuit. 2) Draw the for wiring connection by using Logic ICs (74XX04, 74XX08, 74XX11, 74XX27) and others component (SPDT switches, resistor, LED etc) . 3) Construct the circuit based on Procedure (2). 4) Verify the operation by completing the truth table in Table 3.2. 5) Demo the result to Instructor.

Table 3.2 : Truth Table (TASK2) Input B 0 0 1 1 0 0 1 1 Theory Result X2 X3 Experiment Result X2 X3 Y

A 0 0 0 0 1 1 1 1

C 0 1 0 1 0 1 0 1

X1

X1

5|Page m.rizal@unimap.edu.my

LAB 3: LOGIC GATE APPLICATION (RESULT) NAME MATRIC NO NO.PC/TABLE : : :

PART 1: Combinational Logic Gate (1)

Table 3.1 : Truth Table (TASK1) Input A B 0 0 0 1 1 0 1 1 Theory Result X1 X2 Y Experiment Result X1 X2 Y

PART 2: Combinational Logic Gate (2)

Table 3.2 : Truth Table (TASK2) Input B 0 0 1 1 0 0 1 1 Theory Result X2 X3 Experiment Result X1 X2 X3 Y

A 0 0 0 0 1 1 1 1

C 0 1 0 1 0 1 0 1

X1

6|Page m.rizal@unimap.edu.my

Vous aimerez peut-être aussi

- Lab 1: Introduction To Combinational Design: EquipmentsDocument42 pagesLab 1: Introduction To Combinational Design: EquipmentsnarpatzaPas encore d'évaluation

- Medi-Caps University: Digital ElectronicsDocument54 pagesMedi-Caps University: Digital ElectronicsHarsh KumarPas encore d'évaluation

- Introduction To Logic Gates: 3.2 ObjectivesDocument4 pagesIntroduction To Logic Gates: 3.2 ObjectivesnarpatzaPas encore d'évaluation

- DLD Lab 02 - Basic Logic Gates - V3Document16 pagesDLD Lab 02 - Basic Logic Gates - V3Hamna MansoorPas encore d'évaluation

- DEL Lab ManualDocument68 pagesDEL Lab ManualMohini AvatadePas encore d'évaluation

- EP Manual Master Final 28-01-10 New1Document97 pagesEP Manual Master Final 28-01-10 New1jiyadarjiPas encore d'évaluation

- De - Lab ExperimentsDocument62 pagesDe - Lab ExperimentssaipraneethpPas encore d'évaluation

- Lab Manual ElectronicsDocument57 pagesLab Manual ElectronicsNaveen Rockzz Bhavans100% (2)

- Lab Manual - 32050502 - Digital ElectronicsDocument31 pagesLab Manual - 32050502 - Digital ElectronicsFoad alzhraniPas encore d'évaluation

- De Lab Manual 21-22Document46 pagesDe Lab Manual 21-22AUTHOR SOULPas encore d'évaluation

- Tut - Digital IntegratedDocument32 pagesTut - Digital IntegratedqawaPas encore d'évaluation

- DLC Lab 01Document6 pagesDLC Lab 01Azrin ZibatPas encore d'évaluation

- ECE 1250 Lab 6: Overview: in Lab 3 You WillDocument8 pagesECE 1250 Lab 6: Overview: in Lab 3 You WillXuPas encore d'évaluation

- Digital Lab Manual 2023Document168 pagesDigital Lab Manual 2023isaacrajab17Pas encore d'évaluation

- Laboratory Exercise 2: Basic Logic GatesDocument5 pagesLaboratory Exercise 2: Basic Logic GatesSantiago EspitiaPas encore d'évaluation

- DCS Lab-1Document53 pagesDCS Lab-1national printersPas encore d'évaluation

- Laboratory Exercise 2 PDFDocument5 pagesLaboratory Exercise 2 PDFCristian Felipe Rangel TrianaPas encore d'évaluation

- RTL NotDocument9 pagesRTL Notمعتصم الكاملPas encore d'évaluation

- Lab 10 Mux & DeMuxDocument9 pagesLab 10 Mux & DeMuxsafdarmunir070Pas encore d'évaluation

- Practical DTDocument19 pagesPractical DTKundan BhartiPas encore d'évaluation

- Unit 2 - Logic Gate Devices Characteristics (DBV30023)Document68 pagesUnit 2 - Logic Gate Devices Characteristics (DBV30023)Abd Kadir JailaniPas encore d'évaluation

- RDL And& or GateDocument9 pagesRDL And& or Gateمعتصم الكاملPas encore d'évaluation

- Y-0020-01 Basic Level Digital Electronics PDFDocument86 pagesY-0020-01 Basic Level Digital Electronics PDFAkah PreciousPas encore d'évaluation

- Exp. No. 9 Logic Gates: Aim of Experiment: Study The Electronics Circuit Which Operate As ADocument5 pagesExp. No. 9 Logic Gates: Aim of Experiment: Study The Electronics Circuit Which Operate As Asemsem230Pas encore d'évaluation

- DLD Lab # 1 Report-SampleDocument14 pagesDLD Lab # 1 Report-Samplebiologistusama1234Pas encore d'évaluation

- Digital Circuits and Systems Lab Manual For Iii Year/ V Semester B.Tech (Ee) LAB CODE (EE-306)Document55 pagesDigital Circuits and Systems Lab Manual For Iii Year/ V Semester B.Tech (Ee) LAB CODE (EE-306)NATIONAL XEROXPas encore d'évaluation

- Laboratory Exercise 2Document5 pagesLaboratory Exercise 2BriNyanPas encore d'évaluation

- EP Manual Master Final 31-01-11Document102 pagesEP Manual Master Final 31-01-11birenPas encore d'évaluation

- Logic Lab 1 - Digital Abstraction (5 Gates)Document16 pagesLogic Lab 1 - Digital Abstraction (5 Gates)ram010Pas encore d'évaluation

- Experiment ManualDocument50 pagesExperiment ManualSanji Daruma50% (6)

- DD Lab Manual New PDFDocument44 pagesDD Lab Manual New PDFsuyogshahPas encore d'évaluation

- Digital Logic Design Lab ManualDocument55 pagesDigital Logic Design Lab ManualEngr Zaryab WarraichPas encore d'évaluation

- Logic GatesDocument21 pagesLogic GatesAditya ParmarPas encore d'évaluation

- Logic Gate Circuits (Various Logic Families)Document10 pagesLogic Gate Circuits (Various Logic Families)mmaherPas encore d'évaluation

- Experiment3 HAMZADocument14 pagesExperiment3 HAMZAhamzasamara80Pas encore d'évaluation

- Kalai Mohan Lab ManualDocument35 pagesKalai Mohan Lab Manualrskumar.eePas encore d'évaluation

- VTU LD Lab ManualDocument5 pagesVTU LD Lab ManualManjesh ShettyPas encore d'évaluation

- Assignment 1Document12 pagesAssignment 1abuzarkazmi779Pas encore d'évaluation

- Digital Electronics LabDocument34 pagesDigital Electronics LabJuno Hera Magallanes Huyan100% (1)

- Lab Manual 8085 MicroprocessorDocument43 pagesLab Manual 8085 MicroprocessorManvendra Singh0% (1)

- STLD Lab Manual r20 RegulationDocument42 pagesSTLD Lab Manual r20 RegulationsaikiranPas encore d'évaluation

- UEEA/UEEP 1323 Digital Electronics: Power Supply IC TesterDocument12 pagesUEEA/UEEP 1323 Digital Electronics: Power Supply IC TesterKiritoPas encore d'évaluation

- Experiment - 1Document7 pagesExperiment - 1mainlu897Pas encore d'évaluation

- Practice4 (Adder & SustractorDocument7 pagesPractice4 (Adder & SustractorManolo-Hues Diaz SPas encore d'évaluation

- Introduction To Logic Gates Exp2Document11 pagesIntroduction To Logic Gates Exp2Tamim APas encore d'évaluation

- Design of 8 Bit Alu Using Microwind 3.1Document6 pagesDesign of 8 Bit Alu Using Microwind 3.1ijaert100% (1)

- DE Practical FileDocument91 pagesDE Practical File2K17CO13 ABHISHEK JAYANTPas encore d'évaluation

- Lab Manual Logic Design 1-2Document23 pagesLab Manual Logic Design 1-2akahPas encore d'évaluation

- Introduction To Logic Design Lab: And, Or, Not Nand and Nor GatesDocument5 pagesIntroduction To Logic Design Lab: And, Or, Not Nand and Nor GatesErnest Omorose OsemwegiePas encore d'évaluation

- Phy OR-GATE ProjectDocument9 pagesPhy OR-GATE ProjectAwesom Ask50% (2)

- Laboratory Exercise 5Document7 pagesLaboratory Exercise 5Sebastian MoraPas encore d'évaluation

- Automation1 DS1Document7 pagesAutomation1 DS1Ajay AJPas encore d'évaluation

- DLD Lab Manual 01Document6 pagesDLD Lab Manual 01Sana gullPas encore d'évaluation

- Experiment 3 Exclusive - or and Exclusive - Nor Gates: Holy Angel University College of Engineering and ArchitectureDocument12 pagesExperiment 3 Exclusive - or and Exclusive - Nor Gates: Holy Angel University College of Engineering and ArchitectureIan Mark Cayanan GomezPas encore d'évaluation

- EXPERIMENT 1to2 - IDSDocument31 pagesEXPERIMENT 1to2 - IDSManish KumarPas encore d'évaluation

- 10CS33 Logic Design NotesDocument14 pages10CS33 Logic Design Notesjgssb85Pas encore d'évaluation

- Microprocessor System Design: A Practical IntroductionD'EverandMicroprocessor System Design: A Practical IntroductionPas encore d'évaluation

- Applied Electronics Textbook SampleDocument20 pagesApplied Electronics Textbook SampleParth KothekarPas encore d'évaluation

- B07S (E) 411/B07S411K / B07S401K Instrunction Sheet: (1) PrefaceDocument8 pagesB07S (E) 411/B07S411K / B07S401K Instrunction Sheet: (1) PrefaceМихаил БорозанPas encore d'évaluation

- External InterruptDocument4 pagesExternal Interruptsiva kumaarPas encore d'évaluation

- Fireclass Addressable Fire Alarm Control Panels: Firmware Version 25Document24 pagesFireclass Addressable Fire Alarm Control Panels: Firmware Version 25Aleksandr GolosovPas encore d'évaluation

- DS350 Error CodesDocument12 pagesDS350 Error Codesefrain revillaPas encore d'évaluation

- Interfacing Processor To NAND Flash MemoriesDocument11 pagesInterfacing Processor To NAND Flash Memoriesapi-3802214Pas encore d'évaluation

- Battery ChargerDocument43 pagesBattery ChargerAhmed SheirPas encore d'évaluation

- Arduino OscilloscopeDocument4 pagesArduino OscilloscopeRodolfoPerezEscalonaPas encore d'évaluation

- RF Lab Report 1Document19 pagesRF Lab Report 1Nguyễn ThắngPas encore d'évaluation

- 2SC9012 PromaxJohntonDocument3 pages2SC9012 PromaxJohntonsenel1020% (1)

- Datasheeet Yd2030Document4 pagesDatasheeet Yd2030dinnhowPas encore d'évaluation

- FT-817 Softw Adjustment Menu Tabela Com Valores DefaultDocument6 pagesFT-817 Softw Adjustment Menu Tabela Com Valores DefaultDaniel CoslovskyPas encore d'évaluation

- Essential & Practical Circuit AnalysisDocument34 pagesEssential & Practical Circuit AnalysisSubhajit SenguptaPas encore d'évaluation

- RectifierDocument5 pagesRectifierpreethiPas encore d'évaluation

- Exemplo de Artigo JMOEDocument13 pagesExemplo de Artigo JMOElemuelPas encore d'évaluation

- Multiplexing: 8.1 Review QuestionsDocument4 pagesMultiplexing: 8.1 Review QuestionsOso PolPas encore d'évaluation

- Parts and Function of A Computer: Name: Anjo Blancada ACT 1-ADocument5 pagesParts and Function of A Computer: Name: Anjo Blancada ACT 1-AJay Mark BlancadaPas encore d'évaluation

- Commodore Component Catalog 1981Document194 pagesCommodore Component Catalog 1981Dave0% (1)

- File ListDocument16 pagesFile Listpvs12684Pas encore d'évaluation

- System Noise Temperature, C/N / and G/T Ratio - PN: KTSBDocument11 pagesSystem Noise Temperature, C/N / and G/T Ratio - PN: KTSBErik JhonsonPas encore d'évaluation

- M O D E L 1 2 0 7 B: Microprocessor Motor Speed ControllersDocument2 pagesM O D E L 1 2 0 7 B: Microprocessor Motor Speed ControllersCristian TeodorescuPas encore d'évaluation

- Le 37 M 87 BDXDocument143 pagesLe 37 M 87 BDXJoão Pedro AlmeidaPas encore d'évaluation

- Kuman K1Arduino KIT TutorialsDocument140 pagesKuman K1Arduino KIT TutorialsMister123456100% (1)

- Psu ServidoresDocument13 pagesPsu ServidoresPaolo SarachoPas encore d'évaluation

- T'DJ 609015deh 65FDocument1 pageT'DJ 609015deh 65Fzeb066Pas encore d'évaluation

- Service Manual: CX-JT8Document90 pagesService Manual: CX-JT8Luis BagarelliPas encore d'évaluation

- Wiley - Wireless Power Transfer - Principles and ApplicationsDocument2 pagesWiley - Wireless Power Transfer - Principles and ApplicationstigrePas encore d'évaluation

- Format of Mini Project ReportDocument36 pagesFormat of Mini Project ReporthelloPas encore d'évaluation

- USB 2.0 Board Design and Layout Guidelines: Application ReportDocument11 pagesUSB 2.0 Board Design and Layout Guidelines: Application Reportkarim salimiPas encore d'évaluation