Académique Documents

Professionnel Documents

Culture Documents

Analysis On Output LC Filter of PWM Inverter

Transféré par

Kiran KumarDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Analysis On Output LC Filter of PWM Inverter

Transféré par

Kiran KumarDroits d'auteur :

Formats disponibles

G G

Abstract-The cutoff frequency of output LC filters of PWM

inverters limits the control bandwidth of the converter system

while it attenuates voltage ripples caused from the inverter

switching. For a selected cutoff frequency of an output LC filter,

infinite number of L-C combinations is possible. This paper

analyses the characteristics of output LC filters for PWM

inverters in the view of L-C combinations. Practical circuit

conditions such as no-loads, full resistive-loads, and inductive-

loads are considered in the analysis. This paper proposes a

design criterion and a design example for the L-C filter

combination considering both the control performance and the

size of PWM inverters. An experimental PWM inverter system

based on the proposed output LC filter design guideline is built

and tested.

Key words: PWM inverter, output LC filter, cut-off

frequency, L-C combination, inverter size.

I. INTRODUCTION

PWM inverters are widely used in modern power

electronics, such as adjustable speed drives (ASD), active

power filters (APF), dynamic voltage restorers (DVR), or

uninterruptible power supplies (UPS), etc.

Passive LC filters are commonly used on ac terminals of

PWM inverters when the output voltages of inverter systems

are main control target. The main purpose of the output LC

filter is attenuating voltage ripples came from the inverter

switching. The attenuation effect can be increased by

decreasing the filter cut-off frequency against the switching

frequency of inverters according to -40log(f

sw

/f

cutoff

).

However, the control bandwidth of inverter systems is

limited by the filter cut-off frequency [1]. Increasing the

control bandwidth is important not only for a fast operation

of inverter systems but also for exact voltage compensation

without phase delay [2][3][4]. Thus, there is a trade-off

between the attenuation effect and the control band width in

LC filter design.

Besides after deciding the filter cut-off frequency on LC

filters, two more problems may occur. One problem is

voltage oscillations. Very large voltage over shoot may

occur at the filter capacitor when inverters respond to almost

step manner at transient state. The voltage over shoot can be

damped out by generating a damping voltage that is

negatively proportional to the filter capacitor current [1][5].

This is called active damping.

The other problem is large amount of transient current

that flows through the inverter ac terminals when inverters

must generate a quite large amount of voltages suddenly.

When the transient current goes over certain limitation, the

control system should decrease the current by reducing the

inverter voltage instantly. Otherwise, the inverter system

may be tripped by over current fault.

However, when the inverter voltage is instantly reduced

by the current protection, the active damping may not work

properly so that the output voltage may severely oscillate in

the transient state. This problem may be solved by over

sizing the inverter, which inevitably results in cost issues.

This paper proposes LC filter design guideline that

minimizes the transient over current without loss of active

damping performance of inverter systems.

There are infinite combinations of filter inductance and

filter capacitance for a given filter cutoff frequency.

Intuitively, the transient current of a PWM inverter may be

decreased when the filter inductance increases. However, the

output ac voltages become more sensitive on the load

current disturbance because of comparatively small value of

the filter capacitance. Moreover, large filter inductors not

only increase the cost and weight of the output filters but

also increase voltage stress on the inverter switches, since

the voltage drop of the inductor results in the loss of inverter

output voltage.

This paper analyses the characteristics of output LC filters

for PWM inverters in the view of the L-C combinations.

Practical circuit conditions such as no-loads, full resistive-

loads, and inductive-loads are considered in the analysis.

Based on the analysis, a novel filter design guideline that

guarantees good control dynamics with a minimum inverter

size is proposed. Proposed theory is verified by an

experimental set up.

II. ANALYSIS ON PWM INVERTER SYSTEM

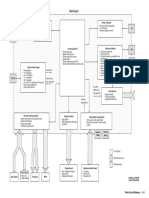

The single phase equivalent circuit of inverter systems

can be described by Fig.1. In Fig. 1, V

INV

is the inverter

output voltage, L

f

is the filter inductor, C

f

is the filter

capacitor, and R

f

is the series equivalent resistance existed

in the filter inductor and inverter switches.

Fig.2 shows a single phase equivalent circuit for a

properly controlled PWM inverter system. The output

regulating voltage V

Com

regulates the ac terminal voltage of

Analysis on Output LC Filters for PWM Inverters

Hyosung Kim

School of EE & Control Engineering

Kongju National University, Korea

hyoskim@kongju.ac.kr

Seung-Ki Sul

School of Electrical Engineering

Seoul National University, Korea

sulsk@plaza.snu.ac.kr

98!+?++3909$?.00 ?009 Tlll TllMC?009 384

G G

a PWM inverter to a reference voltage. The oscillation

damping voltage V

Damp

damps out the overshoot of the

output voltage. The disturbance rejection voltage V

Disturb

suppresses the voltage disturbance occurred from load

current. If the PWM inverter system is controlled properly,

then the three controlled voltages can be generated by the

inverter controller as follows.

A. Output Regulating Voltage

The output regulating voltage V

Com

regulates the output

terminal voltage of a PWM inverter system. When the

oscillation damping voltage V

Damp

and the disturbance

rejection voltage V

Disturb

are ideally controlled, then the load

current disturbance may be completely decoupled and the

system damping factor becomes unity so that the output LC

filter acts just as a time delay component with a delay time

of 2/

f

in the steady state.

Thus the instantaneous load voltage

Load

V can be

regulated exactly to the reference load voltage

*

Load

V when

the time delay is pre-compensated by (1) in the steady state.

*

2

(1 )

Com Load

f

V s V

= + . (1)

where,

1

f

f f

L C

= : filter cut-off frequency.

B. Oscillation Damping Voltage

The damping coefficient can be increased electronically

by generating the oscillation damping voltage V

Damp

as (2).

Damp Damp Inv f Inv

V K i aR i = = . (2)

According to (2), V

Damp

is proportional to the inverter

current with negative coefficient

Damp

K =

f

aR . Thus, the

oscillation damping voltage V

Damp

acts as a series resistance

adding to the

f

R which results in a total equivalent

resistance of (1 )

f

a R + in series to the filter inductor

f

L .

Thus, the effective system damping factor

c

can be

increased as (3).

(1 )

2

(1 )

f f

c

f

f

R C

a

L

a

= +

= +

(3)

Therefore, the control gain of the oscillation damping

voltage

Damp f

K aR = to achieve desired damping factor is

determined by (4).

2

f

Damp f f c

f

L

K aR R

C

= = . (4)

C. Disturbance Rejection Voltage

Since the oscillation damping voltage V

Damp

affects to

increase the equivalent series resistance of the PWM

inverter ac terminal, the output load voltage may be deviated

from the output regulating voltage V

Com

by the load current.

The magnitude of the load voltage decreases and the phase

of the load voltage shifts from the output regulating voltage

V

Com

when the load is reactive. When the load current is

non-sinusoidal, the output load voltage may be further

distorted by the voltage drop across the equivalent series

resistance (1 )

f

a R + and the filter inductance

f

L . The

disturbance rejection voltage V

Disturb

should be generated by

(5) to get rid of the voltage distortion due to the load current

disturbance.

(1 )

Disturb f f Load

V a R sL i = + +

. (5)

D. Equivalent Voltage Drop

Fig. 3 Single phase equivalent circuit of PWM inverter system represented

by two controlled voltage sources.

ZLoad

VInv

pp

pj

ILoad

VLoad

R

f

L

f

C

f

R

T

R

T

VC

R

T

Fig. 1 Single phase equivalent circuit of PWM inverter system.

Fig. 2 Single phase equivalent circuit of properly controlled inverter

system.

385

G G

The total voltage drop, occurred from the oscillation

damping voltage V

Damp

and the disturbance rejection voltage

V

Disturb

, can be calculated by (6).

( ) ( )

(1 ) ( )

(1 )

Drop f f Inv Damp Disturb

f f Inv Load

f f Cap

V R sL i V V

a R sL i i

a R sL i

= + +

= + +

= + +

. (6)

Here, the equivalent voltage drop

Drop

V of a properly

controlled PWM inverter system is only determined by the

filter capacitor current. Thus the single phase equivalent

circuit of the PWM inverter system shown in Fig.2 can be

simplified by Fig.3. Here,

f

sL can be neglected since

(1 )

f f

a R sL + >> , where

f

< in most practical cases.

The equivalent voltage drop

Drop

V causes an error to the

reference load voltage.

III. ANALYSIS ON OUTPUT LC FILTER

The peak value of inverter output current is important

factor in designing the inverter size. The inverter current

rating is normally determined by the filter impedance and

the load impedance in the steady state. However, in the

transient state where the inverter should synthesize output

voltage rapidly, the instantaneous inverter current may

exceed the rated peak value because of the LC filter circuit.

When the transient current of a PWM inverter goes over

the rated peak value, it must be limited by adjusting the

inverter output voltage to protect inverter itself from over

current fault. In this case, the control dynamics of the output

voltage is badly affected by the transient current.

Conventionally, this transient current problem was

compensated by over sizing the inverters. This paper

proposes design guideline of LC output filters that do not

generate the transient current problem without increasing the

inverter size.

A. Equivalent Circuit With No Load

Fig.4 shows a simplified equivalent circuit of a PWM

inverter system without a load. In worst case, the reference

load voltage V

Load

*

is commanded by the peak value of

2V , where V is the rated rms voltage. Since major

problems occur in very short time, this paper focuses on the

transient state analysis for the inverter system. Thus the

reference load voltage V

Load

*

can be regarded as dc value

during the transient state. In the figure, aR

f

is the equivalent

resistance by the oscillation damping control V

Damp

. Various

voltage control methods for compensating the time delay of

the output LC filters have been exploited since the phase

delay compensation described by (1) based on a lead-lag

controller no more works in the transient state. However,

this paper uses a simple feed forward controller for the

output voltage regulation, ie. V

Load

*

= V

Com

= 2V for a

simplicity, since developing the output voltage controller

itself is not the scope of this paper.

The inverter current can be calculated by (7).

2

2

1

1

2

sin( )

f f c

f

INV f c

c

t C V

i t e

= . (7)

The inverter current described by (7) has maximum

value when time reaches to (8).

1

2

1

cos

c

m

f c

t

= . (8)

Thus maximum inverter current can be calculated by (9).

1 2

cos /( 1 / )

2

f

c c c

INVMax

f

C

I V

L

e

=

(9)

Since 2

INVMax

I I < where I = V/Z

Load

, the proportion

between the filter inductance and the filter capacitance

should be limited by (10).

1 2

cos /( 1 / ) f

c c c c

Load Load

f

L

Z Z

C

e e

>

. (10)

B. Equivalent Circuit With Full Load

Although the output LC filters are a main cause to the

inverter current stress in the transient state, load current also

adds the current stress during the transient state. When the

2V

Fig. 4 Simplified equivalent circuit of PWM inverter system without load.

2V

Fig. 5 Simplified equivalent circuit of PWM inverter system with full load.

386

G G

load is inductive, the effect of the load current to the inverter

transient current is not so significant since it increases

smoothly after load terminal voltage is established. However

when the load is purely resistive, the load current can not be

neglected, since it increases sharply proportional to the

established load voltage.

The equivalent circuit of the PWM inverter system with a

full load can be described by Fig.5 since inverter output

current

Inv

I is a sum of the filter capacitor current

Cap

I and

the load current

Load

I . Here, the oscillation damping

voltage V

Damp

and the disturbance rejection voltage V

Disturb

are assumed to be ideally controlled. In worst case, the

reference load voltage with the magnitude of

*

2V

Load

V =

is suddenly commanded to the PWM inverter system at time

t=0. Worst case can also occurs when the load impedance is

purely resistive Z

Load

=R

Load

.

When the output regulating voltage V

Com

is exactly

regulated to the reference load voltage V

Load

*

by a normal

feed forward controller, then the load voltage becomes like

(11).

( )

2

*

2 2

2

2 2

2

2

2

f

Load Load

c f f

f

c f f

s s

V V

s s

V

s

=

+ +

=

+ +

. (11)

Thus the filter capacitor current

Cap

I and the load current

Load

I can be calculated by (12) and (13) respectively.

2

2 2

2

2

f f

Cap f Load

c f f

C

sC V

s s

V

I

+

= =

+

, (12)

( )

2

*

2 2

2

2

f

Load

Load

Load Load c f f

V V

I

Z R s s s

= =

+ +

. (13)

When the filter ratio is chosen as / / 2

f f Load c

L C R =

that is a critical value when (1 )

Load f

R a R = + , the filter

capacitor current can be described by (14).

2 2

2

2

2

Load

c f

Cap

c f f

V

R

I

s s

=

+ +

. (14)

Then the inverter output current ( )

Inv

t i in time domain

can be calculated by the sum of the filter capacitance current

( )

Cap

i t and the load current ( )

Load

i t as (15).

( )

Inv Cap Load

t i i i = +

( )

1

2

1

2

1

2

sin cos 1

Load

f c

c f

t

c

c

V

R

t

e

= +

(15)

Since the inverter current reaches to a maximum value at

1

2

1 ) 2 cos ( /

f c m c

t

= , the maximum inverter current

can be calculated by (16).

1

2

1

2

cos

1

Load

c

c

InvMax c

V

R

I

e

+

. (16)

When the filter ratio is set twice to the critical ratio

as / /

f f Load c

L C R = , the maximum inverter current can

be calculated by (17).

2

1

2

1

2

2

1

cos

1 1

c

Load

InvMax

c

c

R

V

I e

=

. (17)

Fig.6 shows the inverter current overshoot calculated by

(16) and (17) depending on the filter ratio when the system

damping factor ranges from 0.5 to 0.9. When the filter ratio

is set to the critical value, the inverter current overshoot

decreases according to the system damping factor while it is

always higher than 1.15. When the filter ratio is set two

times to the critical value, the inverter current overshoot is

always less than 1.0.

Thus in pure resistive loads, the filter ratio may be set to

/ /

f f Load c

L C R < to maintain the inverter output current

under the rated peak value in the transient state. When the

load is highly inductive, the filter ratio can be decreased to

(10). The lower filter ratio is better since large filter

inductors result to load current disturbance, cost and weight

issues of the output filters, and voltage stress on the inverter.

Fig. 6 Inverter Current Overshoot Depending On Filter Ratio.

387

G G

Therefore, this paper proposes a filter design guide line in

deciding the filter ratio as (18).

c

f

Load Load

c f

L

Z Z

C

e

, (18)

where, upper bound is for purely resistive full load,

lower bound is for no load, and

middle region is for inductive loads or partial loads.

IV. EXPERIMENTAL RESULT

Fig.7 shows the experimental set up to verify the

proposed design criterion on the output LC filter. The

experiment is performed for a single phase inverter module.

Experimental conditions are shown in Table I. A sinusoidal

reference load voltage is applied when its magnitude is the

maximum value of 120V. The inverter is composed of 4

IGBT switches with the switching frequency of 10 kHz. The

sampling time of digital control system is 10 kHz, which is

based on a TMS320VC33/150MHz processor.

TABLE I EXPERIMENTAL CONDITIONS

VCMAX 120V

ZLoad 5 resistive

Fsw 10kHz

Fc 840Hz

Since the filter cutoff frequency is set to 840Hz as given

by Table I, the control bandwidth of the proposed controller

can be reached to 840Hz and the PWM inverter system can

synthesize voltage harmonics up to the 13

TH

order. Further,

the harmonic attenuation at the switching frequency is about

-43dB so that only 0.7% of the voltage ripple due to the

inverter switching remains in the output load voltage as a

noise. Generally, the combinations of filter inductor and

filter capacitor for a given filter cut off frequency are infinite.

However, since the load is pure resistive, the combination of

filter inductor and filter capacitor can be uniquely decided

based on the proposed design criterion as Table II by the

upper bound of (18).

TABLE II. DESIGNED FILTER INDUCTOR AND CAPACITOR

fc 840Hz

Lf 900H

Cf 40F

Fig.8 shows the experimental waveforms of the transient

response where system damping factor is set to 0.5 and the

load is pure resistive. Fig.8a) is the waveforms when the

combination of filter inductor and filter capacitor was

designed /

f f Load

L C Z = according to (18). While the

load current settles into around 21.6 A, the inverter current

overshoots around 24A in its center value, which means the

inverter current goes over 1.1 times to the rated peak current.

Considering normal safety factors on IGBT switches this

over current is not matter.

f

L

f

C

Fig. 7 Experimental set up.

a)

b)

Fig. 8 Experimental waveforms when the sampling time and the

PWM switching frequency is 10kHz, system damping

factor is 0.5, and the load is pure resistive (horizontal axis:

0.2ms/div, vertical axis: 4.00A/div or 30.0V/div); a) when

/

f f Load

L C Z = , b) when / / 4

f f Load

L C Z = .

388

G G

Fig.8b) is the waveforms when the combination of filter

inductor and filter capacitor was adjusted to

/ / 4

f f Load

L C Z = by replacing the load resistor with 20

that is four times larger than that of Fig.8a). While the load

current settles into around 4A, the inverter current overshoot

reaches up to around 19A in its center value, which means

the inverter current goes over 4.75 times to the rated peak

current. This over current will conflict with typical safety

factors on IGBT switches. The output load voltage v

Cap

also

shows some oscillatory behavior.

Fig.9 shows the experimental waveforms for the steady

state response of the proposed inverter system with the same

filters as in Fig.8. The peak value of the inverter ripple

current in steady state goes around 1.2 times to the rated

peak value in Fig.9a) where the combination of filter

inductor and filter capacitor was designed /

f f Load

L C Z = .

While it goes around 1.8 times to the rated peak value in

Fig.9b) where the combination of filter inductor and filter

capacitor was designed / / 4

f f Load

L C Z = . This may also

conflict with the current specification on the inverter

switches.

V. CONCLUSION

This paper has discussed on output filter design

considering both the control dynamics and the inverter size

of PWM inverter systems. While the cut off frequency of

output LC filters limits theoretical control bandwidth, it

attenuates the switching ripples that appear in the output

voltages of PWM inverters. Although there are infinite

combinations of filter inductor and filter capacitor for a

given filter cutoff frequency, no analytical design method

was presented before. This paper analyzed the relation

among the output LC filter, PWM inverter, and controller in

inverter systems to provide a design criterion for the output

LC filters which does not give over current stress to the

inverter switches nor degraded control performance to the

PWM inverter system. Experimental results have verified

that the proposed output LC filter ensures optimal inverter

size and good control dynamics of PWM inverter systems.

ACKNOWLEDGMENT

This work was supported partly by the fund of the Korea

Research Foundation.

REFERENCES

[1] S.J. Lee, H. Kim, S.K. Sul, A Novel Control Method for The

Compensation Voltages in Dynamic Voltage Restorers, Conference

Records on APEC 2004/ IEEE, CD ROM, Feb. 2004.

[2] T. Kawabata, T. Miyashita, Y. Yamamoto, Digital Control of Three-

Phase PWM Inverter with LC Filter, IEEE Trans. on Power

Electronics, Vol. 6, No. 1, pp.62-72, 1991.

[3] M.J. Newman, D.G. Holmes, J.G. Nielsen, and F. Blaabjerg, A

Dynamic Voltage Restorer (DVR) with Selective Harmonic

Compensation at Medium Voltage Level, Conference Records on

IAS03/IEEE, CD ROM , Oct. 2003.

[4] Y.H. Cho, S.K. Sul, Controller Design for Dynamic Voltage

Restorer with Harmonics Compensation Function, Conference

Records on IAS 2004Annual Meeting/ IEEE, CD ROM, Oct. 2004.

[5] M. J. Ryan, R. D. Lorenz, A High Performance Sine Wave Inverter

Controller with Capacitor Current Feedback and Back-EMF

Decoupling, Conference Records on PESC95/IEEE, pp.507 -513,

1995.

a)

b)

Fig. 9 Experimental waveforms when the sampling time and the

PWM switching frequency is 10kHz, system damping

factor is 0.5, and the load is pure resistive (horizontal axis:

0.2ms/div, vertical axis: 4.00A/div or 30.0V/div); a) when

/

f f Load

L C Z = , b) when / / 4

f f Load

L C Z = .

389

Vous aimerez peut-être aussi

- FAQ - National Certification Examination For Energy Managers and Energy AuditorsDocument4 pagesFAQ - National Certification Examination For Energy Managers and Energy AuditorsKiran KumarPas encore d'évaluation

- Usharama Jntu Kakinada Eee SyllabusDocument85 pagesUsharama Jntu Kakinada Eee SyllabussambhanimadhubabuPas encore d'évaluation

- Barc Dgfs PH.D 2017 AdvtDocument2 pagesBarc Dgfs PH.D 2017 AdvtKiran KumarPas encore d'évaluation

- Lal Bahadur Shastri Institute of Management & TechnologyDocument8 pagesLal Bahadur Shastri Institute of Management & TechnologyKiran KumarPas encore d'évaluation

- Read MeDocument2 pagesRead MeKiran KumarPas encore d'évaluation

- Eastern Power Distribution Company Grid Connectivity GuideDocument6 pagesEastern Power Distribution Company Grid Connectivity GuideKiran KumarPas encore d'évaluation

- CDVDT SolutionDocument6 pagesCDVDT SolutionKiran KumarPas encore d'évaluation

- Read MeDocument2 pagesRead MeKiran KumarPas encore d'évaluation

- 05590043Document8 pages05590043Kiran KumarPas encore d'évaluation

- 5-Representation of Discrete-Time Signals in Transform DomainDocument15 pages5-Representation of Discrete-Time Signals in Transform DomainKiran KumarPas encore d'évaluation

- UPSC Civil Services Preliminary 2011 Syllabus for Aptitude TestDocument2 pagesUPSC Civil Services Preliminary 2011 Syllabus for Aptitude TestChandrashekar VenkategowdaPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5782)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- AD8307Document24 pagesAD8307Filip ZalioPas encore d'évaluation

- Mastering With Acustica 1.4Document125 pagesMastering With Acustica 1.4icanadaaPas encore d'évaluation

- 2c Power Supply (Voltage Regulator)Document14 pages2c Power Supply (Voltage Regulator)Dzul HakimPas encore d'évaluation

- 2 11 PDFDocument19 pages2 11 PDFBOLFRAPas encore d'évaluation

- Creative FX Collection - User Guide - v1.0 PDFDocument65 pagesCreative FX Collection - User Guide - v1.0 PDFAriel AlfonsoPas encore d'évaluation

- Small, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionDocument16 pagesSmall, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionGirish Kumar .R. GowdaPas encore d'évaluation

- LAB - 6 - Passive FiltersDocument10 pagesLAB - 6 - Passive FiltersAhmet ArabPas encore d'évaluation

- 2c Power Supply (Voltage Regulator)Document14 pages2c Power Supply (Voltage Regulator)Dzul HakimPas encore d'évaluation

- Single Chip Low Power RF Transmitter For Narrowband SystemsDocument57 pagesSingle Chip Low Power RF Transmitter For Narrowband SystemsjainatinPas encore d'évaluation

- Thermocouple & transducer time constants, damping ratios, & frequency responsesDocument2 pagesThermocouple & transducer time constants, damping ratios, & frequency responsesBolWolPas encore d'évaluation

- Scattering Parameters and Characteristic Polynomials for Lossless Lumped-Element FiltersDocument23 pagesScattering Parameters and Characteristic Polynomials for Lossless Lumped-Element FiltersJAMILPas encore d'évaluation

- VHF ComDocument21 pagesVHF ComCamilo BlanquivPas encore d'évaluation

- IC 7000 ServiceDocument92 pagesIC 7000 Serviceiz2bktPas encore d'évaluation

- PMX - b3579Document24 pagesPMX - b3579Leandro MoriciPas encore d'évaluation

- SKF Machine Condition Transmitters (MCT) SeriesDocument12 pagesSKF Machine Condition Transmitters (MCT) SeriesIlham Rangkayo SatiPas encore d'évaluation

- Filter TransformationsDocument8 pagesFilter TransformationsWilliam GuarientiPas encore d'évaluation

- AN 1059 High CMR Isolation Amplifier For Current SensingDocument9 pagesAN 1059 High CMR Isolation Amplifier For Current Sensing조용규Pas encore d'évaluation

- Planos Electrónicos Monitor Fetal Corometrics Modelo 170 SeriesDocument88 pagesPlanos Electrónicos Monitor Fetal Corometrics Modelo 170 Seriesviviana vargasPas encore d'évaluation

- JNTUH Syllabus 2013 M.tech Communication SysDocument26 pagesJNTUH Syllabus 2013 M.tech Communication SysSRINIVASA RAO GANTAPas encore d'évaluation

- Emi Design GuideDocument18 pagesEmi Design GuideToufeeqh TouffPas encore d'évaluation

- QR Flyback ConverterDocument27 pagesQR Flyback ConverterAndrea SanninoPas encore d'évaluation

- S I 4 0 1 0 A I M N G: Ntenna Nterface AND Atching Etwork UideDocument36 pagesS I 4 0 1 0 A I M N G: Ntenna Nterface AND Atching Etwork Uidehyu2123Pas encore d'évaluation

- Optimal Planning Large Passive-Harmonic-Filters Set at High Voltage LevelDocument9 pagesOptimal Planning Large Passive-Harmonic-Filters Set at High Voltage LevelAlfredo Lopez CordovaPas encore d'évaluation

- 120 W X 2 Channel Class D Audio Power Amplifier Using IRS20955 and IRF6645Document43 pages120 W X 2 Channel Class D Audio Power Amplifier Using IRS20955 and IRF6645Domingo ArroyoPas encore d'évaluation

- EceDocument444 pagesEceSanthosh RockyPas encore d'évaluation

- 2 Meter SDRDocument9 pages2 Meter SDRusaitc100% (1)

- EC6503-Transmission Lines and WaveguidesDocument15 pagesEC6503-Transmission Lines and WaveguidesAnonymous lt2LFZH100% (1)

- Maintenance Schedule ACS800 2016 and BeforeDocument3 pagesMaintenance Schedule ACS800 2016 and BeforeahilsergeyPas encore d'évaluation

- Presentation of LICA On Filter CircuitsDocument10 pagesPresentation of LICA On Filter CircuitsDev GargPas encore d'évaluation

- PowerDocument21 pagesPowermebrahtenPas encore d'évaluation