Académique Documents

Professionnel Documents

Culture Documents

Funcionamiento ShiftReg 8 Bit

Transféré par

Alejandro Agüera LopezCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Funcionamiento ShiftReg 8 Bit

Transféré par

Alejandro Agüera LopezDroits d'auteur :

Formats disponibles

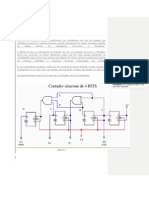

Funcionamiento del Integrado 74HC165

El integrado 74HC165 es un shift register de 8 bits el cual puede ser configurado como un serial-in, serial-out (SISO) o parallel-in, serial-out (PISO). El comportamiento SISO se obtiene cuando las entradas Shift/Load esta en high (equivalente a que el shift register no se encuentre procesando las entradas en paralelo) y el clock enable este en low (equivalente a que el integrado este sincronizado con el reloj); a su vez el comportamiento PISO se logra al tener la entrada Shift/Load en low y el clock enable en high durante el periodo de adquisicin de datos y luego en low durante el proceso de trabajo. Estas disposiciones se detallan a continuacin.

SISO: Esta configuracin se distingue de la PISO al recibir los bits en forma serial. Para ello se debe setear el primer pin (Shift/Load) a un nivel high, con lo cual bloquea cualquier entrada paralelo. Adems su decimo quinto pin correspondiente al clock enable, la seal debe estar seteada en un nivel low, es decir, como dijimos, el integrado est sincronizado con la entrada de reloj. De este modo el integrado estar operando como un shift register serial input serial output. Finalmente el integrado a medida que recibe los bits de informacin, los registrar en su registro de Q1 a Q6 segn el orden de llegada, luego se puede establecer que el atributo de los 8 bits de trabajo del shift register corresponden a el bit en espera a entrar, los 6 bits guardados y el octavo bit que es entregado al detectar un bit que ingresa al circuito.

Figura 2.1.- Diagrama de encapsulado de el integrado 74HC165.

PISO: Este display a diferencia del descrito anteriormente, recibe un nmero binario en forma simultnea para todas sus entradas D0 a D7, esto se da debido a que el clock enable se encuentra con una entrada de nivel high la que en conjunto con el pin Shift/Load en low permite la deteccin de cada entrada, puestas en paralelo. Es importante destacar que en este modo de operacin el integrado es se comporta como un circuito asncrono. Como se puede apreciar en la figura 2.2 una vez que el clock enable comienza a recibir una entrada low, el integrado comienza a depender del clock, dando as lugar a los cambios sincronizados en la salida, la cual adopta de manera secuencial cada valor guardado. Cabe destacar que en este proceso la nica manera de variar el registro del integrado es al encender la entrada que corresponde al clock enable, no se posee un almacenamiento dinmico como en la configuracin SISO.

Figura 2.2.- Diagrama de trabajo de la configuracin PISO.

Referencias : Thomas L. Floyd Fundamentos de Sistemas Digitales, Prentice Hall.

Vous aimerez peut-être aussi

- C Digitales Ii If 3Document17 pagesC Digitales Ii If 3walterPas encore d'évaluation

- Registros de DesplazamientoDocument22 pagesRegistros de Desplazamientomichu4651Pas encore d'évaluation

- Informe PrevioDocument13 pagesInforme PrevioGrecia Melissa Dionicio AntunezPas encore d'évaluation

- C2 ContadoresDocument6 pagesC2 Contadoresbuonarroti17Pas encore d'évaluation

- Registros de CorrimientoDocument7 pagesRegistros de CorrimientoRoberto RobaldinoPas encore d'évaluation

- Circuitos FuncionalesDocument58 pagesCircuitos FuncionalesOrlando Jose HerediaPas encore d'évaluation

- Practica4registro PIPODocument8 pagesPractica4registro PIPOMoises Alejandro Berrios MorenoPas encore d'évaluation

- Práctica 3 VHDLDocument8 pagesPráctica 3 VHDLHoracio Fernández JiménezPas encore d'évaluation

- El Circuito Integrado 74HCTLS192Document6 pagesEl Circuito Integrado 74HCTLS192Blanca TPas encore d'évaluation

- ExpoDocument2 pagesExpoAlyce MaldonadoPas encore d'évaluation

- Controlar Display de 7 Segmentos Con Shift RegisterDocument27 pagesControlar Display de 7 Segmentos Con Shift RegisterPOLLO45100% (1)

- Contador Con HabilitadorDocument10 pagesContador Con HabilitadorcarlosPas encore d'évaluation

- Contador Binario 7493 de 8 BitsDocument6 pagesContador Binario 7493 de 8 BitsSaicker PazPas encore d'évaluation

- Marco Teorico Labo 5Document12 pagesMarco Teorico Labo 5DanteJaraEspinozaPas encore d'évaluation

- Informe Final de Laboratorio 3 SistemasDocument8 pagesInforme Final de Laboratorio 3 SistemasJean Carlos Palomino CondePas encore d'évaluation

- Practica 10Document8 pagesPractica 10Arturo Palacios CalderonPas encore d'évaluation

- Contadores Digitales Con 74193Document61 pagesContadores Digitales Con 74193Saicker Paz100% (1)

- Practica4 Arquitectura Luis ValeroDocument9 pagesPractica4 Arquitectura Luis ValeroAndres FranquizPas encore d'évaluation

- INFORMEDocument18 pagesINFORMEFRANCISCO MOLINAPas encore d'évaluation

- Arquitectura Del Computador Lab 1Document14 pagesArquitectura Del Computador Lab 1Jess Gabriel RojasPas encore d'évaluation

- Ejemplo Contador Del 0 Al 99Document16 pagesEjemplo Contador Del 0 Al 99George MoreloPas encore d'évaluation

- Registros de DesplazamientoDocument28 pagesRegistros de DesplazamientoAnonymous ayB4oYPas encore d'évaluation

- Encoder Lazo CerradoDocument23 pagesEncoder Lazo CerradoRockoPas encore d'évaluation

- Contador ParaleloDocument11 pagesContador ParaleloWilliams Molina EspirituPas encore d'évaluation

- Edison Logacho - Consulta - 4783Document3 pagesEdison Logacho - Consulta - 4783JokerTHPas encore d'évaluation

- Registros de DesplazamientoDocument30 pagesRegistros de Desplazamientoabeat_1100% (2)

- Practica4 Registro MultisimDocument7 pagesPractica4 Registro MultisimMoises Alejandro Berrios MorenoPas encore d'évaluation

- Contadores SíncronosDocument9 pagesContadores SíncronosanderssonPas encore d'évaluation

- REGISTROS DE CORRIMIENTO para Comunicacion Serie - Doc - 1527525162604 PDFDocument5 pagesREGISTROS DE CORRIMIENTO para Comunicacion Serie - Doc - 1527525162604 PDFLeonardo AgüeroPas encore d'évaluation

- Contando Con CircuitosDocument12 pagesContando Con CircuitosPablo Mamani SuycoPas encore d'évaluation

- Contadores Digitales PDFDocument14 pagesContadores Digitales PDFErick Jesús Rodríguez DávilaPas encore d'évaluation

- El Circuito Integrado 74hctls192Document7 pagesEl Circuito Integrado 74hctls192Jimmy SiñaniPas encore d'évaluation

- Contadores SíncronosDocument9 pagesContadores SíncronosAndersson VacaPas encore d'évaluation

- Interrupciones en S7-1200Document7 pagesInterrupciones en S7-1200AslapasPas encore d'évaluation

- Registros. Registro de Corrimiento BásicoDocument6 pagesRegistros. Registro de Corrimiento BásicoHugoDanteGarciaMuñozPas encore d'évaluation

- Contadores SíncronosDocument7 pagesContadores SíncronosCristian Ochoa AriasPas encore d'évaluation

- Disipación de PotenciaDocument11 pagesDisipación de PotenciaBrian AvalosPas encore d'évaluation

- Registro de DesplazamientoDocument9 pagesRegistro de DesplazamientoGabriel MartínezPas encore d'évaluation

- Registros de Corrimiento para Comunicacion SerieDocument5 pagesRegistros de Corrimiento para Comunicacion Serienando3pPas encore d'évaluation

- Registro de Desplazamiento ManyDocument10 pagesRegistro de Desplazamiento Manylus maria ruiz chuquirunaPas encore d'évaluation

- Pic 16 F 877 ADocument7 pagesPic 16 F 877 AXFhernandox ManPas encore d'évaluation

- Ejercicio MultisimDocument7 pagesEjercicio MultisimDavid DelgadoPas encore d'évaluation

- Practica Contador Binario NuevoDocument9 pagesPractica Contador Binario NuevoRominAgPas encore d'évaluation

- Puertos de Entrada y SalidaDocument55 pagesPuertos de Entrada y SalidaJuanfer PCPas encore d'évaluation

- Informe N 2 Terminado de ContadoresDocument13 pagesInforme N 2 Terminado de ContadoresM̶i̶c̶h̶e̶l̶ Mejia100% (2)

- Un Contador Digital de Dos DígitosDocument8 pagesUn Contador Digital de Dos DígitosRuben OmarPas encore d'évaluation

- LAB1 InformeDocument8 pagesLAB1 InformeHector Polanco AlvarezPas encore d'évaluation

- Imforme Previo de RegistrosDocument13 pagesImforme Previo de RegistrosDoming de la CruzPas encore d'évaluation

- CIRCUITOS DIGITALES Semana 10 c5bDocument16 pagesCIRCUITOS DIGITALES Semana 10 c5boliver clemente ramosPas encore d'évaluation

- Toledo Toro Gonzales Practica FinalDocument9 pagesToledo Toro Gonzales Practica FinalLIMBERTOLEDOPas encore d'évaluation

- Analisis de Circuitos Con FF PDFDocument11 pagesAnalisis de Circuitos Con FF PDFArturo YoveraPas encore d'évaluation

- Registro de DesplazamientoDocument6 pagesRegistro de DesplazamientojosegrabandoPas encore d'évaluation

- Como Hacer Un ContadorDocument12 pagesComo Hacer Un ContadorBeastrid Urbaez OvallesPas encore d'évaluation

- Contador Con Flip-FlopDocument19 pagesContador Con Flip-FlopMiguel Angel CasiquePas encore d'évaluation

- Lenguajes de ProgramacionDocument20 pagesLenguajes de ProgramacioncaxchosPas encore d'évaluation

- Entendiendo La Arquitectura 4 BitsDocument17 pagesEntendiendo La Arquitectura 4 BitsoscarPas encore d'évaluation

- Entendiendo La Arquitectura 4 BitsDocument17 pagesEntendiendo La Arquitectura 4 BitsoscarPas encore d'évaluation

- Proyecto 1 AluDocument15 pagesProyecto 1 AluMondatta TerkhataPas encore d'évaluation

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiD'EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiÉvaluation : 5 sur 5 étoiles5/5 (1)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208D'EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Pas encore d'évaluation

- Placement Test - Febrero y Marzo 2024Document3 pagesPlacement Test - Febrero y Marzo 2024xMz 30Pas encore d'évaluation

- Introduction A La Matemática AplicadaDocument6 pagesIntroduction A La Matemática AplicadaRonaldo Andres León ToussaintPas encore d'évaluation

- Coaching Personalizado de Peligros y Riesgos Conasurmin RDocument44 pagesCoaching Personalizado de Peligros y Riesgos Conasurmin RalterPas encore d'évaluation

- Fines TributariosDocument43 pagesFines TributariosCristhian Diego Alvites HuizaPas encore d'évaluation

- Metodología para Un Manifiesto Poético-PolíticoDocument7 pagesMetodología para Un Manifiesto Poético-PolíticoseosoriopPas encore d'évaluation

- M21 U2 A1 Rodr guezHEDocument5 pagesM21 U2 A1 Rodr guezHEMarisol100% (1)

- Test de Fisica Ley de CoulombDocument3 pagesTest de Fisica Ley de CoulombMarcos Yasviel Gómez HernándezPas encore d'évaluation

- El Lenguaje y La Lógica de Las ProposicionesDocument26 pagesEl Lenguaje y La Lógica de Las ProposicionesManuel GomezPas encore d'évaluation

- 8° PER 2° CLASE #2 - El CostumbrismoDocument4 pages8° PER 2° CLASE #2 - El CostumbrismoAndrea Juliana Niño RuedaPas encore d'évaluation

- Formato para Desarrollo de EvidenciaDocument8 pagesFormato para Desarrollo de EvidenciaCamilo enciso coPas encore d'évaluation

- Clase 15Document16 pagesClase 15Jere OlivieriPas encore d'évaluation

- Test de Los 5 Lenguajes Del AmorDocument12 pagesTest de Los 5 Lenguajes Del Amorondina monteroPas encore d'évaluation

- Lista de Precios Mayo 2023 MecanicosDocument3 pagesLista de Precios Mayo 2023 MecanicosTomas Ale75% (4)

- Modelo Canvas LindaDocument6 pagesModelo Canvas LindaDairon villalobos mercadoPas encore d'évaluation

- Analisis Del Codigo de Etica de Psicologos DelDocument22 pagesAnalisis Del Codigo de Etica de Psicologos DelAlexander GallardoPas encore d'évaluation

- Clase 2. Entrevista Inicial Con Los Padres-AberasturyDocument9 pagesClase 2. Entrevista Inicial Con Los Padres-AberasturyMara CovarrubiasPas encore d'évaluation

- Almacenamiento de Productos CongeladosDocument3 pagesAlmacenamiento de Productos CongeladosMónica Del Rio ZuñigaPas encore d'évaluation

- WencdorDocument30 pagesWencdorKevin SilvaPas encore d'évaluation

- Proyecto RSE VyPDocument17 pagesProyecto RSE VyPDavid BaLiPas encore d'évaluation

- Actividad 1 Cuadro ComparativoDocument3 pagesActividad 1 Cuadro ComparativoLauri guerreroPas encore d'évaluation

- Ficha de Sesión SexualidadDocument3 pagesFicha de Sesión SexualidadJulio César Choquecota MamaniPas encore d'évaluation

- Trabajo Final Asignatura DER-104Document2 pagesTrabajo Final Asignatura DER-104elizabeth pujolsPas encore d'évaluation

- Pérdidas V02 1Document36 pagesPérdidas V02 1Miguel Angel Lezama ValdiviaPas encore d'évaluation

- 18 - Técnicas de ModeladoDocument23 pages18 - Técnicas de ModeladoHugoPas encore d'évaluation

- Termodinamica (Toberas)Document13 pagesTermodinamica (Toberas)NAYELY BELLODASPas encore d'évaluation

- Tutorial Diseño MetodologicoDocument10 pagesTutorial Diseño MetodologicoLizethPas encore d'évaluation

- Acto 1° Mayo T.MañanaDocument7 pagesActo 1° Mayo T.MañanaDaniela FernándezPas encore d'évaluation

- Diseño de AlgoritmosDocument181 pagesDiseño de AlgoritmosRafael OviedoPas encore d'évaluation

- Guía LapbookDocument3 pagesGuía LapbookJuana Diaz EspinozaPas encore d'évaluation