Académique Documents

Professionnel Documents

Culture Documents

Computer Architecture Question Anna University

Transféré par

mashaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Computer Architecture Question Anna University

Transféré par

mashaDroits d'auteur :

Formats disponibles

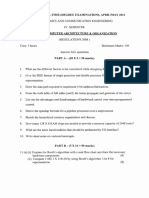

Reg. No.

Question Paper Code:

J7655

M.E./M.Tech. DEGREE EXAMINATION, JUNE 2010 First Semester

Computer Science and Engineering

CS9211 COMPUTER ARCHITECTURE

(Common to M.Tech. Information Technology) (Regulation 2009) Time : Three hours

1. 2. 3. 4. 5. 6. 7. 8. 9. 10.

State the principle of locality and its types.

What are the choices for encoding instruction set? What is speculation? Give an example.

Mention the effects of imperfect alias analysis. What is loop unrolling?

Give the uses of sentinel.

Define multiprocessor cache coherence.

What are the approaches used for multithreading? Which block should be replaced on a cache Miss? How is cache performance improved?

11.

12

0

(a) (i) (ii)

Describe the operations designed for media and signal processing. (10)

Explain the ways in which a computer architect can help the compiler writer. (6) Or

12 0

PART A (10 2 = 20 Marks) PART B (5 16 = 80 Marks)

Answer ALL Questions

12 0

Maximum : 100 Marks

(b)

(i)

(ii)

Describe the addressing modes and instructions designed for control flow. (9)

12.

(a)

Explain the techniques to overcome data hazards with dynamic scheduling. (16) Or

(b) 13. (a)

Describe the limitations of Instruction Level Parallelism. (i) (ii)

Explain the basic VLIW approach used for static multiple issue. (8)

Enumerate the crosscutting issues in hardware and software speculation mechanisms. (8) Or

(ii)

Describe the basic compiler techniques for exposing instruction level parallelism. (8) Describe the design challenges in SMT processors . Discuss the performance of shared memory multiprocessors. Or (8) (8)

14.

(a)

(i) (ii)

(b)

(i)

Explain the synchronization mechanisms designed for large scale multiprocessors. (9) Discuss the details of memory consistency models. (7)

(ii) 15. (a) (i) (ii)

Explain the concept of miss penalty and out of order execution in processors. (6) Discuss the methods of interface between CPU and memory. (10) Or (16)

12

(b)

Discuss in detail the different levels of RAID.

12 0

2

(b)

(i)

Explain the hardware support for exposing more parallelism at compile time. (8)

12 0

(16)

Discuss the instructions.

addressing

modes

used

for

signal

processing (7)

J7655

Vous aimerez peut-être aussi

- CS2354 Advanced Computer Architecture Anna University Question Paper For MEDocument2 pagesCS2354 Advanced Computer Architecture Anna University Question Paper For MEpraveenaprabhuPas encore d'évaluation

- CS9211-Computer Architecture QuestionDocument7 pagesCS9211-Computer Architecture Questionrvsamy80Pas encore d'évaluation

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankaniprahalPas encore d'évaluation

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- EC2303 Computer Architecture and Organization QUESTION PAPERDocument4 pagesEC2303 Computer Architecture and Organization QUESTION PAPERJayagopal JaiPas encore d'évaluation

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzPas encore d'évaluation

- CS 2253 - Computer Organization and Architecture PDFDocument2 pagesCS 2253 - Computer Organization and Architecture PDFvelkarthi92Pas encore d'évaluation

- CS 2354 - Advanced Computer Architecture PDFDocument2 pagesCS 2354 - Advanced Computer Architecture PDFvelkarthi92100% (1)

- CS2253 - Computer Organization and Architecture PDFDocument2 pagesCS2253 - Computer Organization and Architecture PDFvelkarthi92100% (1)

- PART A - (10 × 2 20 Marks)Document2 pagesPART A - (10 × 2 20 Marks)Deepak TirunelveliPas encore d'évaluation

- Anna University QP COADocument3 pagesAnna University QP COAAbirami Satheesh KumarPas encore d'évaluation

- X62303 (CS1251 Cs1202a)Document2 pagesX62303 (CS1251 Cs1202a)tamilarasi87thulasiPas encore d'évaluation

- Answer ALL Questions. PART A - (10 2 20 Marks)Document2 pagesAnswer ALL Questions. PART A - (10 2 20 Marks)Dhanusha Chandrasegar Sabarinath0% (1)

- Question BanksDocument74 pagesQuestion BanksVidhya GanesanPas encore d'évaluation

- Embedded Systems Model Question PaperDocument6 pagesEmbedded Systems Model Question PaperSubramanyaAIyerPas encore d'évaluation

- CS9223 - ADVANCED SYSTEM SOFTWARE Question Paper - Anna UniversityDocument2 pagesCS9223 - ADVANCED SYSTEM SOFTWARE Question Paper - Anna UniversityNithya Preya SreetharanPas encore d'évaluation

- MCS 012Document118 pagesMCS 012SongYak YamPas encore d'évaluation

- DataDocument2 pagesDatamadhes14Pas encore d'évaluation

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.rajkumarsacPas encore d'évaluation

- Es Model QPDocument13 pagesEs Model QPலோகேஷ் கிருஷ்ணமூர்த்திPas encore d'évaluation

- Question Paper CodeDocument2 pagesQuestion Paper CodesaipriyaPas encore d'évaluation

- End Term Examination: Paper Code: BBA - 107 Subject: Computer Fundamentals Paper IDDocument5 pagesEnd Term Examination: Paper Code: BBA - 107 Subject: Computer Fundamentals Paper IDshivscribd1Pas encore d'évaluation

- Question Paper Computer FundamentalsDocument5 pagesQuestion Paper Computer Fundamentalsshivscribd1100% (1)

- WWW - Indiastudents.in: Question Paper CodeDocument2 pagesWWW - Indiastudents.in: Question Paper CodeBehin SamPas encore d'évaluation

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.IT GirlsPas encore d'évaluation

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonPas encore d'évaluation

- NR Set No. 2Document4 pagesNR Set No. 2adddataPas encore d'évaluation

- Ec 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Document2 pagesEc 2303iec 53 - Computer Architecture Organization: B.E.Fb - Tech. Degree Examination, Novemberjdecember 2012Somasundaram RamuPas encore d'évaluation

- Answer ALL Questions: Part A - (10 X 2 20)Document2 pagesAnswer ALL Questions: Part A - (10 X 2 20)BIBIN CHIDAMBARANATHANPas encore d'évaluation

- Embedded System - J7607Document2 pagesEmbedded System - J7607ustadkrishnaPas encore d'évaluation

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviPas encore d'évaluation

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYAPas encore d'évaluation

- Adv. Computer Architecture CS701 - Jan 011Document2 pagesAdv. Computer Architecture CS701 - Jan 011Sachin Kumar GoyelPas encore d'évaluation

- Ca Ap9222 PDFDocument4 pagesCa Ap9222 PDFVenkataLakshmi KrishnasamyPas encore d'évaluation

- Ece-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)Document3 pagesEce-Nd-2021-Ec 8552-Computer Architecture and Organization-807537160-40450 (Ec8552)AwantikPas encore d'évaluation

- B - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012Document2 pagesB - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012krithikgokul selvamPas encore d'évaluation

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptPas encore d'évaluation

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)HOD ECE KNCETPas encore d'évaluation

- Os ND06Document3 pagesOs ND06kevinbtechPas encore d'évaluation

- Jan10 RTSDocument1 pageJan10 RTSSrikanth SridharPas encore d'évaluation

- U 104612Document1 pageU 104612Mohammed Al-nawahPas encore d'évaluation

- MSC IT QuestionsDocument7 pagesMSC IT QuestionsthangaprakashPas encore d'évaluation

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenPas encore d'évaluation

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.saran_neoPas encore d'évaluation

- 07a81901 AdvancedcomputerarchitectureDocument4 pages07a81901 AdvancedcomputerarchitectureSharanya ThirichinapalliPas encore d'évaluation

- CS2253 - Coa - Univ QNSDocument6 pagesCS2253 - Coa - Univ QNSKristyn BlackPas encore d'évaluation

- ArchitectureDocument3 pagesArchitecturesamueljamespeterPas encore d'évaluation

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904Pas encore d'évaluation

- Sastra Deemed University: Ten Ten TenDocument2 pagesSastra Deemed University: Ten Ten TenK SriPas encore d'évaluation

- Question Papers of Two Year M. Tech II Semester Regular Examinations September - 2012Document26 pagesQuestion Papers of Two Year M. Tech II Semester Regular Examinations September - 2012Raja RamPas encore d'évaluation

- WWW - Indiastudents.in: Question Paper CodeDocument2 pagesWWW - Indiastudents.in: Question Paper CodeBehin SamPas encore d'évaluation

- CAO 2018 T3 Question PaperDocument2 pagesCAO 2018 T3 Question Paperharsh guptaPas encore d'évaluation

- Question Bank - M5 To M7Document2 pagesQuestion Bank - M5 To M7Pieter MarkerPas encore d'évaluation

- Lllit5: Embedded System DesignDocument4 pagesLllit5: Embedded System DesignAnonymous 2MwnnyPas encore d'évaluation

- Question Paper For Model Exam Department of Computer Science EngineeringDocument2 pagesQuestion Paper For Model Exam Department of Computer Science EngineeringveerakumarsPas encore d'évaluation

- Testing of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksDocument2 pagesTesting of Vlsi Circuits: Answer All Questions Each Question Carries 25 MarksAnonymous gwdxvOcoqPas encore d'évaluation

- Question PapersDocument4 pagesQuestion Papersமீனா முருகேசன்Pas encore d'évaluation

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemD'EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemPas encore d'évaluation

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesD'EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesPas encore d'évaluation