Académique Documents

Professionnel Documents

Culture Documents

VLSI Lab Manual

Transféré par

ramanujamdineshTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

VLSI Lab Manual

Transféré par

ramanujamdineshDroits d'auteur :

Formats disponibles

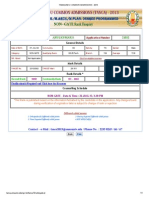

UCF

Pin Details

Verilog code for all gates. module allgates(A, B, not1, or2, and3, nor4, nand5, xor6, xnor7); input A; input B; output not1; output or2; output and3; output nor4; output nand5; output xor6; output xnor7; reg not1; reg or2; reg and3; reg nor4; reg nand5; reg xor6; reg xnor7; always@(A or B) begin not1 = ~ (A); and3 = (A) & (B); or2 = A | B; nand5 = ~((A) & (B)); nor4 = ~((A) | (B)); xor6 = (A) ^ (B); xnor7 = ~((A) ^ (B)); end endmodule

UCF NET NET NET NET NET NET NET NET NET

file(User constraint file): "A" LOC = " " ; "and3" LOC = " " ; "B" LOC = " " ; "nand5" LOC = " " ; "nor4" LOC = " " ; "not1" LOC = " " ; "or2" LOC = " " ; "xnor7" LOC = " " ; "xor6" LOC = " " ;

PLACE & ROUTE SIMULATION:

POST PLACE & ROUTE SIMULATION:

Verilog code for 4-1 Multiplexer. module mux(en, a, y,sel); input en; input [3:0] a; input[1:0] sel; output y; reg y; always@(en or a) begin if(!en) y=1'b0; else case(sel) 2'b00 : y = a[3]; 2'b01 : y = a[2]; 2'b10 : y = a[1]; 2'b11 : y = a[0]; endcase end endmodule USER CONSTRAINTS: NET "a[0]" LOC = " NET "a[1]" LOC = " NET "a[2]" LOC = " NET "a[3]" LOC = " NET "en" LOC = " NET "sel[0]" LOC = NET "sel[1]" LOC = NET "y" LOC = "

" " " " " ;

; ; ; ;

" " ; " " ; " ;

Multiplexer:

Schematic diagram:

Truth table:

K-Map:

PLACE & ROUTE SIMULATION:

POST PLACE & ROUTE SIMULATION:

Verilog code for Decoder. module decoder(a, en, y); input[1:0] a; input en; output[3:0] y; reg[3:0] y; always@(en or a) begin if(!en) y= 4'b0000; else case(a) 2'b00 : y = 4'b0001; 2'b01 : y = 4'b0010; 2'b10 : y = 4'b0100; 2'b11 : y = 4'b1000; default :y = 4'b0000; endcase end endmodule USER CONSTRAINTS: NET "a[0]" LOC = " " ; NET "a[1]" LOC = " " ; NET "en" LOC = " " ; NET "y[0]" LOC = " " ; NET "y[1]" LOC = " " ; NET "y[2]" LOC = " " ; NET "y[3]" LOC = " " ;

PLACE & ROUTE SIMULATION:

POST PLACE & ROUTE SIMULATION:

Verilog code for 4-bit counter. module counter(clk, reset, count); input clk; input reset; output [3:0] count; reg[3:0] count; integer timer_count1 = 0; reg clk_msec; always@(posedge clk) begin if(timer_count1==4999999) begin timer_count1=0; clk_msec=1'b1; end else begin timer_count1=timer_count1+1; clk_msec=1'b0; end end always@(posedge clk_msec) begin if(~reset) count = 4'b0000; else count = count+1; end endmodule

USER CONSTRAINTS: NET NET NET NET NET "CLK" LOC = " "COUNT[0]" LOC "COUNT[1]" LOC "COUNT[2]" LOC "COUNT[3]" LOC = = = = " ; " " ; " " ; " " ; " " ;

NET "RESET" LOC = "

" ;

Verilog code for Accumulator ACCUMULATOR: module accum(clk,clr,q,d); input clk,clr; output [3:0]q; input [3:0]d; reg [3:0] tmp; always @(posedge clk or posedge clr) begin if(clr) tmp = 4'b0000; else tmp = tmp + d; end assign q = tmp; endmodule OUTPUT:

Verilog code for PRBS generator

PRBS GENRATOR: module input input input input input PRBS(CLK, RESET, DIN, LOAD, SHIFT, Q); CLK; RESET; DIN; LOAD; SHIFT;

output [4:0] Q; parameter N = 5; // Width of the shift register parameter tap0 = 0; // Tap designators. Specify which FF's parameter tap1 = 2; parameter tap2 = 3; parameter tap3 = 4; reg [N-1:0] Q; reg [N-1:0] Q_N; wire TAPS; always @ (posedge CLK or posedge RESET) begin if (RESET) Q <= 0-1; else Q <= Q_N; end assign TAPS = Q[tap0] ^ Q[tap1] ^ Q[tap2] ^ Q[tap3]; always @ (Q or SHIFT or LOAD or DIN or TAPS) begin Q_N = Q; if (LOAD) Q_N = {DIN, Q[N-1:1]}; else if (SHIFT) Q_N = {TAPS, Q[N-1:1]}; end endmodule

OUTPUT:

Verilog code for 4-bit multiplier 4-BIT MULTIPLIER: module multiplier(a, b, res); input a[3:0] ; input b[3:0] ; output res [7:0]; assign res = a * b; endmodule

OUTPUT: PLACE & ROUTE SIMULATION:

POST PLACE & ROUTE SIMULATION:

Vous aimerez peut-être aussi

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- New IELTS Writing Answer SheetDocument4 pagesNew IELTS Writing Answer Sheetraaj2240% (5)

- AnnexureD PDFDocument1 pageAnnexureD PDFMukesh ShahPas encore d'évaluation

- Ielts 42 Topics For Speaking Part 1Document32 pagesIelts 42 Topics For Speaking Part 1Zaryab Nisar100% (1)

- ArulDocument1 pageArulramanujamdineshPas encore d'évaluation

- Savi TancetDocument3 pagesSavi TancetJasmine DavidPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- List of Books - EEE Department LibraryDocument44 pagesList of Books - EEE Department Libraryali ghalibPas encore d'évaluation

- GC310Document4 pagesGC310muhammad arif100% (1)

- Unit 3 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument8 pagesUnit 3 - Microprocessor & Its Application - WWW - Rgpvnotes.inPrayag ParasharPas encore d'évaluation

- Modeling and Simulation of SSPC Based On Dymola Software and Modelica LanguageDocument5 pagesModeling and Simulation of SSPC Based On Dymola Software and Modelica LanguageWilliam Jaldin CorralesPas encore d'évaluation

- Msi ms-7204 Rev 1A SCHDocument33 pagesMsi ms-7204 Rev 1A SCHТарас ІщакPas encore d'évaluation

- Kyunghi Chang: Inha University, Electronic Engineering DepartmentDocument7 pagesKyunghi Chang: Inha University, Electronic Engineering Department임동훈Pas encore d'évaluation

- Drx3960a Ic100Document10 pagesDrx3960a Ic100Justin WilliamsPas encore d'évaluation

- Department of Electronics & Instrumentation: Question Bank: CS 2361 EMBEDDED SYSTEMDocument8 pagesDepartment of Electronics & Instrumentation: Question Bank: CS 2361 EMBEDDED SYSTEMBarkavi CharuPas encore d'évaluation

- Yaesu FT 80C Service ManualDocument80 pagesYaesu FT 80C Service ManualRobert/YG2AKR82% (11)

- Haier 2968Document50 pagesHaier 2968Evelyn NaranjoPas encore d'évaluation

- 6t SramDocument13 pages6t SramRekha KumariPas encore d'évaluation

- ASIC Interview Question & Answer: Memory Interface QuestionsDocument5 pagesASIC Interview Question & Answer: Memory Interface QuestionsRajendra PrasadPas encore d'évaluation

- Electronic ComponentsDocument23 pagesElectronic ComponentsUma Venkata SumanthPas encore d'évaluation

- Elektor Electronics USA 1991 06Document80 pagesElektor Electronics USA 1991 06Patrik1968Pas encore d'évaluation

- HiSIM-HV - A Compact Model For Simulation of High-Voltage MOSFET CircuitsDocument8 pagesHiSIM-HV - A Compact Model For Simulation of High-Voltage MOSFET CircuitsMa SeenivasanPas encore d'évaluation

- Usb ItnDocument6 pagesUsb ItnEU VaPas encore d'évaluation

- Automatic Night-Lamp With Morning AlarmDocument1 pageAutomatic Night-Lamp With Morning Alarmapi-3736447100% (1)

- Check Zone & Redundant BB ProtnDocument2 pagesCheck Zone & Redundant BB Protnking_electricalPas encore d'évaluation

- VCO Produces Positive and Negative Output Frequencies PDFDocument4 pagesVCO Produces Positive and Negative Output Frequencies PDFagmnm1962100% (1)

- Tda7000 An192Document14 pagesTda7000 An192Tim HoadPas encore d'évaluation

- Make A Solar Panel Using DiodesDocument9 pagesMake A Solar Panel Using Diodesilhafs5600Pas encore d'évaluation

- Avr Atmega 8 Uc: Lets Learn Fundamentals !!Document40 pagesAvr Atmega 8 Uc: Lets Learn Fundamentals !!malhiavtarsinghPas encore d'évaluation

- Casa Systems Advantech Intel and Wind River - Virtual Mobile Security at The Network EdgeDocument5 pagesCasa Systems Advantech Intel and Wind River - Virtual Mobile Security at The Network EdgeoskcarrasquiPas encore d'évaluation

- Formenti 19-1-CHASSIS Service ManualDocument106 pagesFormenti 19-1-CHASSIS Service Manualschemy111Pas encore d'évaluation

- Design of Rogowski Coil With IntegratorDocument32 pagesDesign of Rogowski Coil With Integratorourbobby100% (1)

- RDSO Specification IRS S - 91 - 2013Document13 pagesRDSO Specification IRS S - 91 - 2013nvnrajesh123Pas encore d'évaluation

- Mitsubishi - Service Manual - Chassis V21Document83 pagesMitsubishi - Service Manual - Chassis V21api-3725622100% (4)

- Indramat Digital Drive Diagnostics: Distance Homing Switch-Reference Mark Error (S-298-9)Document1 pageIndramat Digital Drive Diagnostics: Distance Homing Switch-Reference Mark Error (S-298-9)Muhammad FajriPas encore d'évaluation

- Sony cdx-s2210-s-x S2250ee sw330 Ver-1.3 SM PDFDocument82 pagesSony cdx-s2210-s-x S2250ee sw330 Ver-1.3 SM PDFAlex Rivera100% (1)

- Lecture 6 Differential ProtectionDocument39 pagesLecture 6 Differential ProtectionIhtisham uddinPas encore d'évaluation