Académique Documents

Professionnel Documents

Culture Documents

Decoder Explanation

Transféré par

nivethadavidsonCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Decoder Explanation

Transféré par

nivethadavidsonDroits d'auteur :

Formats disponibles

VHDL 4 : (ver.

2b)

VHDL 4

Building blocks of a computer

VHDL 4 : (ver.2b)

VHDL 4 Building blocks of a computer

We will study the building blocks of a computer.

Control units are state machines, which have Flip-flops,

decoders, multiplexers etc. Beware that , there are usually more than one way to design the same digital system in VHDL

VHDL 4 : (ver.2b)

A typical CPU

FFs=Flip-flops

Control Unit State machine Registers (FFs)

A state machine

contains FFs

Address bus

(latches) data-bus Memory

I/O control logic

(state machine)

ALU

(state machine)

Transceivers

(bi-directional buffers )

VHDL 4 : (ver.2b)

Use VHDL to make digital system building blocks

1) latch, 2) flipflop with asynchronous reset, 3) flipflop with synchronous reset, 4) tri state buffer, 5) decoder, 6) multiplexer, 7) bi-directional buffer,

VHDL 4 : (ver.2b)

VHDL Exercise 4 1) Latch: when gate=1, output follows input (level sensitive)

1 entity latch_ex is

2 port (gate, in1 : in std_logic; 3

Latch 1-bit memory DQ in1 out1 C gate

out1 : out std_logic); 4 end latch_ex; 5 architecture latch_ex_arch of latch_ex is 6 begin sensitivity list 7 process (gate,in1) 8 begin 9 if (gate = '1') then 10 out1 <= in1; http://faculty.kfupm.edu.sa/COE/ashraf/Ric hFilesTeaching/COE022_200/Chapter4_1.ht 11 end if; m, or P.72 Advanced Digital Design with 12 end process; the Veriolog HDL by M.D. Ciletti 13 end latch_ex_arch; The process executes once when gate or in1 changes

VHDL 4 : (ver.2b)

Exercise 4.1 on latch: draw q

In1 gate in1 Latch q

gate

q

VHDL 4 : (ver.2b)

2) Edge-triggered Flip-flop with asyn. reset : reset before clock

statement

1 architecture dff_asyn_arch of dff_asyn is

2 begin

3 process(clock, reset) 4 begin 5

sensitivity list

if (reset = '1') then 6 out1 <= '0'; 7 elsif clock = '1' and clock'event then 8 out1 <= in1; 9 end if; 10 end process; 11 end dff_asyn_arch;

in1 clock

Latch with reset D out1

reset

edge triggered clock or rising_edge(clock)

VHDL 4 : (ver.2b)

Exercise 4.2 on flip-flops:draw qe

D CK CK

Edge (50%) triggered FF

qe

qe

VHDL 4 : (ver.2b)

Exercise 4.3 on architecture dff_asyn_a

When will line 3 be executed? Which is more powerful: clock or reset?

1 architecture dff_asyn_arch of dff_asyn is

2 begin

3 process(clock, reset) 4 begin 5

For asyn. reset flipflop asyn. reset and clock must be in the sensitivity list

if (reset = '1') then 6 out1 <= '0'; 7 elsif clock = '1' and clock'event then 8 out1 <= in1; 9 end if; 10 end process; 11 end dff_asyn_arch;

VHDL 4 : (ver.2b)

10

Exercise 4.4 on different flip-flops

What is the difference between level triggered and edge

triggered flip-flops? **In Xilinx-Foundation all flip-flops are treated as 50% edge triggered flip-flops. What is the difference between

synchronous reset (syn-reset) flip-flops and asynchronous reset (asyn-reset) flip-flops?

Discuss the difference between a latch and a flip flop.

VHDL 4 : (ver.2b)

11

3) Flip-flop with syn. reset: clock before reset statement 1 architecture dff_syn_arch of dff_syn is 2 begin process(clock,reset) reset can be removed, 4 begin -but allowed 5 if clock = '1' and clock'event then edge triggered clock 6 if (reset = '1') then 7 out1 <= '0'; 8 else reset 9 out1 <= in1; out1 10 end if; in1 11 end if; D 12 end process; clock 13 end dff_syn_arch;

Discuss why reset is not needed in the sensitivity list

VHDL 4 : (ver.2b)

12

Difference between Syn. & Asyn. RESET flip-flops (FF)

The order of the statements inside the

process determines Syn. or Asyn. reset

Syn. Reset Flip-Flop (check clock first)

if clock = '1' and clock'event then

if (reset = '1') then

Asyn. Reset Flip-Flop (check reset first)

if (reset = '1') then

q <= '0'; elsif clock = '1' and clock'event then

VHDL 4 : (ver.2b)

13

4) Tri state buffer: using when-else

(Use capital letter big Z for float, Z is a reserved character)

remember: Z is a scissor

1 entity tri_ex is

2 port (in1, control : in std_logic; 3

control out1 in1 Z=float

out1 : out std_logic); 4 end tri_ex; 5 architecture tri_ex_arch of tri_ex is 6 begin 7 out1 <= in1 when control = '1' else 'Z'; 8 end tri_ex_arch;

VHDL 4 : (ver.2b)

14

A decoder (N bits --> 2N bits)

Picture from: http://www.safesdirect.com/safes/meilink/safes.html

VHDL 4 : (ver.2b)

15

5) Decoder: using if statements

1 architecture decoder_a of decoder is 2 begin 3 process (in1, in2)

sensitivity list

in='1' and in2='0', open the safe

4 begin

5 6 7

8

9 10 11 12 13 14

if in1 = '0' and in2 = '0' then out00 <= '1'; else case 1 out00 <= '0'; end if; if in1 = '0' and in2 = '1' then out01 <= '1'; else out01 <= '0'; case 2 end if;

out00 in1 out10 out11 in2

out01

VHDL 4 : (ver.2b)

16

(contin.)Decoder

15 if in1 = '1' and in2 = '0' then 16 out10 <= '1'; case 3 (open the safe) 17 else 18 out10 <= '0'; 19 end if; 20 if in1 = '1' and in2 = '1' then 21 out11 <= '1'; 22 else 23 out11 <= '0'; case 4 24 end if; 25 end process; 26 end decoder_a;

VHDL 4 : (ver.2b)

17

6) Multiplexer (2N bits --> N bits) (the reverse of decoder)

1 architecture mux_arch of mux is 2 begin 3 process (in1, in2, ctrl) 4 begin 5 if ctrl = '0' then 6 out1 <= in1; 7 else 8 out1 <= in2; 9 end if; 10 end process; end mux_arch;

in1 in2 crtl in1 in2 crtl out1

out1

Mux

VHDL 4 : (ver.2b)

18

Note:7) Bi-directional bus: using data flow concurrent statements

1 entity inout_ex is

2 port (io1, io2 : inout std_logic;

3

ctrl : in std_logic); 4 end inout_ex; 5 6 architecture inout_ex_a of inout_ex is 7 --signal outbuf, inbuf : std_logic; 8 begin 9 io1 <= io2 when ctrl = '1' else 'Z'; 10 io2 <= io1 when ctrl = '0' else 'Z'; 11 end inout_ex_a;

ctrl

io2

io1

concurrent statements

VHDL 4 : (ver.2b)

19

Exercise 4.5 for Bi-directional bus

Crt=1, io1 follow io2_in Crt=0, io2 follow io1_in Plot io1 io2

io2

R=10K

ctrl io1

R=10K

Io2_in

Io1_in

ctrl Io1_in io1 Io2_in Io2

VHDL 4 : (ver.2b)

20

Quick revision

You should know how to design asynchronous , synchronous reset flip-flops tri state buffers, Combination logics

decoders,

multiplexers,

bi-directional buffers,

VHDL 4 : (ver.2b)

21

Appendix: do variables in processes have memory. (Good

practice: Initialize variables before use; assign values to variables from input first)

library IEEE; use IEEE.std_logic_1164.all; entity test is port (a,reset_v1: in std_logic; b ,c: out std_logic); end test; architecture test_arch of test is begin label_proc1: process (a,reset_v1)

variable v1 : std_logic; begin if reset_v1 ='1' then v1:= not a; end if; b<=a; c<=v1; end process label_proc1;

end test_arch;

V1 stays at two different levels depending on previous result

**The answer is yes. That means after a process is called, the state of a variable will be stored for the next time the process is being run again.

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Radiation Safety Officers Handbook A PDFDocument100 pagesRadiation Safety Officers Handbook A PDFAlejandro Zubiate100% (1)

- Measure RPA ROI with KPIsDocument4 pagesMeasure RPA ROI with KPIsAdnan FarooqPas encore d'évaluation

- F3 Maths 2012 1stexam Paper1Document3 pagesF3 Maths 2012 1stexam Paper1YiuhangLeung100% (2)

- Fractal ForestsDocument50 pagesFractal ForestsWell Fournier0% (1)

- Ms Word McqsDocument12 pagesMs Word McqsUraiBa AnsaRi0% (1)

- Types of EvidenceDocument13 pagesTypes of EvidenceSteven Jan Sab-itPas encore d'évaluation

- Stakeholder RegisterDocument7 pagesStakeholder Registerrouzbehk6515Pas encore d'évaluation

- 02 Stuck Pipe - Free Point & Back Off PDFDocument31 pages02 Stuck Pipe - Free Point & Back Off PDFام فاطمة البطاط100% (2)

- Detailed Scheduling Planning Board Technical HelpDocument6 pagesDetailed Scheduling Planning Board Technical Helpmanojnarain100% (1)

- Engine Retrofit Guide v8Document70 pagesEngine Retrofit Guide v8Romulo AlvarezPas encore d'évaluation

- ASME PTC 6 - 1996 Steam Turbine Performance Test CodeDocument124 pagesASME PTC 6 - 1996 Steam Turbine Performance Test CodeKristianPas encore d'évaluation

- Boeing Tests Jet Fuel From TobaccoDocument12 pagesBoeing Tests Jet Fuel From TobacconivethadavidsonPas encore d'évaluation

- ChemDocument20 pagesChemnivethadavidsonPas encore d'évaluation

- EC1401 VLSI - Question Bank (N.shanmuga Sundaram)Document35 pagesEC1401 VLSI - Question Bank (N.shanmuga Sundaram)Dr. N.Shanmugasundaram50% (2)

- Vlsi LabDocument95 pagesVlsi LabnivethadavidsonPas encore d'évaluation

- Vlsi LabDocument95 pagesVlsi LabnivethadavidsonPas encore d'évaluation

- Dip PDFDocument34 pagesDip PDFSelva Raj MPas encore d'évaluation

- Broadside AntennaDocument2 pagesBroadside AntennanivethadavidsonPas encore d'évaluation

- ECE 6th SEM SyllabusDocument113 pagesECE 6th SEM SyllabusnivethadavidsonPas encore d'évaluation

- Guide To Preparing Tax Research MemosDocument2 pagesGuide To Preparing Tax Research MemoscglaskoPas encore d'évaluation

- Airtel Case Study Channel StrategyDocument2 pagesAirtel Case Study Channel StrategyTushar GuptaPas encore d'évaluation

- INCaDocument47 pagesINCaMehdi SoltaniPas encore d'évaluation

- Phase 2 (57 Selectee)Document4 pagesPhase 2 (57 Selectee)AmarPas encore d'évaluation

- 3M Water Filtration Products - High Flow Series - HF40 and HF40 - S Performance Data SheetDocument2 pages3M Water Filtration Products - High Flow Series - HF40 and HF40 - S Performance Data SheetSergioPas encore d'évaluation

- Manifest Merger Debug ReportDocument14 pagesManifest Merger Debug ReportRam PankhaniyaPas encore d'évaluation

- Prediction On Miss Mamta Banerjee Honorable CM of West Bengal Much Much Before Result and Election by Indranil RayDocument24 pagesPrediction On Miss Mamta Banerjee Honorable CM of West Bengal Much Much Before Result and Election by Indranil RayIndranil RayPas encore d'évaluation

- ICN Question Bank Unit-1, 2 and 3 (Upto GSM Identifier)Document1 pageICN Question Bank Unit-1, 2 and 3 (Upto GSM Identifier)Snehal PatelPas encore d'évaluation

- FRS - Brake System - TrainsetDocument12 pagesFRS - Brake System - TrainsetCad TutorPas encore d'évaluation

- DSP Lab - ScilabDocument17 pagesDSP Lab - ScilabSai Nikshipth MaddhugaruPas encore d'évaluation

- 5100 Series Gas Analyzer: Product Data SheetDocument2 pages5100 Series Gas Analyzer: Product Data SheetSai KamalaPas encore d'évaluation

- Iso 9712 2012 PDFDocument19 pagesIso 9712 2012 PDFBala KrishnanPas encore d'évaluation

- Web 2.0, Web 3.0, and User Participation in The WebDocument13 pagesWeb 2.0, Web 3.0, and User Participation in The WebDina Navarro DiestroPas encore d'évaluation

- Stanley I. Sandler: Equations of State For Phase Equilibrium ComputationsDocument29 pagesStanley I. Sandler: Equations of State For Phase Equilibrium ComputationscsandrasPas encore d'évaluation

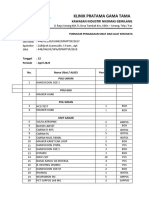

- Pengadaan Obat Dan Alkes TGL 22 April 2021 Klinik PembantuDocument8 pagesPengadaan Obat Dan Alkes TGL 22 April 2021 Klinik PembantuIsma Prasetya WardaniPas encore d'évaluation

- Present Environment and Sustainable Development - Annual Review Report 2015Document7 pagesPresent Environment and Sustainable Development - Annual Review Report 2015catalinlungeanu758Pas encore d'évaluation

- Overhead Line Splices Automatic Copper: Splices For Metric ConductorDocument27 pagesOverhead Line Splices Automatic Copper: Splices For Metric ConductorAzad RahmanPas encore d'évaluation

- Filters in GeneralDocument3 pagesFilters in GeneralJoseGarciaRuizPas encore d'évaluation

- ResearchDocument48 pagesResearchCai De JesusPas encore d'évaluation