Académique Documents

Professionnel Documents

Culture Documents

PWMC - Pulse Width Modulation Controller

Transféré par

Melissa MillerDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

PWMC - Pulse Width Modulation Controller

Transféré par

Melissa MillerDroits d'auteur :

Formats disponibles

PWM

Pulse Width Modulation

PWM

PWM Features

General Features

Four Channels, one 16-bit counter per channel, One common clock generator, providing 13 different clocks,

One Modulo n counter providing eleven clocks, Two independent linear dividers working on modulo n counter output,

Channel Programming

Independent enable/disable commands, Independent clock selection, Independent period and duty cycle, with double buffering system, Programmable selection of the output waveform polarity, Programmable center or left aligned output waveform.

PWM

View of the external PWM Signals

4 Multiplexed Channel outputs with PIOA lines Dedicated high current output pad

- Multiplexed to PA0, PA1 and PA2 (respectively for PWM0, PWM1 and PWM2) allow the user to drive external circuitry with load current up to 16 mA (instead of 8 mA for standard pads)

PWM

PWM into the AT91SAM7S

PMC has to be programmed 1st for PWM to work: Clock Enabling

Set the PMC_PCER (Peripheral Clock Enable Register), bit 10 (PID10). Disable targeted PIO line(s) by using PIO_PDR (PIO Disable Register) as shown below

PIO Controller has to be programmed for the pins to behave as intended

-

I/O Line PA0 PA1 PA2 PWM0 PWM1 PWM2

Peripheral A TIOA0 TIOB0 SCK0

Peripheral B

Select between Peripheral A or B, respectively, in PIO_ASR or PIO_BSR in order to select the PWM peripheral output channel(s) on the right pad(s).

PWM

PWM Architecture

The PWM Peripheral can be split up into two parts

1- The PWM Controller which is made of:

Clock Generator => Clock generation from the Master Clock (MCK) Channel Control => Enable/Disable Channel Interrupt Generator

2- Channel Modules:

Clock Selector Channel Running Mode Manager Duty Cycle and frequency Control Counter value Update register

PWM

PWMC: Clock Generator

PWM_MR (Mode Register)

27 24 23 16 11 8 7 0

PREB

DIVB

PREA

DIVA

/1 /2 /4 /8 /16

MCK

/32 /64 /128 /256 /512 /1024

1, ,1/3,..,1/255

1, ,1/3,..,1/255

CLKA

CLKB

PWM

PWMC: Channel and Interrupt Management

At PWMC level, the user can, independently, enable/disable each channel

PWM_DIS (Disable Register)

0 3 0 3

PWM_ENA (Enable Register) CHID3 CHID2 CHID1 CHID0 PWM_SR (Status Register)

3 0

CHID3 CHID2 CHID1 CHID0

CHID3 CHID2 CHID1 CHID0

The user can use the same control panel at interrupt level plus the dedicated mask register

PWM_IDR (Interrupt Disable Register)

3 0 3 0

PWM_IER (Interrupt Enable Register) CHID3 CHID2 CHID1 CHID0 PWM_IMR (Interrupt Mask Register)

3 0

CHID3 CHID2 CHID1 CHID0 PWM_ISR (Interrupt Status Register)

3 0

CHID3 CHID2 CHID1 CHID0

CHID3 CHID2 CHID1 CHID0

7

PWM

Set up the PWMC in your Application

PIO and PWM lines

Disable the PIO lines and select the right peripheral between A or B at multiplexing level. For power saving consideration, the PWM s clock is stoppped at Power Management Controller level by default.

Enable the PWM Clock

Set up the Clock Generator

Set up the targeted clocks which will be used for the 4 PWM Channels.

Channel Enabling

These tasks can be performed after the complete channel setting

Interrupt Enabling

PWM

Set up a PWM Channel

Per channel:

Channel Mode Register: Select the running mode of the channel Duty Cycle Register: 16-bit value to select the duty cycle of the signal Period Register: 16-bit value to select the period of the signal Counter Register: counter value Update Register: Specific register to modify, synchronously, the Duty Cycle Register or the Period Register.

PWM Channel 0,1,2 or 3

Period Control Update Register Duty Cycle Control

PWM Controller

PWM pad

Comparator

CLKA CLKB

MCK. down to MCK/1024

Clock Selector Counter

Interrupt

9

PWM

First Step: Clock Choice

PWM_CMR (Channel Mode Register)

3 0

CLKA CLKB

/1 /2 /4 /8 /16 /32 /64 /128

CPRE

At Channel level, the Channel Mode Register allows the user to choose between the 13 sources from the clock generator

Channels Counter

/256

/512 /1024

Clock Generator

10

PWM

What is the best clock source ?

The PWM duty cycle quantum is the first criterion:

The user has to know his minimum requested accuracy at duty cycle level. The duty cycle control is managed through a 16-bit PWM_CDTY register.

PWM_CDTY (Channel Duty Cycle Register)

15 0

N value

CDTY

The duty cycle quantum depends on the value written in Period Register:

The M value is the required number of event in order to complete one PWM channel period (or half period in center-aligned mode) PWM_CPRD (Channel Period Register)

15 0

M value

CPRD

The PWM Channel period being equal to M source period. N will be from 0 up to M value. The higher M value, the higher the N value can be, the lower the quantum.

11

PWM

Example of different PWM accuracy

In this first choice, the duty cycle quantum will be 1/75 of a period

CLKA CLKB Clock Generator on 750 kHz (/64) = 10 kHz

48 MHz

Clock Generator

Channel Period Register = 75

For the same period, the duty cycle quantum will be 1/4800 of a period.

CLKA CLKB

48 MHz

Clock Generator

Clock Generator on (1) =

48 MHz

Channel Period Register = 4800

10 kHz

12

PWM

How to modify a channel Period or a channel Duty Cycle value ?

Before to enable the PWM Channel at PWM Controller level (PWM_ENA Register): The user will be able to write directly into the PWM_CDTYx or PWM_CPRDx of this channel, respectively, for a duty cycle or period change. As soon as this PWM channel has been enabled: It is not possible to write into these previous registers. The user will have to use the Channel Update Register in order to modify one of the previous value.

The contain of the Update register is put into the PWM_CDTY or PWM_CPRD according to the value of CPD value in PWM_CMR

PWM_CMRx (Channel Mode Register)

10 3 0

CPD

CPRE

PWM_CDTYx 0 PWM_CUPDx 1 PWM_CUPDx

13

PWM

Channel Update Register: PWM_CUPD

Why use it:

In running mode, modifying the duty cycle or the period value can be done only via PWM_CUPD, The duty cycle or the period modification is going to be taken synchronously into account at the end of the period in progress, Before to write in PWM_CUPD, the user will have to be sure that the last write has been take into account. In other case, the previous data will be overlaid by the last one. Use the bit CPD, in PWM_CMR register, in order to select a duty cycle or period modification, Write the data into PWM_CUPD register.

How use it:

-

Note: It is not possible to modify, in the same PWM period for one channel, the duty cycle AND the period values.

14

PWM

PWM_CUPD Write method

PWM_ISR (Interrupt Status Register)

3 0

CHID3 CHID2 CHID1 CHID0 0 0 0 0

Reading PWM_ISR automatically clears CHIDx flags

PWM_ISR (Interrupt Status Register)

3 0

Polling or interrupt methods can be used:

A flag rises after an end of channel period (channel 1 for example)

CHID3 CHID2 CHID1 CHID0 0 0 1 0

Modifying duty cycle or period value in channel 1 can be possible without overlaying risk at PWM_CUPD level.

15

PWM

First Working Mode: Left-aligned

PWM_CMR (Channel Mode Register)

8 CALG=0 CPOL Lelt-Aligned Mode 9 When the PWM Counter reach the period value, it is cleared.

PWM_CPRD

PWM_CDTY 0

CPOL= 0

CPOL= 1

16

PWM

Left-aligned Limitation in Multi-Channel use

The left-aligned working mode does not allow to avoid overlapped transition in Multi-channel use

PWM_CPRD0 PWM_CDTY0 In Left-aligned Mode: One event depends on the duty cycle value and the other depends on the period value. For the same period, there will be overlapped event

Channel 0 Output

The period of both Channels are equal

Channel 1 Output (PWM_CDTY0 - PWM_CDTY1)

PWM_CPRD1

PWM_CDTY1

17

PWM

Second Working Mode: Center-aligned

PWM_CMR (Channel Mode Register)

8 CALG=0 CPOL Lelt-Aligned Mode 9

PWM_CPRD

PWM_CDTY 0

CPOL= 0

CPOL= 1

18

PWM

Center-aligned: Non-overlapped event Method

The center-aligned working mode allows to avoid overlapped transition in Multichannel use

PWM_CPRD0 PWM_CDTY0

Channel 0 Output

(PWM_CDTY0 - PWM_CDTY1) Channel 1 Output

PWM_CPRD1 PWM_CDTY1

19

Vous aimerez peut-être aussi

- Control DC Motor Speed using STM32 PWMDocument4 pagesControl DC Motor Speed using STM32 PWMJohn FarandisPas encore d'évaluation

- LPC2148 PWM Programming GuideDocument14 pagesLPC2148 PWM Programming GuideVinothkumar UrumanPas encore d'évaluation

- PWMDocument17 pagesPWMmaintboardPas encore d'évaluation

- Microcontrollers LabDocument19 pagesMicrocontrollers LabAMARNATHNAIDU77Pas encore d'évaluation

- The University of Texas at Arlington Timers, Capture/Compare/PWMDocument22 pagesThe University of Texas at Arlington Timers, Capture/Compare/PWMadamwaiz100% (1)

- Secrets of Arduino PWMDocument8 pagesSecrets of Arduino PWMpcrmengePas encore d'évaluation

- Secrets of Arduino PWMDocument20 pagesSecrets of Arduino PWMDany Setyawan100% (1)

- Infineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENDocument42 pagesInfineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENFatenn BellakhdharPas encore d'évaluation

- Ds PICDocument3 pagesDs PICSharad Chandra SharamaPas encore d'évaluation

- Os Segredos Do PWM Do ArduinoDocument6 pagesOs Segredos Do PWM Do ArduinoFernando EsquírioPas encore d'évaluation

- Safari - 13 Mai 2023 À 09:40Document1 pageSafari - 13 Mai 2023 À 09:40Paréto BessanhPas encore d'évaluation

- TimersDocument37 pagesTimersAnastasia PestereanPas encore d'évaluation

- 16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerDocument12 pages16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerLauderi MartinsPas encore d'évaluation

- PWM RegistersDocument14 pagesPWM RegistersAshok KumarPas encore d'évaluation

- On-Chip PeripheralsDocument73 pagesOn-Chip PeripheralsR R DeshmukhPas encore d'évaluation

- CCP PWMDocument19 pagesCCP PWMalaa_saq100% (1)

- HBridgeMotorControl With PICDocument11 pagesHBridgeMotorControl With PICcoceicr100% (3)

- Section 14. Motor Control PWM: HighlightsDocument56 pagesSection 14. Motor Control PWM: HighlightsCiprian Tironeac100% (1)

- L 122a 6Document13 pagesL 122a 6Bogdan Alin100% (1)

- LED Brightness Control Using PWM of LPC2138: ESD Lab Mini-ProjectDocument8 pagesLED Brightness Control Using PWM of LPC2138: ESD Lab Mini-ProjectAditya GadgilPas encore d'évaluation

- STM32 Timers TutorialDocument6 pagesSTM32 Timers TutorialHossein MajidiPas encore d'évaluation

- Atmel Avr Atmega48 PWMDocument9 pagesAtmel Avr Atmega48 PWMAlfred J. NgunyiPas encore d'évaluation

- Introduction To MSP430 MicrocontrollersDocument32 pagesIntroduction To MSP430 MicrocontrollersAlejandro OrtizPas encore d'évaluation

- Lecture7 MCU Timers - ADCDocument36 pagesLecture7 MCU Timers - ADCAKSHATA R CPas encore d'évaluation

- MCES - 18CS44 - Unit4 PWM - DCMotorDocument9 pagesMCES - 18CS44 - Unit4 PWM - DCMotorSAKSHAM PRASADPas encore d'évaluation

- CHAPTER 5 Hardware InterfacingDocument51 pagesCHAPTER 5 Hardware InterfacingCheng Ching HaoPas encore d'évaluation

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - C - 12Document42 pagesOsmeoisis 2022-09-06 15-33-19PIC - Mid - C - 12Tomás BurónPas encore d'évaluation

- TimersDocument51 pagesTimersSaravanan T YPas encore d'évaluation

- Atmega16: Square Wave GenerationDocument3 pagesAtmega16: Square Wave Generationshahbazalam4a5Pas encore d'évaluation

- Slaa 116Document21 pagesSlaa 116misaelrodrigoPas encore d'évaluation

- TWRKV46F150 PMSM SensorlessDocument22 pagesTWRKV46F150 PMSM Sensorlessb_dupPas encore d'évaluation

- En - stm32l4 WDG Timers GptimDocument64 pagesEn - stm32l4 WDG Timers GptimGia LữPas encore d'évaluation

- Timer Counter AVRDocument105 pagesTimer Counter AVRفايزميلي الأبد100% (1)

- 06 - Timer With PWM PDFDocument14 pages06 - Timer With PWM PDFSrikanth MahanthiPas encore d'évaluation

- PWM ManualDocument56 pagesPWM ManualAlexander Rodriguez GonzalezPas encore d'évaluation

- 06 Nutiny-Nuc029 PWMDocument25 pages06 Nutiny-Nuc029 PWMDharmendra SavaliyaPas encore d'évaluation

- 8-Bit Single Chip Microcontroller LC87F67C8ADocument27 pages8-Bit Single Chip Microcontroller LC87F67C8AAlbert GTPas encore d'évaluation

- DC Motor Speed ControlDocument5 pagesDC Motor Speed ControlAnita WulansariPas encore d'évaluation

- AVR_Timers0Document32 pagesAVR_Timers0Muhammad ejaz RamzanPas encore d'évaluation

- 1 Nghiên cứu, tìm hiểu 1.1 Principle of pulse generator 1.1.1 Generating PWMDocument4 pages1 Nghiên cứu, tìm hiểu 1.1 Principle of pulse generator 1.1.1 Generating PWMQuang Huy Doan NgocPas encore d'évaluation

- Atmel PWM Fan ControlDocument10 pagesAtmel PWM Fan ControlArijan BogovićPas encore d'évaluation

- Book PIC Microcontrollers-Chapter 5 CCP ModulesDocument17 pagesBook PIC Microcontrollers-Chapter 5 CCP ModulesHammamiSalah100% (1)

- Timers of ATmega328PDocument26 pagesTimers of ATmega328PZaryab Khalil SiddiquePas encore d'évaluation

- Cpm1A Series Micro PlcsDocument6 pagesCpm1A Series Micro PlcsVerbin DuandikaPas encore d'évaluation

- ELEC 3040/3050 Lab #7: PWM Waveform GenerationDocument22 pagesELEC 3040/3050 Lab #7: PWM Waveform GenerationBrandon2017Pas encore d'évaluation

- 3-Phase Sensorless BLDC Motor Control Development Kit With MC9S12G128 MCUDocument40 pages3-Phase Sensorless BLDC Motor Control Development Kit With MC9S12G128 MCUBogdan CosteaPas encore d'évaluation

- Micro ControllerDocument9 pagesMicro ControllerShameerPas encore d'évaluation

- RC Servo Motor Control Using LPC2148 MicrocontrollerDocument12 pagesRC Servo Motor Control Using LPC2148 Microcontrollersameer khanPas encore d'évaluation

- LC877364ADocument26 pagesLC877364AAlbert GTPas encore d'évaluation

- ks88c4400Document32 pagesks88c4400Cesar JakobyPas encore d'évaluation

- PWM Freq Arduino DueDocument9 pagesPWM Freq Arduino DueEdgar Eduardo Medina CastañedaPas encore d'évaluation

- Microcontroller Based Sinusoidal PWM Inverter For Photovoltaic ApplicationDocument4 pagesMicrocontroller Based Sinusoidal PWM Inverter For Photovoltaic ApplicationDumitrescu Camil SorinPas encore d'évaluation

- PWM DAN TIMERDocument54 pagesPWM DAN TIMERmasrinaPas encore d'évaluation

- Timer PWM Questions and AnswersDocument4 pagesTimer PWM Questions and AnswersAbdallah MiidounePas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Analog Circuit Design Volume Three: Design Note CollectionD'EverandAnalog Circuit Design Volume Three: Design Note CollectionÉvaluation : 3 sur 5 étoiles3/5 (2)

- The PIC Microcontroller: Your Personal Introductory CourseD'EverandThe PIC Microcontroller: Your Personal Introductory CourseÉvaluation : 1 sur 5 étoiles1/5 (2)

- Jind Institute of Engineering and TechnologyDocument1 pageJind Institute of Engineering and TechnologyRaman GuptaPas encore d'évaluation

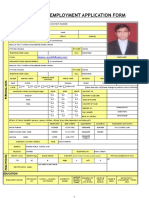

- Employment Application Form: SC ST DT NT SBC OBC Gen - CatDocument4 pagesEmployment Application Form: SC ST DT NT SBC OBC Gen - CatRaman GuptaPas encore d'évaluation

- Staff Selection Commission, Government of HaryanaDocument1 pageStaff Selection Commission, Government of HaryanaRaman GuptaPas encore d'évaluation

- Jind Institute of Engineering and TechnologyDocument1 pageJind Institute of Engineering and TechnologyRaman GuptaPas encore d'évaluation

- Employment Application Form - SIPS (2) KULDEEPDocument10 pagesEmployment Application Form - SIPS (2) KULDEEPRaman GuptaPas encore d'évaluation

- Employment Application Form: SC ST DT NT SBC OBC Gen - CatDocument4 pagesEmployment Application Form: SC ST DT NT SBC OBC Gen - CatRaman GuptaPas encore d'évaluation

- Employment Application Form SandeepDocument8 pagesEmployment Application Form SandeepRaman GuptaPas encore d'évaluation

- Employment Application Form ANILDocument4 pagesEmployment Application Form ANILRaman GuptaPas encore d'évaluation

- Hand Operated Die PunchDocument4 pagesHand Operated Die PunchRaman GuptaPas encore d'évaluation

- Sandeep Resume For F.EDocument2 pagesSandeep Resume For F.ERaman GuptaPas encore d'évaluation

- Employment Application Form - SIPS SumitDocument8 pagesEmployment Application Form - SIPS SumitRaman GuptaPas encore d'évaluation

- Employment Application Form GAURAV SAINIDocument10 pagesEmployment Application Form GAURAV SAINIRaman GuptaPas encore d'évaluation

- S&S June 2014Document2 pagesS&S June 2014Raman GuptaPas encore d'évaluation

- CEE Result of 280216 PDFDocument10 pagesCEE Result of 280216 PDFRaman GuptaPas encore d'évaluation

- d6395343 133791 7605216553Document2 pagesd6395343 133791 7605216553BasavarajBusnurPas encore d'évaluation

- SNS 2009 PaperDocument3 pagesSNS 2009 PaperRaman GuptaPas encore d'évaluation

- Employment Application Form: SC ST DT NT SBC OBC Gen - CatDocument4 pagesEmployment Application Form: SC ST DT NT SBC OBC Gen - CatRaman GuptaPas encore d'évaluation

- SandeepDocument2 pagesSandeepRaman GuptaPas encore d'évaluation

- d6395343 133791 7605216553Document2 pagesd6395343 133791 7605216553BasavarajBusnurPas encore d'évaluation

- Employment Application Form: SC ST DT NT SBC OBC Gen - CatDocument4 pagesEmployment Application Form: SC ST DT NT SBC OBC Gen - CatRaman GuptaPas encore d'évaluation

- F&W June 2014Document2 pagesF&W June 2014Raman GuptaPas encore d'évaluation

- Math-3 Dec 2011 PaperDocument3 pagesMath-3 Dec 2011 PaperRaman GuptaPas encore d'évaluation

- G20Document1 pageG20Raman GuptaPas encore d'évaluation

- Improving Human Resource Management Services Delivery Through Information TechnologyDocument63 pagesImproving Human Resource Management Services Delivery Through Information TechnologyRaman GuptaPas encore d'évaluation

- Math-3 June 2010 PaperDocument3 pagesMath-3 June 2010 PaperRaman GuptaPas encore d'évaluation

- De June 2014Document1 pageDe June 2014Raman GuptaPas encore d'évaluation

- Eim June 2014Document1 pageEim June 2014Raman GuptaPas encore d'évaluation

- De 2009 PaperDocument2 pagesDe 2009 PaperRaman GuptaPas encore d'évaluation

- Rain Water Harvesting: Gautam Banerjee UP Jal NigamDocument28 pagesRain Water Harvesting: Gautam Banerjee UP Jal NigamAniket Gurav100% (1)

- Math3 - Dec 2008Document3 pagesMath3 - Dec 2008Raman GuptaPas encore d'évaluation