Académique Documents

Professionnel Documents

Culture Documents

Race Condition in J-K Latch

Transféré par

Tejas DharaniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Race Condition in J-K Latch

Transféré par

Tejas DharaniDroits d'auteur :

Formats disponibles

RACE CONDITION IN J-K

FLIP FLOP

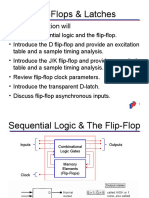

The J-K Flip Flop

CLK J K Qn+1 Qn+1

1 0 0 Qn Qn

1 0 1 0 1

1 1 0 1 0

1 1 1 Qn Qn

The J-K Flip Flop (contd.)

Timing Race

Many cascaded flip-flops, clocked simultaneously

with the input being passed to the output

The propagation delay in each device will be

cumulative and add up

If data doesn't ripple through the line and become

stable at each output before the next clock, bad

information passes into the next stage. This is called

timing race.

Race conditions give you bad data

Timing Race (contd.)

It takes at the most 45ns to get through each flip-flop

Approximate window of 180ns for which data is invalid

Insignificant while counting hours but significant for

counting milliseconds

Ton > Overall Tpd

Race Condition In J-K Flip Flops

What?

Takes place when both inputs J and K are

high (J=K=1)

Multiple instances of toggling of the output in

level triggered J-K flip flops

Ambiguous output and erratic behaviour

May not always produce predictable output

Why?

Level triggered circuits

Output will change every time the input

changes

Unwanted changes in input may occur due to

noise, consequently changing the output

Occurs mainly because of the feedback

connections (Q &Qbar)

Race Condition In J-K Flip Flops

The time period of the clock pulse is greater than the

propagation delay of the latch/flip flop

Output changes or toggles in a single clock period

If it toggles even number of times the output is same

but if it toggles odd number of times then the output

is complemented

This leads to ambiguity

Race Condition In J-K Flip Flops

How?

When J= K =1 and clock= 1, the value of output

should be toggled

Practically, we do not get toggling

Race Condition In J-K Flip Flops

Solutions

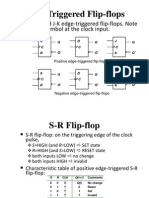

1. If Ton < Tpd

2. Edge Triggering

Output is affected only at the time of presence of

edge i.e. only during the rising or falling edge of a

clock pulse

When the input clock pulse makes a +ve/-ve going

transition, the input is transferred to output

Changes in input when clock is maintained at a steady

1 value do not affect Q

A -ve pulse transition does not affect the output and

nor does when clock pulse is 0

Thus, edge triggering eliminates any feedback

problem

Solutions

3. J-K Master Slave flip flop

Two latches connected serially

Clock is connected directly to Master and inverted to Slave

Inputs fed at the +ve edge and outputs available at the -ve

edge

Solutions

When clock is

high Master is

functional and

when clock is

low Slave is

functional

The outputs from the master flip flop are only seen by

the gated slave flip flop when the clock input goes LOW

to logic level 0

Master-Slave JK Flip flop is a Synchronous device as it only

passes data with the timing of the clock signal

Solutions

Vous aimerez peut-être aussi

- Flip Flop Counters PDFDocument15 pagesFlip Flop Counters PDFAdarsh SinghPas encore d'évaluation

- Practical 7 AIM: Design / Simulate Master Slave JK Flip FlopDocument4 pagesPractical 7 AIM: Design / Simulate Master Slave JK Flip FlopDivyes PPas encore d'évaluation

- RaceDocument5 pagesRaceRCEE-2020 ONLINE FDPPas encore d'évaluation

- UntitledDocument8 pagesUntitledlalita chauhanPas encore d'évaluation

- Sequential Circuits: Latches and Flip-FlopsDocument32 pagesSequential Circuits: Latches and Flip-FlopsRohan BorgalliPas encore d'évaluation

- EE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Document19 pagesEE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanPas encore d'évaluation

- Gate TipsDocument3 pagesGate TipsBharadwaja VyasaPas encore d'évaluation

- EET206 M4 Ktunotes - inDocument195 pagesEET206 M4 Ktunotes - inKhaled AlshurmanPas encore d'évaluation

- Flip FlopsDocument60 pagesFlip FlopsA10-14Rajat KumarPas encore d'évaluation

- MD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5Document17 pagesMD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5shyburrahaman120Pas encore d'évaluation

- Topic 5 - Flip Flops Sequential CircuitsDocument16 pagesTopic 5 - Flip Flops Sequential CircuitsShivneet KumarPas encore d'évaluation

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document5 pagesPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraPas encore d'évaluation

- Jkflip FlopDocument27 pagesJkflip FlopUsama NaveedPas encore d'évaluation

- Master Slave Flip FlopDocument2 pagesMaster Slave Flip FlopShruti ChandraPas encore d'évaluation

- Sequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos TatasDocument22 pagesSequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatasvikramkolanu100% (2)

- Flip FlopDocument6 pagesFlip FlopMuzakki SathorPas encore d'évaluation

- Report For Experiment 10: Lab 1 Data and ObservationsDocument2 pagesReport For Experiment 10: Lab 1 Data and ObservationsFaiza Tabassam 546-FET/BSEE/F19Pas encore d'évaluation

- Computer Architecture 1Document39 pagesComputer Architecture 1ARAFAT GaamanPas encore d'évaluation

- Flip Flop Sect 2Document31 pagesFlip Flop Sect 2Bink BonkPas encore d'évaluation

- 7 & 8. Sequential CircuitsDocument24 pages7 & 8. Sequential CircuitsDr. Sanjeev PuniaPas encore d'évaluation

- Study of Flip Flops Using ICsDocument5 pagesStudy of Flip Flops Using ICssaravanan_12aPas encore d'évaluation

- Flip FlopsDocument40 pagesFlip Flopszohaiba338Pas encore d'évaluation

- FlipflopsDocument38 pagesFlipflopsajith p pPas encore d'évaluation

- Name:-Bharat Arora Section: - A Rollno: - 18 University Rollno: - 191500212Document6 pagesName:-Bharat Arora Section: - A Rollno: - 18 University Rollno: - 191500212Deepam AsnaniPas encore d'évaluation

- Flip Flops: 1.definition 2.basic Flip Flop Types (SR, D, JK, T) 3.conversion of 1 FF To OtherDocument29 pagesFlip Flops: 1.definition 2.basic Flip Flop Types (SR, D, JK, T) 3.conversion of 1 FF To Otherrdb003Pas encore d'évaluation

- Flip Flops: Prof. Jagannadha Naidu KDocument14 pagesFlip Flops: Prof. Jagannadha Naidu KArvind kumar PrajapatiPas encore d'évaluation

- FlipFlops Chapter 5Document27 pagesFlipFlops Chapter 5jenny khanPas encore d'évaluation

- Chapter 2.2Document15 pagesChapter 2.2OzzyPas encore d'évaluation

- DCLD Unit 3Document57 pagesDCLD Unit 3sanskritijha.csPas encore d'évaluation

- The JK FlipDocument4 pagesThe JK Flipraj2510Pas encore d'évaluation

- Learn The Basics First!: Flip FlopsDocument7 pagesLearn The Basics First!: Flip FlopsBharath Kumar100% (1)

- Chap 8Document8 pagesChap 8mailusman9835Pas encore d'évaluation

- J-K Flip FlopDocument5 pagesJ-K Flip FlopNagham Hikmat AzizPas encore d'évaluation

- Sequential Circuits: Flip FlopsDocument16 pagesSequential Circuits: Flip FlopsSonam SoniPas encore d'évaluation

- Module 5 - Counter Design Problems and Flip-Flops - Oct 8thDocument65 pagesModule 5 - Counter Design Problems and Flip-Flops - Oct 8thRavi CharanPas encore d'évaluation

- Sequential CircuitsDocument134 pagesSequential CircuitsRajat KumarPas encore d'évaluation

- DE Module 03Document20 pagesDE Module 03Rishabh TiwariPas encore d'évaluation

- Module 4Document26 pagesModule 4OKPas encore d'évaluation

- Module-4: Flip-Flops, Registers and CountersDocument111 pagesModule-4: Flip-Flops, Registers and CountersSanchitha GowdaPas encore d'évaluation

- Flip Flops and ApplicationsDocument10 pagesFlip Flops and ApplicationsjaltitiPas encore d'évaluation

- EC 201 Basic Electronics: Tarun Tripathi School of Electronics Engineering KIIT UniversityDocument35 pagesEC 201 Basic Electronics: Tarun Tripathi School of Electronics Engineering KIIT Universityvarun_1992100% (1)

- FlipssDocument8 pagesFlipssOrion Starbwoy BlackstockPas encore d'évaluation

- Latch and Flip-FlopDocument58 pagesLatch and Flip-FlopDalila Nadia RazaliPas encore d'évaluation

- Sequential Circuits: Presented By: Group 3Document30 pagesSequential Circuits: Presented By: Group 3Jalaj SrivastavaPas encore d'évaluation

- Title ObjectiveDocument4 pagesTitle ObjectiveShekhar ShuklaPas encore d'évaluation

- Counters in Digital Electronics - JavatpointDocument5 pagesCounters in Digital Electronics - JavatpointRA NDYPas encore d'évaluation

- Digital Logic DesignDocument26 pagesDigital Logic DesignPranav GangwarPas encore d'évaluation

- CSE231 Lecture 6Document31 pagesCSE231 Lecture 6Rayhan Amin 2212830042Pas encore d'évaluation

- Report FlipFlopsDocument15 pagesReport FlipFlopsPratibh SinhaPas encore d'évaluation

- DL CH 4Document50 pagesDL CH 4Praches AcharyaPas encore d'évaluation

- DSC Experiment 2Document7 pagesDSC Experiment 2Chinmay NarkhedePas encore d'évaluation

- DLLec8b NotesDocument9 pagesDLLec8b NotesChintan MandalPas encore d'évaluation

- The Basic JK Flip-FlopDocument4 pagesThe Basic JK Flip-Flopom1444100% (1)

- Latched, Flip-Flops, and TimersDocument36 pagesLatched, Flip-Flops, and TimersMuhammad Umair AslamPas encore d'évaluation

- Unit 4 D-JK Flip FlopsDocument17 pagesUnit 4 D-JK Flip FlopsRongeet SodhiPas encore d'évaluation

- 2 FlipflopDocument19 pages2 FlipfloplidhisijuPas encore d'évaluation

- The J K Flip FlopDocument3 pagesThe J K Flip FlopSaanguPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- PNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGD'EverandPNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGPas encore d'évaluation

- Spare CellDocument8 pagesSpare CellpravinPas encore d'évaluation

- Cover LetterDocument1 pageCover LetterTejas DharaniPas encore d'évaluation

- Cmos and Finfet TechDocument5 pagesCmos and Finfet TechTejas DharaniPas encore d'évaluation

- 3D Trigate TransistorDocument5 pages3D Trigate TransistorTejas DharaniPas encore d'évaluation

- Static Timing AnalysisDocument71 pagesStatic Timing Analysisapi-3762689100% (13)

- STA AssignmentsDocument3 pagesSTA AssignmentsTejas DharaniPas encore d'évaluation

- PCITarget 33 MHZ 32 Bit DocumentationDocument14 pagesPCITarget 33 MHZ 32 Bit DocumentationTejas DharaniPas encore d'évaluation

- Jay Vasavada's - Best of Best Article Collection by I-Love-GujaratiDocument5 pagesJay Vasavada's - Best of Best Article Collection by I-Love-Gujaratii_love_gujarati83% (6)

- Race Condition in J-K LatchDocument14 pagesRace Condition in J-K LatchTejas DharaniPas encore d'évaluation

- PWMDocument12 pagesPWMTejas DharaniPas encore d'évaluation

- 01 Trends in Embedded Software EngineeringDocument46 pages01 Trends in Embedded Software EngineeringTejas DharaniPas encore d'évaluation

- Door Entry DetectionDocument8 pagesDoor Entry DetectionTejas DharaniPas encore d'évaluation

- StaDocument2 pagesStaTejas DharaniPas encore d'évaluation

- 8051 CoreDocument88 pages8051 CoreTejas DharaniPas encore d'évaluation

- Verilog Interview Questions and AnswersDocument16 pagesVerilog Interview Questions and AnswersAashish AggarwalPas encore d'évaluation

- Static Timing AnalysisDocument71 pagesStatic Timing Analysisapi-3762689100% (13)

- DTMF Using FPGADocument16 pagesDTMF Using FPGATejas DharaniPas encore d'évaluation

- Introduction To Logic Synthesis Using Verilog HDLDocument84 pagesIntroduction To Logic Synthesis Using Verilog HDLritesh_necPas encore d'évaluation

- JBL NewDocument1 pageJBL NewTejas DharaniPas encore d'évaluation

- Awg Cable IntroductionDocument2 pagesAwg Cable IntroductionFrancis LeePas encore d'évaluation

- Experiment #04 To Understand The Operation of Over Current RelayDocument5 pagesExperiment #04 To Understand The Operation of Over Current RelayMuniba FatimaPas encore d'évaluation

- 3 Measurement of Power and Power Factor in 3 Phase CircuitDocument6 pages3 Measurement of Power and Power Factor in 3 Phase Circuitsatishsongs1Pas encore d'évaluation

- Engine Control System 1. General: Engine - 2Tr-Fe Engine EG-31Document32 pagesEngine Control System 1. General: Engine - 2Tr-Fe Engine EG-31Maxi SardiPas encore d'évaluation

- Modi Con 512Document60 pagesModi Con 512Time To Use BrainPas encore d'évaluation

- Types of TransformersDocument7 pagesTypes of TransformersTyron FrancisPas encore d'évaluation

- Dynamic Voltage and Frequency Scaling The Laws ofDocument6 pagesDynamic Voltage and Frequency Scaling The Laws ofQurat AnniePas encore d'évaluation

- Gallien Krueger bl112 Poweramp 206 0151Document17 pagesGallien Krueger bl112 Poweramp 206 0151electromusicworkshopPas encore d'évaluation

- Agriculture Based Saved Wild AnimalsDocument19 pagesAgriculture Based Saved Wild Animalsvenky potlaPas encore d'évaluation

- Simulation of Phasor Measurement Unit (PMU) in MATLAB: January 2015Document5 pagesSimulation of Phasor Measurement Unit (PMU) in MATLAB: January 2015Rajesh GangwarPas encore d'évaluation

- Arduino UnoDocument3 pagesArduino UnoDebi BolePas encore d'évaluation

- L4 Translational Mechanical System PDFDocument33 pagesL4 Translational Mechanical System PDFshahabPas encore d'évaluation

- Handouts EIM. SS1 Week 2Document4 pagesHandouts EIM. SS1 Week 2myco sauraPas encore d'évaluation

- Advances in Analog Circuits PDFDocument380 pagesAdvances in Analog Circuits PDFnskprasad89100% (1)

- Manual Atlas CopcoDocument52 pagesManual Atlas CopcoRobertoSoaresPas encore d'évaluation

- CS6461 - Computer Architecture Fall 2016 Instructor Morris LancasterDocument28 pagesCS6461 - Computer Architecture Fall 2016 Instructor Morris Lancaster闫麟阁Pas encore d'évaluation

- Alex0718 PDUDocument17 pagesAlex0718 PDUDwiki KurniaPas encore d'évaluation

- Night Vision Tech PPT PramodDocument28 pagesNight Vision Tech PPT PramodSampathhhhh Sai Tadepalli100% (1)

- EMI-Signal GeneratorsDocument7 pagesEMI-Signal GeneratorsVineela ThonduriPas encore d'évaluation

- Acer Aspire 5551 Newx5 Pew56Document45 pagesAcer Aspire 5551 Newx5 Pew56nikola1660Pas encore d'évaluation

- Procedure For Electrical WorksDocument13 pagesProcedure For Electrical WorksBenadict JoshuaPas encore d'évaluation

- KSG-1K-SM / KSG-1.5K-SM / KSG-1.9K-SM / KSG-2K-SM KSG 1K SM/KSG 1.5K SM/KSG 1.9K SM/KSG 2K SMDocument2 pagesKSG-1K-SM / KSG-1.5K-SM / KSG-1.9K-SM / KSG-2K-SM KSG 1K SM/KSG 1.5K SM/KSG 1.9K SM/KSG 2K SMBhavik PrajapatiPas encore d'évaluation

- EE2001 Circuit Analysis - OBTLDocument7 pagesEE2001 Circuit Analysis - OBTLAaron TanPas encore d'évaluation

- Protection in 400kvDocument18 pagesProtection in 400kvmanoharmanishPas encore d'évaluation

- Analysis of Series RC Circuit Using MatlabDocument5 pagesAnalysis of Series RC Circuit Using MatlabAbdul MubinPas encore d'évaluation

- Induction Heating Handbook: John Davies Peter SimpsonDocument5 pagesInduction Heating Handbook: John Davies Peter SimpsonOthman Ben Cheikh0% (1)

- en HR RoDocument86 pagesen HR RoGabriel SetnicPas encore d'évaluation

- Septum Polarizers and Feeds: Paul Wade, W1GHZ ©2003Document20 pagesSeptum Polarizers and Feeds: Paul Wade, W1GHZ ©2003Madalin Damaris GaleaPas encore d'évaluation

- Electrom iTIG II Moottorimittauslaitteet - ENGDocument6 pagesElectrom iTIG II Moottorimittauslaitteet - ENGE BuPas encore d'évaluation

- Details Make The Difference: Xlpe Insulated Heavy Duty Cables 650/1100VDocument25 pagesDetails Make The Difference: Xlpe Insulated Heavy Duty Cables 650/1100VlogixPas encore d'évaluation