Académique Documents

Professionnel Documents

Culture Documents

Arsitektur Komputer (Sistem Bus)

Transféré par

Dianne HarrisDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Arsitektur Komputer (Sistem Bus)

Transféré par

Dianne HarrisDroits d'auteur :

Formats disponibles

William Stallings

Computer Organization

and Architecture

6

th

Edition

Chapter 3

System Buses

Program Concept

Hardwired systems are inflexible

General purpose hardware can do different

tasks, given correct control signals

Instead of re-wiring, supply a new set of control

signals

What is a program?

A sequence of steps

For each step, an arithmetic or logical operation

is done

For each operation, a different set of control

signals is needed

Function of Control Unit

For each operation a unique code is provided

e.g. ADD, MOVE

A hardware segment accepts the code and

issues the control signals

Components

The Control Unit and the Arithmetic and Logic

Unit constitute the Central Processing Unit

Data and instructions need to get into the

system and results out

Input/output

Temporary storage of code and results is

needed

Main memory

Computer Components:

Top Level View

Instruction Cycle

Two steps:

Fetch

Execute

Fetch Cycle

Program Counter (PC) holds address of next

instruction to fetch

Processor fetches instruction from memory

location pointed to by PC

Increment PC

Unless told otherwise

Instruction loaded into Instruction Register (IR)

Processor interprets instruction and performs

required actions

Execute Cycle

Processor-memory

data transfer between CPU and main memory

Processor I/O

Data transfer between CPU and I/O module

Data processing

Some arithmetic or logical operation on data

Control

Alteration of sequence of operations

e.g. jump

Combination of above

Example of Program Execution

Instruction Cycle -

State Diagram

Interrupts

Mechanism by which other modules (e.g. I/O) may

interrupt normal sequence of processing

Program

e.g. overflow, division by zero

Timer

Generated by internal processor timer

Used in pre-emptive multi-tasking

I/O

from I/O controller

Hardware failure

e.g. memory parity error

Interrupt Cycle

Added to instruction cycle

Processor checks for interrupt

Indicated by an interrupt signal

If no interrupt, fetch next instruction

If interrupt pending:

Suspend execution of current program

Save context

Set PC to start address of interrupt handler routine

Process interrupt

Restore context and continue interrupted program

Transfer of Control via Interrupts

Instruction Cycle with Interrupts

Instruction Cycle (with Interrupts) -

State Diagram

Multiple Interrupts

Disable interrupts

Processor will ignore further interrupts whilst

processing one interrupt

Interrupts remain pending and are checked after first

interrupt has been processed

Interrupts handled in sequence as they occur

Define priorities

Low priority interrupts can be interrupted by higher

priority interrupts

When higher priority interrupt has been processed,

processor returns to previous interrupt

Multiple Interrupts - Sequential

Multiple Interrupts Nested

Time Sequence of Multiple Interrupts

Connecting

All the units must be connected

Different type of connection for different type of

unit

Memory

Input/Output

CPU

Computer Modules

Memory Connection

Receives and sends data

Receives addresses (of locations)

Receives control signals

Read

Write

Timing

Input/Output Connection(1)

Similar to memory from computers viewpoint

Output

Receive data from computer

Send data to peripheral

Input

Receive data from peripheral

Send data to computer

Input/Output Connection(2)

Receive control signals from computer

Send control signals to peripherals

e.g. spin disk

Receive addresses from computer

e.g. port number to identify peripheral

Send interrupt signals (control)

CPU Connection

Reads instruction and data

Writes out data (after processing)

Sends control signals to other units

Receives (& acts on) interrupts

Buses

There are a number of possible interconnection

systems

Single and multiple BUS structures are most

common

e.g. Control/Address/Data bus (PC)

e.g. Unibus (DEC-PDP)

What is a Bus?

A communication pathway connecting two or

more devices

Often grouped

A number of channels in one bus

e.g. 32 bit data bus is 32 separate single bit channels

Data Bus

Carries data

Remember that there is no difference between data

and instruction at this level

Width is a key determinant of performance

8, 16, 32, 64 bit

Address bus

Identify the source or destination of data

e.g. CPU needs to read an instruction (data)

from a given location in memory

Bus width determines maximum memory

capacity of system

e.g. 8080 has 16 bit address bus giving 64k address

space

Control Bus

Control and timing information

Memory read/write signal

Interrupt request

Clock signals

Bus Interconnection Scheme

Big and Yellow?

What do buses look like?

Parallel lines on circuit boards

Ribbon cables

Strip connectors on mother boards

e.g. PCI

Sets of wires

Single Bus Problems

Lots of devices on one bus leads to:

Propagation delays

Long data paths mean that co-ordination of bus use can

adversely affect performance

If aggregate data transfer approaches bus capacity

Most systems use multiple buses to overcome

these problems

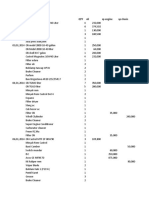

Traditional (ISA)

(with cache)

High Performance Bus

Bus Types

Dedicated

Separate data & address lines

Multiplexed

Shared lines

Address valid or data valid control line

Advantage - fewer lines

Disadvantages

More complex control

Ultimate performance

Bus Arbitration

More than one module controlling the bus

e.g. CPU and DMA controller

Only one module may control bus at one time

Arbitration may be centralised or distributed

Centralised Arbitration

Single hardware device controlling bus access

Bus Controller

Arbiter

May be part of CPU or separate

Distributed Arbitration

Each module may claim the bus

Control logic on all modules

Timing

Co-ordination of events on bus

Synchronous

Events determined by clock signals

Control Bus includes clock line

A single 1-0 is a bus cycle

All devices can read clock line

Usually sync on leading edge

Usually a single cycle for an event

Synchronous Timing Diagram

Asynchronous Timing Read Diagram

Asynchronous Timing Write Diagram

PCI Bus

Peripheral Component Interconnection

Intel released to public domain

32 or 64 bit

50 lines

PCI Bus Lines (required)

Systems lines

Including clock and reset

Address & Data

32 time mux lines for address/data

Interrupt & validate lines

Interface Control

Arbitration

Not shared

Direct connection to PCI bus arbiter

Error lines

PCI Bus Lines (Optional)

Interrupt lines

Not shared

Cache support

64-bit Bus Extension

Additional 32 lines

Time multiplexed

2 lines to enable devices to agree to use 64-bit

transfer

Boundary Scan

For testing procedures

PCI Commands

Transaction between initiator (master) and

target

Master claims bus

Determine type of transaction

e.g. I/O read/write

Address phase

One or more data phases

PCI Read Timing Diagram

PCI Bus Arbitration

Foreground Reading

Stallings, chapter 3 (all of it)

www.pcguide.com/ref/mbsys/buses/

In fact, read the whole site!

www.pcguide.com/

Vous aimerez peut-être aussi

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- A Top-Level View of Computer Function and InterconnectionDocument56 pagesA Top-Level View of Computer Function and InterconnectionVERY YOGA MARULI TUA SIHOMBING TBAPas encore d'évaluation

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument54 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesNiloy RahmanPas encore d'évaluation

- System Buses ExplainedDocument54 pagesSystem Buses ExplainedAhmed Hassan MohammedPas encore d'évaluation

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument58 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesDr-Raghad Al-FahamPas encore d'évaluation

- William Stallings Computer Architecture 8 Edition: Top Level View of Computer Function and InterconnectionDocument55 pagesWilliam Stallings Computer Architecture 8 Edition: Top Level View of Computer Function and Interconnectionmeriem bahaPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument55 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusespuyPas encore d'évaluation

- Computer Buses and InterconnectionDocument55 pagesComputer Buses and InterconnectionMuhammad WildanPas encore d'évaluation

- Part 04: Designing For Performance: Prof. Aaradhana DeshmukhDocument55 pagesPart 04: Designing For Performance: Prof. Aaradhana Deshmukhmadhursen99Pas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 EditionDocument55 pagesWilliam Stallings Computer Organization and Architecture 7 EditionAthreyaPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument55 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesLeandro MansillaPas encore d'évaluation

- 03 - Top Level View of Computer Function and InterconnectionDocument50 pages03 - Top Level View of Computer Function and Interconnectiondommy omosaPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 EditionDocument47 pagesWilliam Stallings Computer Organization and Architecture 7 EditionMeena ShahPas encore d'évaluation

- Ch3 PDFDocument62 pagesCh3 PDFtesfu zewduPas encore d'évaluation

- Computer Organization and Architecture Chapter 3 Top Level View SummaryDocument62 pagesComputer Organization and Architecture Chapter 3 Top Level View SummaryMD. MAHIR ABRAR KHANPas encore d'évaluation

- El ProcesadorDocument58 pagesEl ProcesadorCarlos Jesus Koo LabrinPas encore d'évaluation

- Computer Architecture and OrganizationDocument61 pagesComputer Architecture and OrganizationPoornima EgPas encore d'évaluation

- 3 BusesDocument61 pages3 BusesPuso MoletaPas encore d'évaluation

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument55 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesHassan MansoorPas encore d'évaluation

- BusesDocument55 pagesBusesWajahat HussainPas encore d'évaluation

- 03 - Top Level View of Computer Function and InterconnectionDocument55 pages03 - Top Level View of Computer Function and Interconnectionjanray1988Pas encore d'évaluation

- Top Level View of Computer Components and Bus ArchitectureDocument44 pagesTop Level View of Computer Components and Bus ArchitectureMAHNOOR ATIFPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument40 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesUsman khanPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument39 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesMurtaza JamaliPas encore d'évaluation

- LectureSeries3 - BusesDocument19 pagesLectureSeries3 - BusesLamar ArnoldPas encore d'évaluation

- 03N - Top Level View of Computer Function and InterconnectionDocument38 pages03N - Top Level View of Computer Function and InterconnectionDoc TelPas encore d'évaluation

- ECEG-3202 Computer Architecture and Organization: Top Level View of Computer Function and InterconnectionDocument36 pagesECEG-3202 Computer Architecture and Organization: Top Level View of Computer Function and InterconnectionESTIFANOS NegaPas encore d'évaluation

- Computer Architecture Top Level ViewDocument36 pagesComputer Architecture Top Level Viewδιρορα δρPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument47 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesAjmal KhanPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition System BusesDocument50 pagesWilliam Stallings Computer Organization and Architecture 7 Edition System BusesRubeshan ShanPas encore d'évaluation

- 03 - Top Level View of Computer Function and InterconnectionDocument32 pages03 - Top Level View of Computer Function and InterconnectionflowrentsiaPas encore d'évaluation

- A Top-Level View of Computer Function and InterconnectionDocument61 pagesA Top-Level View of Computer Function and InterconnectionBisma NusaPas encore d'évaluation

- Top Level View of Computer Function and InterconnectionDocument62 pagesTop Level View of Computer Function and InterconnectionAhsan JameelPas encore d'évaluation

- William Stallings Computer Organization and Architecture 8 EditionDocument52 pagesWilliam Stallings Computer Organization and Architecture 8 EditionabbasPas encore d'évaluation

- Buses and InterconnectionDocument32 pagesBuses and Interconnectionather_88100% (1)

- Introduction To ComputerDocument47 pagesIntroduction To ComputerPradhyumn ShetTilvePas encore d'évaluation

- Top Level View of Computer Function and InterconnectionDocument64 pagesTop Level View of Computer Function and Interconnectionbree789Pas encore d'évaluation

- Sytem BusDocument24 pagesSytem BusRam RamPas encore d'évaluation

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument34 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesShakeel AwanPas encore d'évaluation

- Computer Architecture and Organization (Eeng 3192)Document34 pagesComputer Architecture and Organization (Eeng 3192)Esuyawkal AdugnaPas encore d'évaluation

- CH 03 p2 BusStructureDocument37 pagesCH 03 p2 BusStructureAnanda Haykel IskandarPas encore d'évaluation

- Coa 03 Function InterconnectionDocument61 pagesCoa 03 Function Interconnectionmuhammad farooqPas encore d'évaluation

- Top Level View of Computer Components and Instruction CycleDocument74 pagesTop Level View of Computer Components and Instruction CycleDagmawiPas encore d'évaluation

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument29 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesPritam SirpotdarPas encore d'évaluation

- William Stallings Computer Organization and Architecture 8 Edition Input/OutputDocument63 pagesWilliam Stallings Computer Organization and Architecture 8 Edition Input/Outputtesos ganulPas encore d'évaluation

- 07 Input OutputDocument63 pages07 Input Outputdeepak joshiPas encore d'évaluation

- William Stallings Computer Organization and Architecture 7 Edition Input/OutputDocument63 pagesWilliam Stallings Computer Organization and Architecture 7 Edition Input/OutputAndi Didik Wira PutraPas encore d'évaluation

- Week 3 18032022 040218pmDocument47 pagesWeek 3 18032022 040218pmmisbah AbidPas encore d'évaluation

- William Stallings Computer Organization and Architecture 8 Edition Input/OutputDocument65 pagesWilliam Stallings Computer Organization and Architecture 8 Edition Input/OutputUmar IftikharPas encore d'évaluation

- 07 Input OutputDocument63 pages07 Input OutputJuNaid QaimkhaniPas encore d'évaluation

- William Stallings Computer Organization and Architecture 8 EditionDocument55 pagesWilliam Stallings Computer Organization and Architecture 8 EditionflowrentsiaPas encore d'évaluation

- 07 - Input OutputDocument62 pages07 - Input OutputAbdukadir AbdullahPas encore d'évaluation

- Computer Architecture: Von Neumann ModelDocument28 pagesComputer Architecture: Von Neumann ModelDevan KaladharanPas encore d'évaluation

- Lesson 3 - Top Level View of Computer Function and InterconnectionDocument74 pagesLesson 3 - Top Level View of Computer Function and InterconnectionParadise TheKingPas encore d'évaluation

- Computer Organization and ArchitectureDocument52 pagesComputer Organization and ArchitectureMohammad Hussain AfridiPas encore d'évaluation

- Lecture-03, Adv. Computer Architecture, CS-522Document62 pagesLecture-03, Adv. Computer Architecture, CS-522torabgullPas encore d'évaluation

- Chapter 03 Computer Function InterconnectionDocument44 pagesChapter 03 Computer Function InterconnectionALEMU DEMIRACHEWPas encore d'évaluation

- SEEPZ Special Economic ZoneDocument2 pagesSEEPZ Special Economic ZonetarachandmaraPas encore d'évaluation

- Embedded Systems: Martin Schoeberl Mschoebe@mail - Tuwien.ac - atDocument27 pagesEmbedded Systems: Martin Schoeberl Mschoebe@mail - Tuwien.ac - atDhirenKumarGoleyPas encore d'évaluation

- MT R 108 000 0 000000-0 DHHS B eDocument68 pagesMT R 108 000 0 000000-0 DHHS B eRafal WojciechowskiPas encore d'évaluation

- 1 N 2Document327 pages1 N 2Muhammad MunifPas encore d'évaluation

- Capran+980 CM en PDFDocument1 pageCapran+980 CM en PDFtino taufiqul hafizhPas encore d'évaluation

- Why Companies Choose Corporate Bonds Over Bank LoansDocument31 pagesWhy Companies Choose Corporate Bonds Over Bank Loansতোফায়েল আহমেদPas encore d'évaluation

- Career Guidance Activity Sheet For Grade IiDocument5 pagesCareer Guidance Activity Sheet For Grade IiJayson Escoto100% (1)

- RS-RA-N01-AL User Manual of Photoelectric Total Solar Radiation TransmitterDocument11 pagesRS-RA-N01-AL User Manual of Photoelectric Total Solar Radiation TransmittermohamadPas encore d'évaluation

- Department of Education: Republic of The PhilippinesDocument3 pagesDepartment of Education: Republic of The PhilippinesAdonis BesaPas encore d'évaluation

- Denys Vuika - Electron Projects - Build Over 9 Cross-Platform Desktop Applications From Scratch-Packt Publishing (2019)Document429 pagesDenys Vuika - Electron Projects - Build Over 9 Cross-Platform Desktop Applications From Scratch-Packt Publishing (2019)Sarthak PrakashPas encore d'évaluation

- SINGGAR MULIA ENGINEERING HORIZONTAL 2-PHASE SEPARATORDocument3 pagesSINGGAR MULIA ENGINEERING HORIZONTAL 2-PHASE SEPARATORElias EliasPas encore d'évaluation

- Air Cycle Refrigeration:-Bell - Coleman CycleDocument21 pagesAir Cycle Refrigeration:-Bell - Coleman CycleSuraj Kumar100% (1)

- 63db2cf62042802 Budget Eco SurveyDocument125 pages63db2cf62042802 Budget Eco SurveyNehaPas encore d'évaluation

- Request For AffidavitDocument2 pagesRequest For AffidavitGhee MoralesPas encore d'évaluation

- Nuxeo Platform 5.6 UserGuideDocument255 pagesNuxeo Platform 5.6 UserGuidePatrick McCourtPas encore d'évaluation

- Schedule of Charges General Banking 2022Document18 pagesSchedule of Charges General Banking 2022Shohag MahmudPas encore d'évaluation

- Javascript: What You Should Already KnowDocument6 pagesJavascript: What You Should Already KnowKannan ParthasarathiPas encore d'évaluation

- Gigahertz company background and store locationsDocument1 pageGigahertz company background and store locationsjay BearPas encore d'évaluation

- IT support tips for non-tech colleaguesDocument7 pagesIT support tips for non-tech colleaguesLeo KrekPas encore d'évaluation

- James Ashmore - Curriculum VitaeDocument2 pagesJames Ashmore - Curriculum VitaeJames AshmorePas encore d'évaluation

- Maximizing Revenue of IT Project DevelopmentDocument4 pagesMaximizing Revenue of IT Project DevelopmentJulius Mark CerrudoPas encore d'évaluation

- Lenex 3.0 Technical DocumentationDocument31 pagesLenex 3.0 Technical DocumentationGalina DPas encore d'évaluation

- University Assignment Report CT7098Document16 pagesUniversity Assignment Report CT7098Shakeel ShahidPas encore d'évaluation

- United States Court of Appeals, Third CircuitDocument3 pagesUnited States Court of Appeals, Third CircuitScribd Government DocsPas encore d'évaluation

- Cantilever Retaining Wall AnalysisDocument7 pagesCantilever Retaining Wall AnalysisChub BokingoPas encore d'évaluation

- User-Centered Website Development: A Human-Computer Interaction ApproachDocument24 pagesUser-Centered Website Development: A Human-Computer Interaction ApproachKulis KreuznachPas encore d'évaluation

- TransformerDocument50 pagesTransformerبنیاد پرست100% (8)

- BCM Risk Management and Compliance Training in JakartaDocument2 pagesBCM Risk Management and Compliance Training in Jakartaindra gPas encore d'évaluation

- A Research About The Canteen SatisfactioDocument50 pagesA Research About The Canteen SatisfactioJakeny Pearl Sibugan VaronaPas encore d'évaluation

- MSDS Metafuron 20 WPDocument10 pagesMSDS Metafuron 20 WPAndi DarmawanPas encore d'évaluation