Académique Documents

Professionnel Documents

Culture Documents

Digital Integrated Circuits © Prentice Hall 1995 Design Methodologies

Transféré par

Khadar BashaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Digital Integrated Circuits © Prentice Hall 1995 Design Methodologies

Transféré par

Khadar BashaDroits d'auteur :

Formats disponibles

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Design

Methodologies

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

The Design Problem

Source: sematech97

A growing gap between design complexity and design productivity

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Design Methodology

Design process traverses iteratively between three abstractions:

behavior, structure, and geometry

More and more automation for each of these steps

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Design Analysis and Verification

Accounts for largest fraction of design time

More efficient when done at higher levels of

abstraction - selection of correct analysis

level can account for multiple orders of

magnitude in verification time

Two major approaches:

Simulation

Verification

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Digital Data treated as Analog Signal

V

o

u

t

(

V

)

5.0

3.0

1.0

1.0

t (nsec)

2 1.5 1 0. 5 0

Vin Vout

t pHL

Gn,p

In Out

VDD

Bp

Bn

Dn,p

Sn

Sp

Circuit Simulation

Both Time and Data treated as Analog Quantities

Also complicated by presence of non-linear elements

(relaxed in timing simulation)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Representing Data as Discrete Entity

V

t

V

M

t

1

t

2

0 1 0 V

DD

R

n

R

p

C

L

Discretizing the data using

switching threshold

The linear switch model

of the inverter

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Circuit versus Switch-Level Simulation

0 5 10 15 20

time (nsec)

1.0

1.0

3.0

5.0

CI N

OUT[3]

OUT[2]

C

i

r

c

u

i

t

S

w

i

t

c

h

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Structural Description of Accumulator

entity accumulator is

port ( --

definition of input and output terminals

DI: in bit_vector(15 downto 0) --

a vector of 16 bit wide

DO: inout bit_vector(15 downto 0);

CLK: in bit

);

end accumulator;

architecture structure of accumulator is

component reg --

definition of register ports

port (

DI : in bit_vector(15 downto 0);

DO : out bit_vector(15 downto 0);

CLK : in bit

);

end component;

component add --

definition of adder ports

port (

IN0 : in bit_vector(15 downto 0);

IN1 : in bit_vector(15 downto 0);

OUT0 : out bit_vector(15 downto 0)

);

end component;

--

definition of accumulator structure

signal X : bit_vector(15 downto 0);

begin

add1 : add

port map (DI, DO, X); --

defines port connectivity

reg1 : reg

port map (X, DO, CLK);

end structure;

Design defined as composition of

register and full-adder cells (netlist)

Data represented as {0,1,Z}

Time discretized and progresses with

unit steps

Description language: VHDL

Other options: schematics, Verilog

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Behavioral Description of Accumulator

entity accumulator is

port (

DI : in integer;

DO : inout integer := 0;

CLK : in bit

);

end accumulator;

architecture behavior of accumulator is

begin

process(CLK)

variable X : integer := 0; --

intermediate variable

begin

if CLK = '1' then

X <= DO + D1;

DO <= X;

end if;

end process;

end behavior;

Design described as set of input-output

relations, regardless of chosen

implementation

Data described at higher abstraction

level (integer)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Behavioral simulation of accumulator

Integer data

Discrete time

(Synopsys Waves display tool)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Timing Verification

(Synopsys-Epic Pathmill)

Critical path

Enumerates and rank

orders critical timing paths

No simulation needed!

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Issues in Timing Verification

bypass

4-bit adder

M

U

X

Out

In

False Timing Paths

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Implementation Methodologies

Digital Circuit Implementation Approaches

Custom

Semi-custom

Cell-Based

Array-Based

Standard Cells

Macro Cells Pre-diffused Pre-wired

(FPGA)

Compiled Cells

(Gate Arrays)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Custom Design

Layout Editor

Magic Layout Editor

(UC Berkeley)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Symbolic Layout

1

3

In

Out

V

DD

GND

Stick diagram of inverter

Dimensionless layout entities

Only topology is important

Final layout generated by

compaction program

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Cell-based Design (or standard cells)

Functional

Module

(RAM,

multiplier, )

R

o

w

s

o

f

C

e

l

l

s

Logic Cell

Routing

Channel

Feedthrough Cell

Routing channel

requirements are

reduced by presence

of more interconnect

layers

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Standard Cell Example

[Brodersen92]

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Standard Cell - Example

3-input NAND cell

(from Mississippi State Library)

characterized for fanout of 4 and

for three different technologies

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Automatic Cell Generation

Random-logic layout

generated by CLEO

cell compiler (Digital)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Module Generators

Compiled Datapath

a

d

d

e

r

b

u

f

f

e

r

r

e

g

0

r

e

g

1

m

u

x

bus0

bus2

bus1

bit-slice

routing area

feed-through

Advantages: One-dimensional placement/routing problem

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Macrocell Design Methodology

Macrocell

Interconnect Bus

Routing Channel

Floorplan:

Defines overall

topology of design,

relative placement of

modules, and global

routes of busses,

supplies, and clocks

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Macrocell-Based Design

Example

Video-encoder chip

[Brodersen92]

SRAM

SRAM

Data paths

Standard cells

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Gate Array Sea-of-gates

rows of

cells

routing

channel

uncommitted

VDD

GND

polysilicon

metal

possible

contact

In1 In2 In3 In4

Out

Uncommited

Cell

Committed

Cell

(4-input NOR)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Sea-of-gate Primitive Cells

NMOS

PMOS

Oxide-isolation

PMOS

NMOS

NMOS

Using oxide-isolation Using gate-isolation

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Sea-of-gates

Random Logic

Memory

Subsystem

LSI Logic LEA300K

(0.6 mm CMOS)

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Prewired Arrays

Categories of prewired arrays (or field-

programmable devices):

Fuse-based (program-once)

Non-volatile EPROM based

RAM based

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Programmable Logic Devices

PLA PROM

PAL

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

EPLD Block Diagram

Macrocell

Courtesy Altera Corp.

Primary inputs

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Field-Programmable Gate Arrays

Fuse-based

I/O Buffers

Program/Test/Diagnostics

I/O Buffers

I

/

O

B

u

f

f

e

r

s

I

/

O

B

u

f

f

e

r

s

Vertical routes

Rows of logic modules

Routing channels

Standard-cell like

floorplan

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Interconnect

Cell

Horizontal

tracks

Vertical tracks

Input/output pin

Antifuse

Programmed interconnection

Programming interconnect using anti-fuses

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Field-Programmable Gate Arrays

RAM-based

CLB CLB

CLB

CLB

switching matrix

Horizontal

routing

channel

Vertical routing channel

Interconnect point

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

RAM-based FPGA

Basic Cell (CLB)

R

Q1 D

CE

R

Q2 D

CE

F

G

F

G

F

G

R

D

in

Clock

CE

F

G

A

B/Q1/Q2

C/Q1/Q2

D

A

B/Q1/Q2

C/Q1/Q2

D

E

Combinational logic Storage elements

Any function of up t o

4 variables

Any function of up t o

4 variables

Courtesy of Xilinx

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

RAM-based FPGA

Xilinx XC4025

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Taxonomy of Synthesis Tasks

Architectural Level Logic Level Circuit Level

B

e

h

a

v

i

o

r

a

l

V

i

e

w

S

t

r

u

c

t

u

r

a

l

V

i

e

w

Architecture

Synthesis

Logic

Synthesis

Circuit

Synthesis

0

1

3

2

state

(i: 1..16) ::

sum = sum*z

1

+

coeff[i]*In*z

1

a

b

c

x

a

b

c

1

2

2

4

t

p

a

b

c

x

D

mem

*

fsm

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Design

for Test

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Validation and Test of

Manufactured Circuits

Components of DFT strategy

Provide circuitry to enable test

Provide test patterns that guarantee reasonable

coverage

Goals of Design-for-Test (DFT)

Make testing of manufactured part swift and

comprehensive

DFT Mantra

Provide controllability and observability

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Test Classification

Diagnostic test

used in chip/board debugging

defect localization

go/no go or production test

Used in chip production

Parametric test

x e [v,i] versus x e [0,1]

check parameters such as NM, V

t

, t

p

, T

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Design for Testability

M state regs

N inputs

K outputs

K outputs N inputs

Combinational

Logic

Module

Combinational

Logic

Module

(a) Combinational function

(b) Sequential engine

2

N

patterns 2

N+M

patterns

Exhaustive test is impossible or unpractical

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Problem:

Controllability/Observability

Combinational Circuits:

controllable and observable - relatively easy to

determine test patterns

Sequential Circuits: State!

Turn into combinational circuits or use self-test

Memory: requires complex patterns

Use self-test

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Test Approaches

Ad-hoc testing

Scan-based Test

Self-Test

Problem is getting harder

increasing complexity and heterogeneous

combination of modules in system-on-a-chip.

Advanced packaging and assembly techniques

extend problem to the board level

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Generating and Validating

Test-Vectors

Automatic test-pattern generation (ATPG)

for given fault, determine excitation vector (called test vector)

that will propagate error to primary (observable) output

majority of available tools: combinational networks only

sequential ATPG available from academic research

Fault simulation

determines test coverage of proposed test-vector set

simulates correct network in parallel with faulty networks

Both require adequate models of faults in

CMOS integrated circuits

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Fault Models

0

1

sa0

sa1

(output)

(input)

Most Popular - Stuck - at model

x1

x2

x3

Z

, : x1 sa1

: x1 sa0 or

x2 sa0

: Z sa1

Covers almost all (other)

occurring faults, such as

opens and shorts.

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Problem with stuck-at model:

CMOS open fault

x1

x2

x1

x2

Z

Sequential effect

Needs two vectors to ensure detection!

Other options: use stuck-open or stuck-short models

This requires fault-simulation and analysis at the switch or

transistor level - Very expensive!

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Problem with stuck-at model:

CMOS short fault

0

0

0

1

C

A B

D

A

B

C

D

Causes short circuit between

Vdd and GND for A=C=0, B=1

Possible approach:

Supply Current Measurement (IDDQ)

but: not applicable for gigascale

integration

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Path Sensitization

Out

Techniques Used: D-algorithm, Podem

Goals: Determine input pattern that makes a fault

controllable (triggers the fault, and makes its impact

visible at the output nodes)

sa0

1

1

0

1

1

1

0

1

Fault propagation

Fault enabling

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Ad-hoc Test

Inserting multiplexer improves testability

I/O bus

Memory

Processor

d

a

t

a

a

d

d

r

e

s

s

I/O bus

Memory

Processor

d

a

t

a

a

d

d

r

e

s

s

select

test

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Scan-based Test

Logic

Combinational

Logic

Combinational

R

e

g

i

s

t

e

r

R

e

g

i

s

t

e

r

Out

In

ScanOut

ScanIn

A B

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Polarity-Hold SRL

(Shift-Register Latch)

Introduced at IBM and set as company policy

System Data

System Clock

Scan Data

Shift A Clock

D

C

SI

A

L1

L2

Shift B Clock

B

Q

Q

SO

SO

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Scan-Path Register

SCANIN

IN

LOAD

SCAN PHI2 PHI1

KEEP

OUT

SCANOUT

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Scan-based Test Operation

Test

ScanIn

Test

Latch

In

0

Out

0

Test Test

Latch

In

1

Out

1

Test Test

Latch

In

2

Out

2

Test Test

Latch

In

3

Out

3

ScanOut

Test

2

N cycles

1 cycle

evaluation

scan-in

N cycles

scan-out

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Scan-Path Testing

Partial-Scan can be more effective for pipelined datapaths

REG[5]

REG[4]

REG[3] REG[2]

REG[0] REG[1]

+

COMP

OUT

SCANIN

COMPIN

SCANOUT

A B

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Boundary Scan (JTAG)

Printed-circuit board

Logic

scan path

n

o

r

m

a

l

i

n

t

e

r

c

o

n

n

e

c

t

Packaged IC

Bonding Pad

Scan-in

Scan-out

si so

Board testing becomes as problematic as chip testing

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Self-test

(Sub)-Circuit

Under

Test

Stimulus Generator Response Analyzer

Test Controller

Rapidly becoming more important with increasing

chip-complexity and larger modules

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Linear-Feedback Shift Register (LFSR)

S

0

S

1

S

2

R R R

1 0 0

0 1 0

1 0 1

1 1 0

1 1 1

0 1 1

0 0 1

1 0 0

Pseudo-Random Pattern Generator

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Signature Analysis

R

Counter

In

Counts transitions on single-bit stream

Compression in time

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

BILBO

S0

R R R

S1 S2

ScanOut ScanIn

m

u

x

D2 D1 D0

B0

B1

Operation mode B

0

Normal

Scan

Signature analysis

1 1

0 0

1 0

Pattern generation or

0 1 Reset

B

1

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

BILBO Application

Logic

Combinational

Logic

Combinational

B

I

L

B

O

-

B

B

I

L

B

O

-

A Out

In

ScanIn ScanOut

Digital Integrated Circuits Prentice Hall 1995 Design Methodologies

Memory Self-Test

FSM

Memory Signature

Analysis

Under Test

data

address &

R/W control

-in

data-out

Patterns: Writing/Reading 0s, 1s,

Walking 0s, 1s

Galloping 0s, 1s

Vous aimerez peut-être aussi

- Design For Test: Digital Integrated Circuits © Prentice Hall 1995 Design MethodologiesDocument24 pagesDesign For Test: Digital Integrated Circuits © Prentice Hall 1995 Design Methodologiesanand_duraiswamyPas encore d'évaluation

- System Design and Modeling With SimulinkDocument0 pageSystem Design and Modeling With SimulinkSharmila ChowdhuriPas encore d'évaluation

- Vlsi TechnologyDocument60 pagesVlsi TechnologyPrasad NagavaraPas encore d'évaluation

- 08.546 DSD With VHDL Lecture Notes - Module 1Document70 pages08.546 DSD With VHDL Lecture Notes - Module 1Assini Hussain100% (1)

- Efficiently Triggering Debugging and Decoding Low-Speed Serial BusesDocument19 pagesEfficiently Triggering Debugging and Decoding Low-Speed Serial BusesVipin JainPas encore d'évaluation

- Digital Systems Verification: Alessandra NardiDocument29 pagesDigital Systems Verification: Alessandra NardiNaushad SheikPas encore d'évaluation

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranPas encore d'évaluation

- Unit 5 - DFT - E&iDocument79 pagesUnit 5 - DFT - E&inithyadecePas encore d'évaluation

- Communication Radar Systems Design and SimulationDocument89 pagesCommunication Radar Systems Design and SimulationAbdulrahman BastaPas encore d'évaluation

- Analog Design Methodology Jnotor r3Document17 pagesAnalog Design Methodology Jnotor r3Manjunath ReddyPas encore d'évaluation

- PLTS 2014Document25 pagesPLTS 2014cgrachanenPas encore d'évaluation

- Summer Training VHDLDocument38 pagesSummer Training VHDLmjcetpaPas encore d'évaluation

- System On Chip Design and ModellingDocument131 pagesSystem On Chip Design and ModellingGurram KishorePas encore d'évaluation

- DSD ReportDocument14 pagesDSD Report22051774Pas encore d'évaluation

- Advanced Technologies Development Center Microelectronics & Nanotechology laboratory Design Kit Development Project TeamDocument21 pagesAdvanced Technologies Development Center Microelectronics & Nanotechology laboratory Design Kit Development Project TeamAmel ChPas encore d'évaluation

- Introduction To Field Programmable Gate Arrays: Lecture 1/3Document29 pagesIntroduction To Field Programmable Gate Arrays: Lecture 1/3Sandeep ChaudharyPas encore d'évaluation

- Design Examples-Digital System Designs and Practices Using Verilog HDL and FPGAsDocument69 pagesDesign Examples-Digital System Designs and Practices Using Verilog HDL and FPGAsyamaha640Pas encore d'évaluation

- Generating Optimizing and Verifying HDL Code With Matlab and SimulinkDocument46 pagesGenerating Optimizing and Verifying HDL Code With Matlab and Simulinkkpkarthi80Pas encore d'évaluation

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaPas encore d'évaluation

- Sam Palermo TAMU High Speed IODocument18 pagesSam Palermo TAMU High Speed IOmansoor110Pas encore d'évaluation

- Digital Integrated Circuits - A Design Perspective 2/e: Reference Chapter: 11Document3 pagesDigital Integrated Circuits - A Design Perspective 2/e: Reference Chapter: 11DarwinPas encore d'évaluation

- VHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIDocument23 pagesVHDL Come Strumento Di Progettazione Per Circuiti Digitali VLSIunibfePas encore d'évaluation

- Optimize Digital Design SynthesisDocument41 pagesOptimize Digital Design SynthesisFeroz AhmedPas encore d'évaluation

- Ds First LatestDocument31 pagesDs First LatestZohaib KhanPas encore d'évaluation

- Unit 3 DSDDocument107 pagesUnit 3 DSDGuru VelmathiPas encore d'évaluation

- CmosDocument23 pagesCmoselumalaianithaPas encore d'évaluation

- Digital IC Implementation Strategies OutlineDocument18 pagesDigital IC Implementation Strategies OutlineRajesh BathijaPas encore d'évaluation

- Static Timing Analysis Static Timing AnalysisDocument49 pagesStatic Timing Analysis Static Timing AnalysisRajesh DurisalaPas encore d'évaluation

- MATLAB Simulink For Engineering EducationDocument32 pagesMATLAB Simulink For Engineering EducationKalyan GovindarajanPas encore d'évaluation

- SoC Design and Modelling Lecture NotesDocument131 pagesSoC Design and Modelling Lecture NotesSambhav VermanPas encore d'évaluation

- Electronics in High Energy Physic: Field Programmable Gate ArraysDocument37 pagesElectronics in High Energy Physic: Field Programmable Gate Arraysبلال ناجي الميسPas encore d'évaluation

- Synthesizable VHDL Slides AyonDocument39 pagesSynthesizable VHDL Slides AyonSreeja DasPas encore d'évaluation

- Flexible OFDM Signal Generation, Analysis and TroubleshootingDocument70 pagesFlexible OFDM Signal Generation, Analysis and Troubleshootingkeethu8Pas encore d'évaluation

- Cmos Design MethodsDocument69 pagesCmos Design MethodsPuneet PatilPas encore d'évaluation

- Ece260b w05 Design StyleDocument57 pagesEce260b w05 Design StyleHarish KumarPas encore d'évaluation

- Verilog AMS TutorialDocument29 pagesVerilog AMS TutorialSiva KrishnaPas encore d'évaluation

- Introduction To Hardware Description LanguageDocument5 pagesIntroduction To Hardware Description LanguageMallik KglPas encore d'évaluation

- CVCVCDocument20 pagesCVCVCChristopher MckinneyPas encore d'évaluation

- Introduction to Digital Design MethodologyDocument22 pagesIntroduction to Digital Design MethodologySibtain Ul HassanPas encore d'évaluation

- 28nm Silicon and Design Enablement The Foundry and EDA Vendor PerspectiveDocument31 pages28nm Silicon and Design Enablement The Foundry and EDA Vendor Perspectiveswathikomati7870Pas encore d'évaluation

- PrimeTime SlidesDocument47 pagesPrimeTime SlidesRamakrishnaRao SoogooriPas encore d'évaluation

- LT SpiceDocument39 pagesLT SpiceKot FarePas encore d'évaluation

- Iscug 2013 Hls TutorialDocument96 pagesIscug 2013 Hls TutorialLiu WenPas encore d'évaluation

- Introduction to Verilog HDLDocument42 pagesIntroduction to Verilog HDLMichael SohanlallPas encore d'évaluation

- L5 - Combinational Logic Design With VerilogDocument17 pagesL5 - Combinational Logic Design With VerilogYogen SharmaPas encore d'évaluation

- System On Chip Design and Modelling: University of Cambridge Computer Laboratory Lecture NotesDocument144 pagesSystem On Chip Design and Modelling: University of Cambridge Computer Laboratory Lecture Notesgkk001Pas encore d'évaluation

- Wcdma: - IMT-2000 Requirements - WCDMA System - Multiservice ConceptsDocument27 pagesWcdma: - IMT-2000 Requirements - WCDMA System - Multiservice ConceptsSahar SadeghiPas encore d'évaluation

- SR PSpice SimulationDocument11 pagesSR PSpice SimulationMark Chow Khoon KeatPas encore d'évaluation

- VLSI Design - EDA TOOLS PDFDocument83 pagesVLSI Design - EDA TOOLS PDFprathap_somaPas encore d'évaluation

- 2 Front To Back MMIC Design Flow With ADSDocument65 pages2 Front To Back MMIC Design Flow With ADSSAMPas encore d'évaluation

- Vijay Kumar Physical Design EngineerDocument3 pagesVijay Kumar Physical Design EngineerKarthik VarmaPas encore d'évaluation

- Introduction to IC Design and HDL in 40 CharactersDocument38 pagesIntroduction to IC Design and HDL in 40 CharactersSebastian KarlPas encore d'évaluation

- Practical Design of Digital Circuits: Basic Logic to MicroprocessorsD'EverandPractical Design of Digital Circuits: Basic Logic to MicroprocessorsÉvaluation : 4.5 sur 5 étoiles4.5/5 (2)

- Microprocessor System Design: A Practical IntroductionD'EverandMicroprocessor System Design: A Practical IntroductionPas encore d'évaluation

- Millimeter-Wave Digitally Intensive Frequency Generation in CMOSD'EverandMillimeter-Wave Digitally Intensive Frequency Generation in CMOSPas encore d'évaluation

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- 12345Document3 pages12345Khadar BashaPas encore d'évaluation

- 1234Document3 pages1234Khadar BashaPas encore d'évaluation

- Desktop-A19L7Cl 201a0693306fDocument1 pageDesktop-A19L7Cl 201a0693306fKhadar BashaPas encore d'évaluation

- TimerDocument8 pagesTimerKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Instrumentation Amplifier Circuit GainDocument2 pagesInstrumentation Amplifier Circuit GainKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- 123Document2 pages123Khadar BashaPas encore d'évaluation

- TimerDocument8 pagesTimerKhadar BashaPas encore d'évaluation

- SysDocument4 pagesSysKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Instrumentation amplifier circuit gainDocument1 pageInstrumentation amplifier circuit gainKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Instrumentation Amplifier Circuit GainDocument2 pagesInstrumentation Amplifier Circuit GainKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- Common-Mode Rejection RatioDocument1 pageCommon-Mode Rejection RatioKhadar BashaPas encore d'évaluation

- Lica LabDocument7 pagesLica LabKhadar BashaPas encore d'évaluation

- AsusDocument1 pageAsusKhadar BashaPas encore d'évaluation

- AsusDocument1 pageAsusKhadar BashaPas encore d'évaluation

- December 2016 Current AffairsDocument103 pagesDecember 2016 Current AffairsKhadar BashaPas encore d'évaluation

- ConstitutionDocument9 pagesConstitutionKhadar BashaPas encore d'évaluation

- Current Affairs Quiz August 2016Document74 pagesCurrent Affairs Quiz August 2016Khadar BashaPas encore d'évaluation

- Geography of IndiaDocument16 pagesGeography of Indiaatul mishraPas encore d'évaluation

- Improve Your VocublarlyDocument50 pagesImprove Your VocublarlyKhadar BashaPas encore d'évaluation

- EDocument179 pagesEKhadar BashaPas encore d'évaluation

- 10 Spelling & Capitalization DVDDocument4 pages10 Spelling & Capitalization DVDPJ HongPas encore d'évaluation

- Serial Age of Enpires 3Document1 pageSerial Age of Enpires 3Khadar BashaPas encore d'évaluation

- EulaDocument60 pagesEulaGleider TorresPas encore d'évaluation

- UC300 Users GuideDocument19 pagesUC300 Users Guidedreman13Pas encore d'évaluation

- Brief Data Sheet: Hi3535 H.264 CODEC ProcessorDocument7 pagesBrief Data Sheet: Hi3535 H.264 CODEC Processordash boardPas encore d'évaluation

- Manual Rigblaster P&PDocument13 pagesManual Rigblaster P&PTimothy KnottsPas encore d'évaluation

- UGRD-IT6302 Integrative Programming and Technology 1 Midterm ExamDocument5 pagesUGRD-IT6302 Integrative Programming and Technology 1 Midterm ExamCatherine Joy Sapon GarciaPas encore d'évaluation

- Asm 330 LHHDocument84 pagesAsm 330 LHHp kPas encore d'évaluation

- Importance of A Programmer Debugger in Software DevelopmentDocument13 pagesImportance of A Programmer Debugger in Software DevelopmentjackPas encore d'évaluation

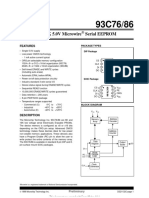

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocument12 pages8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonPas encore d'évaluation

- Asignment2 FIT1047Document8 pagesAsignment2 FIT1047Shaza Shaheeni ShaharulPas encore d'évaluation

- Combo384 DDocument9 pagesCombo384 DfedeperisPas encore d'évaluation

- TUNERPRO GUIDEDocument2 pagesTUNERPRO GUIDESutiknoPas encore d'évaluation

- Introduction To Programming and Problem SolvingDocument33 pagesIntroduction To Programming and Problem SolvingChristine MalibiranPas encore d'évaluation

- LK315T3LA31 SharpDocument25 pagesLK315T3LA31 SharpJayanti MarathePas encore d'évaluation

- 55 CM (21 Inch) Class Color Display MonitorDocument2 pages55 CM (21 Inch) Class Color Display Monitormoricica81Pas encore d'évaluation

- Target RevisionDocument10 pagesTarget RevisionemcviltPas encore d'évaluation

- Computers: The Machines Behind Computing: Hossein BIDGOLIDocument40 pagesComputers: The Machines Behind Computing: Hossein BIDGOLIYakupPas encore d'évaluation

- Pt 100 + Type K/J/R/E/T Thermometer 2 in 1 Model TM-936Document4 pagesPt 100 + Type K/J/R/E/T Thermometer 2 in 1 Model TM-936Sebastian Marin MuñozPas encore d'évaluation

- Notebook CLEVO ManualDocument236 pagesNotebook CLEVO Manualhumtydumty3810Pas encore d'évaluation

- ModBerry 500 - Industrial Computer based on Raspberry PiDocument6 pagesModBerry 500 - Industrial Computer based on Raspberry PiSebastian Rodrigo Contreras GamboaPas encore d'évaluation

- PFRODocument3 pagesPFRORsam SamrPas encore d'évaluation

- EonStor DS 3000 Hardware ManualDocument100 pagesEonStor DS 3000 Hardware Manualcross_of_northPas encore d'évaluation

- Operacion y Codigo de Errores EECO SystemDocument84 pagesOperacion y Codigo de Errores EECO SystemLUIS ARM88Pas encore d'évaluation

- FlashBoot UserGuide 2.3aDocument136 pagesFlashBoot UserGuide 2.3aleogenicPas encore d'évaluation

- Lenovo B590 Service ManualDocument104 pagesLenovo B590 Service ManualMellisa TamayoPas encore d'évaluation

- L&T Infotech Model Questions & Answers for Quantitative AptitudeDocument27 pagesL&T Infotech Model Questions & Answers for Quantitative AptitudedivyasatthishPas encore d'évaluation

- Critical Techniques For High-Speed A-Ds in Real-Time Systems, Sixth Ed.Document56 pagesCritical Techniques For High-Speed A-Ds in Real-Time Systems, Sixth Ed.A. VillaPas encore d'évaluation

- ST24/25C02, ST24C02R ST24/25W02: Serial 2K (256 X 8) EepromDocument16 pagesST24/25C02, ST24C02R ST24/25W02: Serial 2K (256 X 8) EepromrigaboPas encore d'évaluation

- Design and Implementation of Static RAM Cell: Circuit Diagram of SRAMDocument4 pagesDesign and Implementation of Static RAM Cell: Circuit Diagram of SRAMkomaladitya challaPas encore d'évaluation

- Compal La 1911Document57 pagesCompal La 1911stuartb52Pas encore d'évaluation

- Survey of Machine Learning AcceleratorsDocument11 pagesSurvey of Machine Learning AcceleratorsdanydwarPas encore d'évaluation

- A Bidirectional Automatic Room Light Controller Using Visitor CounterDocument12 pagesA Bidirectional Automatic Room Light Controller Using Visitor CounterNilabha DasPas encore d'évaluation