Académique Documents

Professionnel Documents

Culture Documents

DLD Lecture 4

Transféré par

sjbv.hardik5820 évaluation0% ont trouvé ce document utile (0 vote)

38 vues53 pagesDigital logic design PPT

Titre original

Dld Lecture 4

Copyright

© © All Rights Reserved

Formats disponibles

PPT, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDigital logic design PPT

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPT, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

38 vues53 pagesDLD Lecture 4

Transféré par

sjbv.hardik582Digital logic design PPT

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPT, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 53

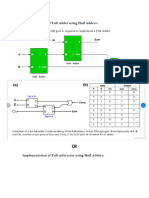

Binary Parallel Adders

Subscript i 4 3 2 1 Full adder

Input carry 0 1 1 0 Ci Z

Augend 1 0 1 1 Ai X

A

Addend 0 0 1 1 Bi Y

Sum 1 1 1 0 Si S

Output carry 0 0 1 1 Ci + 1 C

S4

FA

C5

B4 A4

FA

C4

FA

C2

FA

C3

S1

S2

S3

C1

0

A1

B1 A2 B2

A3

B3

4-BIT FULL ADDER

An n-bit parallel adder requires n full adders

An IC of 4-bit FA has 14 terminals

It is an MSI function

The classical method would require a truth table with 512 entries

(9 input variable) (too cumbersome)

BCD

INPUT

1

0

C1

B1

B2

B3

B4

A1

A2

A3

A4

C5

Not used

S1

S2

S3

S4

Excess-3

Output

BCD -to -Excess 3 Code

Converter

A

B

D

C

D

CD

C+D

(C+D)

Z

Y

X

W

Classical Method

Truth table for four inputs

K-maps for four outputs

Algebraic manipulation of expressions

Logic diagram using gates 4 x AND gates, 4 x OR gates

& 3 x inverters

Requires 3 IC packages & 14 wire connections

(excluding 1/0 connections)

Alternate Design Methods

1 IC package , MS1 function , 5 wire connections

(excluding 1/O connections)

Derivation of a BCD adder

K Z

8

Z

4

Z

2

Z

1

C S

8

S

4

S

2

S

1

Decimal

0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 1 0 0 0 0 1 1

0 0 0 1 0 0 0 0 1 0 2

0 0 0 1 1 0 0 0 1 1 3

0 0 1 0 0 0 0 1 0 0 4

0 0 1 0 1 0 0 1 0 1 5

0 0 1 1 0 0 0 1 1 0 6

0 0 1 1 1 0 0 1 1 1 7

0 1 0 0 0 0 1 0 0 0 8

0 1 0 0 1 0 1 0 0 1 9

Input Binary Sum Output B C D Sum

K Z8 Z4 Z2 Z1 C S8 S4 S2 S1 Decimal

0 1 0 1 0 1 0 0 0 0 10

0 1 0 1 1 1 0 0 0 1 11

0 1 1 0 0 1 0 0 1 0 12

0 1 1 0 1 1 0 0 1 1 13

0 1 1 1 0 1 0 1 0 0 14

0 1 1 1 1 1 0 1 0 1 15

1 0 0 0 0 1 0 1 1 0 16

1 0 0 0 1 1 0 1 1 1 17

1 0 0 1 0 1 1 0 0 0 18

1 0 0 1 1 1 1 0 0 1 19

C = K + Z8 Z4 + Z8 Z2

Addend Augend

4-bit binary adder

K

Z8 Z4 Z2 Z1

carry in carry out

Output

Carry

4-bit binary adder

S8

S4

S2

S1

0

0 1 1 0

BLOCK DIAGRAM OF A BCD ADDER

D0

D1

D2

D3

D4

D5

D6

D7

x y z

x y z

x y z

x y z

x y z

x y z

x y z

x y z

x

y

z

A 3 to 8 line decoder

(Binary to Octal application)

Input lines = n

Output lines = 2

n

(Maximum)

n to m decoder

M 2

n

Truth table of a 3 to 8 line decoder

x y z D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

0 0 0 1 0 0 0 0 0 0 0

0 0 1 0 1 0 0 0 0 0 0

0 1 0 0 0 1 0 0 0 0 0

0 1 1 0 0 0 1 0 0 0 0

1 0 0 0 0 0 0 1 0 0 0

1 0 1 0 0 0 0 0 1 0 0

1 1 0 0 0 0 0 0 0 1 0

1 1 1 0 0 0 0 0 0 0 1

Inputs

Outputs

Design a BCD to Decimal Decoder

X X D

9

D

8

10

X X X X 11

D

6

D

7

D

5

D

4

01

D

2

D

3

D

1

D

0

00

10 11 01 00

y

z

x

w

Map for simplifying a BCD to decimal decoder

D0 = w x y z

D1 = w x y z

D2 = x y z

D3 = x y z

D4 = x y z

D5 = x y z

D6 = x y z

D7 = x y z

D8 = w z

D9 = w z

wx

yz

D

0

= w x y z

D

1

= w x y z

D

2

= x y z

D

3

= x y z

D

4

= x y z

D

5

= x y z

D

6

= x y z

D

7

= x y z

D

8

= w z

D

9

= w z

w

x

y

z

BCD TO DECIMAL DECODER ( 4 LINE TO 10 LINE)

PARTIAL TRUTH TABLE

w x y z

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

8

D

9

1 0 1 0 0 0 1 0 0 0 0 0 1 0

1 0 1 1 0 0 0 1 0 0 0 0 0 1

1 1 0 0 0 0 0 0 1 0 0 0 1 0

1 1 0 1 0 0 0 0 0 1 0 0 0 1

1 1 1 0 0 0 0 0 0 0 1 0 1 0

1 1 1 1 0 0 0 0 0 0 0 1 0 1

Inputs

Outputs

0

1

2

3

4

5

6

7

2

2

2

1

2

0

x

y

z

3 x 8

decoder

Implementation of a full adder with

a decoder and two OR gates

S (x, y, z) = (1, 2, 4, 7)

c (x, y, z) = (3, 5, 6, 7)

c

s

DEMULTIPLEXERS

A decoder with an enable input can function as

a demultiplexer. It receives information on a

single line and transmits this information on

one of 2

n

possible output lines.

A 2 to 4 line decoder with E input is shown

When E = 0, the circuit operates as a decoder

with comlemented outputs.

The decoder can function as a demultiplexer if E line is taken

as a data input line and A & B lines are taken as the selection

line.

2 decoders (3x8) can be connected to form a larger decoder

circuit (4x16)

when:

W = 0, top decoder is inabled

(0000 0111)

W = 1, bottom decoder is enabled

(1000 1111)

Digital function can be easily expanded to accommodate more

inputs and outputs by using e lines

D

0

D

1

D

2

D

3

(A B ) = A + B

(A B ) = A + B

(A B ) = A + B

(A B ) = A + B

A

0

0

1

1

B

0

1

0

1

A

B

E

(a) LOGIC DIAGRAM WITH NAND GATES

Demultiplexer

E A B D0 D1 D2 D3

1 X X 1 1 1 1

0 0 0 0 1 1 1

0 0 1 1 0 1 1

0 1 0 1 1 0 1

0 1 1 1 1 1 0

TRUTH TABLE

A 2 TO 4 LINE DECODER WITH ENABLE E INPUT

2 X 4

Decoder

A

B

E

A B

1 X 4

Demultiplexer

D

0

D

1

D

2

D

3

D

0

D

1

D

2

D

3

Select

Enable

Inputs

(a) Decoder with enable can

function as demultiplexer

(b) Demultiplexer

Input

E

3 X 8

Decoder

3 X 8

Decoder

X

y

z

W

D0 to D7

0000 to 0111

1000 to 1111

D8 to D15

A 4x16 Decoder Constructed with two 3x8 Decoders

E

E

ENCODERS

An encoder produces a reverse operation of a decoder

Input lines 2

n

Output lines = n

An octal-to-binary encoder circuit has 8 inputs and 3

outputs.

Only one input line can be equal to one at any time.

Possible input combinations = 2

8

= 256

Meaningful combinations = 8

Dont care conditions = 248

Priority encoder establishes an input priority to

ensure that the highest priority input line is encoded.

D2

If input 1

D5

Output line D5 is encoded

because of higherpriority

When D

0

is not connected to any OR gate, then

binary output is 000.

x = D

4

+ D

5

+ D

6

+ D

7

y = D

2

+ D

3

+ D

6

+ D

7

z = D

1

+ D

3

+ D

5

+ D

7

D0

D1

D2

D3

D4

D5

D6

D7

Octal to binary encoder

TRUTH TABLE

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 1 0 0 0 0 0 0 0

1 0 1 0 0 0 0 0 0

2 0 0 1 0 0 0 0 0

3 0 0 0 1 0 0 0 0

4 0 0 0 0 1 0 0 0

5 0 0 0 0 0 1 0 0

6 0 0 0 0 0 0 1 0

7 0 0 0 0 0 0 0 1

OUTPUTS (binary)

x y z

INPUTS (Octal)

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

Multiplexers

A digital multiplexer is a combinational circuit that

selects binary information from one of many input

lines and directs it to a single output line.

input lines = 2

n

output lines = 1

selection lines = n

An example of 4-line-to-1-line shows that:

input lines = 2

2

= 4 (I

0,

I

1,

I

2 &

I

3

)

output lines = 1 (Y)

selection lines = 2 (s

0

& s

1

)

A multiplexer is also called a data selector

since it selects one of many inputs and steers

the binary information to the output line.

Multiplexer ICs can have an enable input to

control the operation of the unit. When E is in

disable state, outputs = 0. When E is in enable

state, the circuit functions as a normal MUX.

The E strobe can used to expand two or more

ICs (MUXs) to provide a larger number of

inputs.

(a) Logic Diagram

I

0

I

1

I

2

I

3

S

1

S

0

Y

0

1

2

3

Y

S

1

S

0

4 x 1

MUX

inputs

output

Select

S1 S

0

Y

0 0 I

0

0 1 I

1

1 0 I

2

1 1 I

3

(b) Block Diagram

(c) Function Table

A 4-to-1 Line Multiplexer

Y

1

Y

2

Y

3

Y

4

A

1

A

2

A

3

A

4

B

1

B

2

B

3

B

4

S

E

(Select)

(Enable)

Quadruple 2-to-1 Line multiplexer

Function Table

E S Output Y

1 X all 0s

0 0 Select A

0 1 Select B

4 x MUXs

E = 1, Y

1

-Y

4

= 0

When E = 0, S = 0:

Y

1

= A

1

Y

2

= A

2

Y

3

= A

3

Y

4

= A

4

When E = 0, S=1 Y

1

= B

1

,Y

2

=B

2

, Y

3

=B

3

& Y

4

=B

4

Applications:-

Used for connecting 2 or more sources to a single

destination among computer units.

Used for constructing a common bus system

Function Table

E S Output Y

1 X all Os

0 0 Select A

0 1 Select B

Boolean Function Implementation

Example :- F(A,B,C)= (1,3,5,6)

0

1

A

A

B

C

I

1

I

0

I

2

I

3

S

1

S

0

4 x 1

MUX

F

Y

Minterm

A B C

F

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

S1 S0

(c) Multiplexer Implementation

I

1

I

0

I

2

I

3

0

4

1 2

7

3

5 6

A

A

0 1 A A

(a) Truth Table

It is possible to generate any

function of n+1 variables with

2

n

-to-1 Multiplexer

(b)Implementation Table

Implementing F(A,B,C)= (1,3,5,6) with a multiplexer

I

1

I

0

I

2

I

3

0

4

7

6

3 5

C

C C C C

2

1

F

A

B

I

1

I

0

I

2

I

3

S

1

s0

4 x 1

MUX

Y

C

S1 S0

A C B

0

0

1

1

0

0

1

1

0

2

4

6

1

3

5

7

0

1

0

1

0

1

0

1

0

0

0

0

1

1

1

1

F

0

0

0

0

1

1

1

1

(b) Implementation Table

(c) Multiplexer Implementation

Alternate implementation for F(A,B,C)= (1,3,5,6)

C

(a) Truth Table

Example:- F(A,B,C,D)= (0,1,3,4,8,9,15)

1

0

A

B

C

D

I

0

I

1

I

2

I

3

I

4

I

5

I

6

I

7

S

2

S

1

S

0

8 x 1

MUX

Y F

S

2

S

1

S

0

A B C D

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

F

1

1

0

1

1

0

0

0

1

1

0

0

0

0

0

1

A

A

I0 I1 I2 I3 I4 I5 I6 I7

0 1 2 3 4 5 6 7

8 9 10 11 12 13 14

15

1 1 0 A A

0 0 A

READ ONLY MEMORY ROM

ROM is a device that includes both the decoder and the OR gates within a

single IC package.

It is usually used to implement a complex comb. circuit in one IC package

and eliminates all interconnecting wires between a decoder and OR gates.

It is a memory device in which binary information is stored fusing or

breaking internal links in order to form required circuit paths.

If a ROM has:

input lines = n

output lines = m

Then:

Distinct Addresses (words) = 2

n

Total no. of bits stored in ROM = 2

n

x m

(Where m denotes no. of bits per word)

32 x 8 ROM means:

(i) Words = 32 of 8 bits each

(ii) Output lines = 8

(iii) Input lines = 5

(iv) Total bits = 256 (2

5

x 8)

Internal construction of a 32 x 4 ROM can be shown using a

decoder and four OR gates

2

n

x

m

ROM

n inputs

m outputs

ROM BLOCK DIAGRAM

0

1

2

31

F

1

F

2

F

3

F

4

MINTERMS

A

D

D

R

E

S

S

I

N

P

U

T

S

A

0

A

1

A

2

A

3

A

4

INPUTS = 5

WORDS = 32

BITS/WORD = 4

OUTPUTS = 4

128 LINKS

Logic Construction of a 32 x 4 ROM

(32words of 4 bits each)

Total bits stored = 32 x 4 = 128

5 x 32

decoder

Combinational Logic Implementation - ROM

For an n-input, m-output combinational circuit of a 2

n

x m ROM is needed

The opening of the links is referred to as programming

ROM program table gives the information for the required paths in the

ROM

Example: F

1

(A

1

, A

0

) = (1,2,3)

F

2

(A

1

, A

0

) = (0,2)

Truth Table A

1

A

0

F

1

F

2

0 0 0 1

0 1 1 0

1 0 1 1

1 1 1 0

Combinational circuit implementation with a 4 x 2 ROM is shown:

With AND OR gates

With AND-OR-Inverter gates

2 x 4

decoder

A

0

A

1

F

1

F

2

ROM with

AND-OR gates

00

01

10

11

Combinational Circuit Implementation With a 4 x 2 ROM

A

0

A

1

F

1

F

2

0 0

0 1

1 0

1 1

0 1

1 0

1 1

1 0

TRUTH TABLE

2 x 4

decoder

A

0

A

1

F

1

F

2

ROM with

AND-OR-INVERTER

gates

00

01

10

11

F

1

F

2

Combinational Circuit Implementation With a 4 x 2 ROM

A

0

A

1

F

1

F

2

0 0

0 1

1 0

2 1

0 1

1 0

1 1

1 0

TRUTH TABLE

Types of ROM

Mask programming (ROM)

PROM

EPROM

EAROM

Uses

to implement complex CC from truth tables

to convert one binary code to another

to implement arithmetic functions

to display of characters on CRT

to design microprogrammed control units

Inputs (3) Outputs (6)

Decimal

A

2

A

1

A

0

B

5

B

4

B

3

B

2

B

1

B

0

0 0 0 0 0 0 0 0 0 0 0

1 0 0 1 0 0 0 0 0 1 1

2 0 1 0 0 0 0 1 0 0 4

3 0 1 1 0 0 1 0 0 1 9

4 1 0 0 0 1 0 0 0 0 16

5 1 0 1 0 1 1 0 0 1 25

6 1 1 0 1 0 0 1 0 0 36

7 1 1 1 1 1 0 0 0 1 49

(i) TRUTH TABLE

Example: Design a comb. circuit using a ROM. The circuit

accepts a 3-bit number and generates an output binary

number equal to the square of the input number.

A

2

A

1

A

0

B

5

B

4

B

3

B

2

B

1

B

0

BLOCK DIAGRAM

8 x 4

ROM

F

1

F

2

F

3

F

4

0

A

2

A

1

A

0

F

1

F

2

F

3

F

4

0 0 0 0 0 0 0 0

1 0 0 1 0 0 0 0

2 0 1 0 0 0 0 1

3 0 1 1 0 0 1 0

4 1 0 0 0 1 0 0

5 1 0 1 0 1 1 0

6 1 1 0 1 0 0 1

7 1 1 1 1 1 0 0

ROM TRUTH TABLE

ROM Implementation

(ii)

(iii)

Programmable Logic Array (PLA)

All the bit patterns available in the ROM are not used due to dont care

conditions which results into wastage of equipment

Size of the ROM required to convert a 12-bit card code to a 6-bit internal

alphanumeric code:

4096 x 6

2

12

input output A-Z = 26

valid entries = 47 Numbers = 10

dont care conditions = 4049 other char= 11

47

It is more economical to use PLA (LSI) in such cases to avoid wastage.

Programmable Logic Array (PLA)

A block diagram of the PLA consists of:

n inputs

m outputs

k product terms

m sum terms

Output function: AND-OR form

AND-OR-INVERTOR form

A typical PLA has : n = 16, m = 8, k = 48 programmed links

PLA ROM

2n * k + k * m + m 2

n

* m = 2

16

x 8

1928 524288

1 272

PLA BLOCK DIAGRAM

n x k

Links

n x k

Links

k x m

Links

m

Links

Inputs

m output

K Product

terms

(AND gates)

m Sum

terms

(OR

gates)

IMPLEMENTATION OF PLA COMB CIRCUIT

Mask programmable (PLA)

Field programmable (FPLA)

PLA program table is required to program a PLA

Truth table of the comb. Circuit can be used to simplify the function to get

the minimum AND gates (sum of products)

Paths are specified in its AND OR or AND OR - INVERT

pattern by programming PLA

PLA program table contains:

1

st

column - lists product terms numerically

2

nd

column - specifies the required paths between OR gates and AND gates

T is written if the output inverter is to be bypassed

C is written if the output inverter is not to be bypassed

1 Variable is unprimed

0 variable is primed

- Variable is absent

EXAMPLE#1

F1 (A, B,C) = (4,5,7)

F2 (A,B,C) = (3,5,7)

C

1 1 1 1 1

1

00

01 11 10 00

01

11 10

BC

A

A

BC

C

B B

F

1

(A,B,C)=(4,5,7)

F

2

(A,B,C)=(3,5,7)

F

1

=AB+AC

F

2

=AC+BC

Map simplification

0

1

A

A

0

1

0 0 0 0

0

0 0

0

0

0

F

1

=A+BC

F

2

=C + AB

F

1

F2 = A + BC + C + AB

F1F2 = A + BC + AC + BC

F1F2 = AB + AC + C + AB

F1F2 = AB + AC + BC

So, the value k = 3.

A B C F1 F2

0 0 0 0 0

0 0 1 0 0

0 1 0 0 0

0 1 1 0 1

1 0 0 1 0

1 0 1 1 1

1 1 0 0 0

1 1 1 1 1

TRUTH TABLE

STEPS REQUIRED IN PLA IMPLEMENTATION

1 -

1 1

- 1

1 0 -

1 - 1

- 1 1

1

2

3

Outputs

F1 F2

Inputs

A B C

Product

term

AB

AC

BC

PLA Program table

T/C T T

F

1

=AB+AC

F

2

=AC+BC

1

2

3

AB

AC

BC

C

B

A

AB + AC

AC + BC

n = 3

m = 2

K = 3

K * m

(6)

+ m

(2)

PLA Links = 26

PLA with 3 inputs, 3 product terms, and 2 outputs; it

implements the combinational circuit

F

1

F

2

EXAMPLE#2

F

1

(A,B,C)=(3,5,6,7)

F

2

(A,B,C)=(0,2,4,7)

1

0

C

1 1 1

1

1 1

1 1

00

01 11 10 00

01

11 10

BC

A

A

BC

A

A

C

B

B

F

1

=AC+AB+BC

F

2

=BC+AC+ABC

1

0

C

0

0 0 0

0 0

0 0

00

01 11 10 00

01

11 10

BC

A

A

BC

A

A

C

B

B

F

1

=BC+AC+AB

F

2

=BC+AC+ABC

1

0

1 1

1 1

1 -

- 1

- 0 0

0 - 0

0 0 -

1 1 1

1

2

3

4

Outputs

F1 F2

Inputs

A B C

Product

term

BC

AC

AB

C T T/C

Examples

PLA Program Table

ABC

Condition

F

1

(A,B,C)=(3,5,6,7)

F

2

(A,B,C)=(0,2,4,7)

F

1

=(BC+AC+AB)

F

2

=BC+AC+ABC

Inputs=3

Product term=4

Outputs =2

HOME ASSIGNMENT

DRAW CIRCUIT FROM THE

PLA IMPLEMENTATION TABLE

Vous aimerez peut-être aussi

- Binary Parallel AddersDocument58 pagesBinary Parallel AddersJagan RajendiranPas encore d'évaluation

- Chapter 5-1Document31 pagesChapter 5-1Tushar SarkarPas encore d'évaluation

- Ch4 - 2 Decoders-MultiplexersDocument39 pagesCh4 - 2 Decoders-MultiplexersMariam ElnourPas encore d'évaluation

- DEMSTDocument10 pagesDEMSTSaloni VaniPas encore d'évaluation

- 08 DecodersssssDocument31 pages08 DecodersssssDani Tri KurniawanPas encore d'évaluation

- 32 DLD Lec 32 Combinational Circuit Implementation Using Decoder, Encoder, Priority Encoder 30 Nov 2022 Lecture SlidesDocument18 pages32 DLD Lec 32 Combinational Circuit Implementation Using Decoder, Encoder, Priority Encoder 30 Nov 2022 Lecture SlidesZuha FatimaPas encore d'évaluation

- Combinational Logic: By: Ali MustafaDocument33 pagesCombinational Logic: By: Ali MustafaNimra WaqarPas encore d'évaluation

- Combinational Logic: Dr/Ghada KareemDocument38 pagesCombinational Logic: Dr/Ghada Kareemlove youPas encore d'évaluation

- 8 To 3 Bit Priority EncoderDocument12 pages8 To 3 Bit Priority EncoderDev SejvaniPas encore d'évaluation

- Nand-Only Logic CircuitsDocument33 pagesNand-Only Logic Circuitsyagnasree_sPas encore d'évaluation

- Bayan University of Science and Technology Collage of EngineeringDocument31 pagesBayan University of Science and Technology Collage of EngineeringOmur NoorPas encore d'évaluation

- Lab 9 Encoders and DecodersDocument7 pagesLab 9 Encoders and Decoderssafdarmunir070Pas encore d'évaluation

- Chapter 3 - Combinational Logic DesignDocument36 pagesChapter 3 - Combinational Logic Designmahbub mitulPas encore d'évaluation

- DDL 06Document8 pagesDDL 06Anonymous KLGejaVPas encore d'évaluation

- Comb Circ PDFDocument63 pagesComb Circ PDFMengistu KetemaPas encore d'évaluation

- Comb Circ PDFDocument63 pagesComb Circ PDFSrinivasan KrishnanPas encore d'évaluation

- Combinational Circuits LDICDocument129 pagesCombinational Circuits LDIChemanth ramireddyPas encore d'évaluation

- Decodere and Ncoder: ObjectivesDocument3 pagesDecodere and Ncoder: ObjectivesIqea janPas encore d'évaluation

- Introduction To Combinational Logic Circuits and Advanced Combinational Logic CircuitsDocument18 pagesIntroduction To Combinational Logic Circuits and Advanced Combinational Logic CircuitsBhaskar MPas encore d'évaluation

- ELEC2141 Combinational Circuit Building BlocksDocument36 pagesELEC2141 Combinational Circuit Building Blocks刘浩灵Pas encore d'évaluation

- R1 CH5 Encoder Decoder Mux DemuxDocument44 pagesR1 CH5 Encoder Decoder Mux DemuxChang BillyPas encore d'évaluation

- Lecture7 Chapter4 - Study Encoders, Function Implementation Using EncodersDocument18 pagesLecture7 Chapter4 - Study Encoders, Function Implementation Using EncodersAyesha HussainPas encore d'évaluation

- Chapter 3 - Encoder, DecoderDocument39 pagesChapter 3 - Encoder, Decodernizar_ayub95Pas encore d'évaluation

- EncoderDocument9 pagesEncoderDhaivat PandyaPas encore d'évaluation

- Combinational Circuits - 3Document76 pagesCombinational Circuits - 3harshulyagnik.csePas encore d'évaluation

- Module 3 STDDocument93 pagesModule 3 STDmatlabdec12Pas encore d'évaluation

- Lecture2 Chapter4 - BCD To Excess-3 Code Converter DesignDocument19 pagesLecture2 Chapter4 - BCD To Excess-3 Code Converter DesignAyesha HussainPas encore d'évaluation

- Solution ManualDocument14 pagesSolution ManualdattadhanwePas encore d'évaluation

- 30 DLD Lec 30 Combinational Circuit Implementation Using Decoder 23 Dec 2020 Lecture NotesDocument17 pages30 DLD Lec 30 Combinational Circuit Implementation Using Decoder 23 Dec 2020 Lecture NotesEhsan MalikPas encore d'évaluation

- DSD Lab Manual 2021Document21 pagesDSD Lab Manual 2021adityaPas encore d'évaluation

- Tutorial3-With Answer KeyDocument12 pagesTutorial3-With Answer KeyRetheshPas encore d'évaluation

- Combinational Circuits - 2Document66 pagesCombinational Circuits - 2harshulyagnik.csePas encore d'évaluation

- Topic 7. Combinational Logic Circuit (2) : Ce232 Digital SystemDocument55 pagesTopic 7. Combinational Logic Circuit (2) : Ce232 Digital SystemNep NepPas encore d'évaluation

- Cse 205: Digital Logic DesignDocument89 pagesCse 205: Digital Logic DesignAfifa murshida NazinPas encore d'évaluation

- Quiz Questions For DLD LabDocument6 pagesQuiz Questions For DLD LabGerald Carson100% (1)

- Presentation 1Document14 pagesPresentation 1Tapu GhoshPas encore d'évaluation

- Arithmetic CircuitsDocument69 pagesArithmetic Circuitsshivam007100% (2)

- Combinational Logic Implementation Technologies: Hai Zhou ECE 303 Advanced Digital Design Spring 2002Document40 pagesCombinational Logic Implementation Technologies: Hai Zhou ECE 303 Advanced Digital Design Spring 2002Aravind Ramesh100% (1)

- Combinational Logic Implementation: Multi-Level NetworksDocument57 pagesCombinational Logic Implementation: Multi-Level NetworksMod-ali RadiPas encore d'évaluation

- Unit-5: Combinational Circuit: Multiplexers-De-multiplexers Decoder-EncoderDocument22 pagesUnit-5: Combinational Circuit: Multiplexers-De-multiplexers Decoder-EncoderFaizan KhanPas encore d'évaluation

- CSE 140 Midterm 3 - SolutionDocument15 pagesCSE 140 Midterm 3 - SolutionyonasPas encore d'évaluation

- Experiment 10: Multiplexers: Mr. Mohamed El-SaiedDocument4 pagesExperiment 10: Multiplexers: Mr. Mohamed El-SaiedEstéfano GómezPas encore d'évaluation

- Chapter 04Document33 pagesChapter 04Iqbal Ashfaq Joiya100% (1)

- Cps 213 Chapter 4Document43 pagesCps 213 Chapter 4Krish Gopi KondetiPas encore d'évaluation

- Encoders/ Decoders Multipleexers and DemultiplexersDocument10 pagesEncoders/ Decoders Multipleexers and DemultiplexersRashid AltafPas encore d'évaluation

- Digital Logic - Computer ArchitectureDocument41 pagesDigital Logic - Computer ArchitectureManvir SinghPas encore d'évaluation

- Combinational Circuit Design-2Document36 pagesCombinational Circuit Design-2mikko intalPas encore d'évaluation

- Combinational Logic Circuits (Circuits Without A Memory)Document78 pagesCombinational Logic Circuits (Circuits Without A Memory)Hamza NasirPas encore d'évaluation

- Practical QuizDocument13 pagesPractical QuizSebastian Austin SuelaPas encore d'évaluation

- Comb CircDocument63 pagesComb Circm.sangeethjaPas encore d'évaluation

- DD Module-2 Part-2 (Comparator, Encoder, Decoder, Mux)Document43 pagesDD Module-2 Part-2 (Comparator, Encoder, Decoder, Mux)Aneal SinghPas encore d'évaluation

- Logic Circuits and Switching TheoryDocument57 pagesLogic Circuits and Switching TheoryBruce Lamb100% (1)

- Exp 8 DecoderDocument4 pagesExp 8 DecoderabdallaPas encore d'évaluation

- Laboratory Exercise #2 4-Bit BCD Decoder: Submitted To Professor in EE 538/LDocument5 pagesLaboratory Exercise #2 4-Bit BCD Decoder: Submitted To Professor in EE 538/LDSPas encore d'évaluation

- Priority EncoderDocument11 pagesPriority Encodershivam007Pas encore d'évaluation

- Combinational Logic CircuitsDocument29 pagesCombinational Logic CircuitsVichu SadaPas encore d'évaluation

- DSD BookDocument270 pagesDSD BookROUGH X YTPas encore d'évaluation

- Digital Electronics For Engineering and Diploma CoursesD'EverandDigital Electronics For Engineering and Diploma CoursesPas encore d'évaluation

- HFP v1.7.1Document144 pagesHFP v1.7.1sjbv.hardik582Pas encore d'évaluation

- Excerpt GB8Document101 pagesExcerpt GB8Hesham_Hegazy18Pas encore d'évaluation

- Excel Gantt Chart TemplateDocument9 pagesExcel Gantt Chart TemplateAnuth SiddharthPas encore d'évaluation

- P 89 V 51 RD 2Document75 pagesP 89 V 51 RD 2ckprvn100% (2)

- C Coding StandardDocument21 pagesC Coding Standardsjbv.hardik582Pas encore d'évaluation

- Application Note Deep Sleep Modes 7.25.14Document1 pageApplication Note Deep Sleep Modes 7.25.14sjbv.hardik582Pas encore d'évaluation

- C Coding StandardDocument21 pagesC Coding Standardsjbv.hardik582Pas encore d'évaluation

- Application Note Deep Sleep Modes 7.25.14Document1 pageApplication Note Deep Sleep Modes 7.25.14sjbv.hardik582Pas encore d'évaluation

- DLD Lecture 2Document41 pagesDLD Lecture 2sjbv.hardik582Pas encore d'évaluation

- DLD Lecture 1Document50 pagesDLD Lecture 1sjbv.hardik582Pas encore d'évaluation

- Digital and Logic Design No. 3 (Logic Circuits) From APCOMSDocument34 pagesDigital and Logic Design No. 3 (Logic Circuits) From APCOMSNaveedPas encore d'évaluation

- DLD Lecture 1Document50 pagesDLD Lecture 1sjbv.hardik582Pas encore d'évaluation

- GTU Digital ElectronicsDocument3 pagesGTU Digital Electronicssjbv.hardik582Pas encore d'évaluation

- Cushah PapersDocument7 pagesCushah Paperssjbv.hardik582Pas encore d'évaluation

- Meeting 2 Inside ComputerDocument16 pagesMeeting 2 Inside ComputerFelix Rizky LesmanaPas encore d'évaluation

- Full Form List in ComputerDocument6 pagesFull Form List in ComputerAndrew ParkarPas encore d'évaluation

- Grade 10 Q2 TLE-CSSNCII LASDocument72 pagesGrade 10 Q2 TLE-CSSNCII LASBernadeth Irma Sawal Caballa100% (2)

- Ms Dos & Fundamental Final Book PDFDocument55 pagesMs Dos & Fundamental Final Book PDFRahul SinghPas encore d'évaluation

- TM213TRE.425-EnG Automation Runtime V4330Document60 pagesTM213TRE.425-EnG Automation Runtime V4330meirelgPas encore d'évaluation

- Sharp GX30 SM VerB FinalDocument166 pagesSharp GX30 SM VerB Finalgiancarlos1979Pas encore d'évaluation

- BasicC NotesDocument70 pagesBasicC NotesChinmayac CnPas encore d'évaluation

- Indutrial Training Report VarunDocument48 pagesIndutrial Training Report Varunvarun pandey 1065Pas encore d'évaluation

- Unit 5Document29 pagesUnit 5Dhileepan Kumarasamy0% (1)

- Components of A Computer SystemDocument26 pagesComponents of A Computer SystemhehehehePas encore d'évaluation

- 1st Year Computer NotesDocument67 pages1st Year Computer NotesMuhammadPas encore d'évaluation

- Analysis of The General Block Diagram of The MotherboardDocument9 pagesAnalysis of The General Block Diagram of The Motherboardraj grdPas encore d'évaluation

- LAB1Document42 pagesLAB1farheen khosoPas encore d'évaluation

- Memory and Its TypesDocument4 pagesMemory and Its TypesNikku100% (2)

- Module 2 - Reading7 - ReadOnlyMemoryDocument8 pagesModule 2 - Reading7 - ReadOnlyMemoryChristopher AdvinculaPas encore d'évaluation

- The First Book of KIMDocument178 pagesThe First Book of KIMmatahachirohPas encore d'évaluation

- 25xx+ SMDocument122 pages25xx+ SMmagma871385Pas encore d'évaluation

- BCA I Year Digital Computer Oragnisation Practice QuestionsDocument6 pagesBCA I Year Digital Computer Oragnisation Practice Questionsarchana naikPas encore d'évaluation

- AnswerDocument51 pagesAnswersamPas encore d'évaluation

- Different Types of Electrical Power and Hydraulic ToolsDocument8 pagesDifferent Types of Electrical Power and Hydraulic ToolsDex Licong0% (1)

- How To Install Stock ROM On Tecno Phantom 8 (AX8) (Firmware Flash File) - 1599476194110Document4 pagesHow To Install Stock ROM On Tecno Phantom 8 (AX8) (Firmware Flash File) - 1599476194110Mory CondePas encore d'évaluation

- 1 Wire App-NoteDocument36 pages1 Wire App-NotehuynhkhoaPas encore d'évaluation

- UpdatedDocument65 pagesUpdatedcsemaths11Pas encore d'évaluation

- 9800301C 8080 8085 Assembly Language Programming Manual Nov78Document224 pages9800301C 8080 8085 Assembly Language Programming Manual Nov78Rupam OjhaPas encore d'évaluation

- Microcontrooller and Microprocessor-Lecture 3Document9 pagesMicrocontrooller and Microprocessor-Lecture 3نهاد نهادPas encore d'évaluation

- Computer Organization and Architecture C PDFDocument24 pagesComputer Organization and Architecture C PDFGemma Capilitan BoocPas encore d'évaluation

- A Presentation On Semiconductor Memories PDFDocument112 pagesA Presentation On Semiconductor Memories PDFSarthak RoyPas encore d'évaluation

- Unit 62 Microprocessor Systems and ApplicationsDocument11 pagesUnit 62 Microprocessor Systems and ApplicationsPaul Jensen Umali SatimbrePas encore d'évaluation

- Internal Memory Ch1Document26 pagesInternal Memory Ch1shanbel ayayuPas encore d'évaluation

- DS2502 1Kb Add-Only Memory: Features Pin AssignmentDocument24 pagesDS2502 1Kb Add-Only Memory: Features Pin AssignmentrogeriocorreaPas encore d'évaluation