Académique Documents

Professionnel Documents

Culture Documents

Capitulo 3 Expo

Transféré par

ChristianLojan0 évaluation0% ont trouvé ce document utile (0 vote)

18 vues53 pagesCapitulo 3 Arquitectura de computadores.

Copyright

© © All Rights Reserved

Formats disponibles

PPTX, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentCapitulo 3 Arquitectura de computadores.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPTX, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

18 vues53 pagesCapitulo 3 Expo

Transféré par

ChristianLojanCapitulo 3 Arquitectura de computadores.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPTX, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 53

CAPITULO 3

COMPONENTES DEL COMPUTADOR Y FUNCIONAMIENTO DEL

COMPUTADOR.

DOCENTE: ING. CHRISTIAN LOJAN HERRERA

EL COMPUTADOR ESTA

CONSTITUIDO.

CPU.

MEMORIA

UNIDADES DE E/S.

ALTO NIVEL

DESCRIPCION DEL COMPORTAMIENTO (DATOS Y SEALES)

ESTRUCTURA (CONTROL E INTERCONEXION)

3.1. COMPONENTES DEL

COMPUTADOR.

CONCEPTOS DE Von Neumann.

Datos e instrucciones comparten una memoria de lectura y escritura.

Direccionado de memoria discrimina el tipo de dato.

Ejecucin secuencial de programas a menos que se programe un salto.

COMPONENTES LGICOS.

Guardan datos / realizan operaciones aritmticas o lgicas.

Programacin en hardware vs. Programacin en software.

HARDWARE VS. SOFTWARE.

Hardware: Se requiere una reprogramacin fsica.

Software: Hardware de propsito general, con seales de control

generadas por un algoritmo secuencial.

REGISTROS DEL COMPUTADOR

Dentro de la CPU hay un conjunto de registros que ofrecen un nivel de

memoria mas rpido y pequeo que la memoria principal.

Registros visible al usuario.

Registros de control y de estado.

El registro visible al usuario es aquel que puede ser referenciado por

medio del lenguaje maquina que ejecuta el procesador; accesible a

todos los programas tanto los de aplicacin como los del sistema; los

registros normalmente disponibles son:

Registro de datos.

Registros de direccin.

Registro ndice

Puntero de segmento.

Puntero de pila

COMPONENTES DE ALTO NIVEL.

REGISTROS DEL COMPUTADOR

Los registros de control y de estado se emplean para controlar las

operaciones del procesador, la mayor parte de estos registros no

son visibles para los usuarios , algunos pueden ser accesibles a las

instrucciones de maquina ejecutadas en un modo de control.

MAR: Memory Address Register.

MBR: Memory Buffer Register.

IOAR: Input Output Address Register.

IOBR: Input Output Buffer Register.

REGISTROS DEL COMPUTADOR.

Adems de estos los siguientes registros son esenciales en la ejecucin de

instrucciones.

Contador de programa(PC).

Registro de instruccin(IR)

Program status word(PSW) contiene cdigos de condicin junto con otras

informaciones de estado.

Signo. Supervisor

Cero. Igualdad.

Acarreo. Se produce acarreo mas alla del bit mas significativo.

Desbordamiento.

Habilitar/Inhabilitar interrupciones.

FUNCIONAMIENTO DEL

COMPUTADOR

Ejecucin de un programa.

Capta instruccin (fetch).

Ejecuta la instruccin.

Ciclo de instruccin (Procesamiento para

ejecutar una instruccin)

CICLOS DE CAPTACION Y

EJECUCION.

La instruccin captada se almacena en el registro de instruccin

(IR). El CPU interpreta la instruccin que puede ser en general del

siguiente tipo:

CPU-Memoria Transferir datos del CPU a la memoria o viceversa.

CPU-ES Transferir datos a o desde el exterior mediante

transferencias entre el CPU y un mdulo de E/S.

Procesamiento de datos El CPU debe realizar alguna operacin

aritmtica o lgica con los datos.

Control Alteracin de la secuencia de ejecucin.

Una instruccin puede implicar una combinacin de las acciones

anteriores.

EJEMPLO

Sea una maquina hipottica cuyas caractersticas son :

El procesador tiene un nico registro de datos el Acumulador(AC).

Tanto las instrucciones como los datos son de 16 bits de longitud.

El formato de instruccin dedica 4 (16 codigos de operacin diferentes)bits para el codigo de

operacin y 12(4096=4K palabras) bits para direccionar la memoria directamente.

Registros internos de la CPU:

Contador de progarma(PC):direccion de la instruccin a ser leida.

Registro de instruccin(IR):Instruccin que esta ejecutandose

Acumulador(AC): Almacenamiento temporal

Cod . Op.

S

0 3 4 15

Direccion

0 1 15

Magnitud

EJEMPLO

Lista parcial de los codigos de operacin:

0001 = Cargar de la memoria la acumulador.

0010 = Almacenar el AC en memoria.

0101 = Sumar al AC el contenido de la memoria

EJEMPLO

EJEMPLO

EJEMPLO

PC = PC + 1

EJEMPLO

EJEMPLO

EJEMPLO

CICLOS DE INSTRUCCIN

(ESTADOS)

CICLOS DE INSTRUCCION

1. clculo direccin instruccin: determina la direccin de la

siguiente instruccin a ejecutarse

2. bsqueda instruccin: lee la instruccin de suposicin de

memoria a la cpu.

3. decodificacin de la instruccin: analiza la instruccin para

determinar el tipo de operacin a realizar y los operandos que se

usarn.

4. clculo direccin operando: si la operacin implica la referencia

a un operando en la memoria e/s, entonces se determina la

direccin.

CICLOS DE INSTRUCCION

5. Bsqueda del operando: busca el operando en lamemoria e/s.

6.operacin sobre los datos: ejecuta la instruccin.

7. clculo direccin resultado.

8. almacenamiento resultado

RESUMEN: Una vez que se hace un fetch de una instruccin, los

especificadores de los operandos deben ser identificados. Cada

operando que se encuentra en memoria es extrado de la misma

mediante un fetch, pero es posible que se requiera realizar un acceso

indirecto a memoria. Es importante aclarar que no se requiere accesar

la memoria (realizar un fetch) cuando los operandos de la instruccin

se encuentran ya en los registros del CPU. Una vez que la instruccin es

ejecutada, es posible que se requiera almacenar el resultado en la

memoria principal.

INTERRUPCIONES

Programa Generada por alguna condicin como resultado de la

ejecucin de una instruccin (desbordamiento, divisin por cero,

instruccin no existente o acceso fuera del espacio de memoria).

Termporizacin Generada por un temporizador interno al

procesador para realizar una funcin de manera regular.

E/S Generada por un controlador de E/S para indicar fin de

operacin sin error o avisar una condicin de error.

Fallo del hardware Generada por un fallo como deficiencia en

alimentacin

INTERRUPCIONES?

MEJORA EL DESEMPEO DEL PROCESADOR.

DESPERDICIO DE CICLOS DE PROCESADOR.

EJECUCION DE INTERRUPCIONES

1,2 Y 3.- Instrucciones que no

generan procesos de e/s.

4.- Instruccin implica copia de

datos y inicializacin (prep.

Parmetros de control.)

El programa se encierra en un

bucle en espera de E/S.

5.- Fin, devuelve Flag (correcto o

con errores)

Interrupciones y el ciclo de

instruccin. (espera corta)

Cuando se invoca a WRITE,

solo se ejecuta el cdigo de

preparacin y la orden de

e/s.

Continua el programa

usuario mientras el dispositivo

interacta con los datos en

memoria.

Al terminar enva peticin de

interrupcin.

Suspende la operacin del

programa de usuario y

ejecuta el gestor de

interrupciones.

Interrupciones y el ciclo de

instruccin. (espera corta)

CICLO DE INSTRUCCIN CON

INTERRUPCIONES

TRATAMIENTO DE INTERRUPCIONES

Suspende la ejecucin del programa en curso y guarda su

contexto.

Carga el contador de programa con la direccin de comienzo de

la rutina de gestin de interrupcin.

TRATAMIENTO DE INTERRUPCIONES

Interrupcin y ciclo de instruccin

(espera larga)

ESTADOS CICLO DE INSTRUCCIONES

CON INTERRUPCIONES

INTERRUPCIONES MULTIPLES

SECUENCIA TEMPORAL CON

VARIAS INTERRUPCIONES.

3.3.- Estructuras de

interconexion

SU PRINCIPAL OBJETIVO ES ASEGURAR LA COMUNICACIN ENTRE LOS

MDULOS DEL COMPUTADOR.

Tipos de intercambio entre

estructuras de interconexion.

Los conjuntos de lneas que conectan los diversos mdulos se

denomina estructura de interconexin. El diseo de la estructura

depende de los intercambios que se deban producir.

Memoria Est constituido por palabras de la misma longitud, cada

una de ellas con una nica direccin numrica. Seales de control

(Lectura/Escritura)

Mdulo de E/S Funcionalmente es similar a la memoria. Hay dos

tipos de operaciones (lectura y escritura), puede controlar ms de

un dispositivo externo. Las interfaces se denominan Puertos.

CPU Lee instrucciones y datos, escribe datos una vez que los ha

procesado, y utiliza ciertas seales para controlar el funcionamiento

del sistema.

Tipos de transferencia.

La estructura de interconexin debe dar cobertura a los siguientes

tipos de transferencias:

Memoria - CPU El CPU lee una instruccin o dato desde la memoria.

CPU - Memoria El CPU escribe un dato en la memoria.

E/S - CPU El CPU lee datos de un dispositivo de E/S a travs de un

mdulo de E/S.

CPU - E/S El CPU envo datos al dispositivo de E/S.

Memoria - E/S y viceversa Se utiliza el acceso directo a memoria

(DMA), no se pasa a travs del CPU.

Interconexin de modulos.

INTERCONEXIN CON BUSES.

Un bus es un camino de comunicacin entre dos o ms dispositivos.

Al ser un camino en comn pueden solaparse las seales. El bus

esta disponible para una transaccin a la vez.

El bus posee varias lneas de comunicacin que determinan

cuantos bits se pueden transmitir simultneamente.

Los computadores poseen varios buses con jerarqua.

El bus del sistema comunica los componentes principales del

computador (Pueden haber uno o varios buses).

ESTRUCTURA DEL BUS.

ESTRUCTURA DEL BUS

Lneas/bus de datos: camino para transferir datos entre el resto de

componentes de un computador. Su anchura (nmero de lneas

elctricas) suele ser una potencia de dos (8=2^3, 16=2^4, 32=2^5,

64=2^6, ...).

Lneas/bus de direcciones: designan la posicin/direccin de los

datos. Son salidas de la CPU/procesador y determinan capacidad

de direccionamiento.

Lneas/bus de control: controlan el acceso y uso de las lneas/buses

anteriores.

ORDENES Y OPERACIONES.

Memory write.

Memory Read.

I/O write.

I/O Read.

Transfer ACK.

Bus Request

Bus Grant.

Interrupt request.

Interrupt Ack.

Clock.

Reset.

Buses.

A nivel fsico son un conjunto de conductores elctricos grabados

en una placa.

Los dispositivos pueden estar conectadas a unas o todas las lneas

del bus.

Jerarquas de Buses Mltiples.

Mayor nmero de dispositivos, mas retardos en la propagacin.

Cuellos de botella por peticiones mltiples (Aumentar el ancho de

bus vs. Incremento de velocidad.)

Arquitectura Tradicional

Arquitectura de Altas prestaciones.

Elementos del diseo de un bus

Tipos de buses

Las lneas de los buses se dividen en:

Dedicadas.- Usa lneas separadas para direcciones y datos

Multiplexadas.-Usa las mismas lneas

Mtodo de arbitraje.- el control del bus puede necesitar mas de un mdulo

Centralizado.- Un nico dispositivo asigna tiempos en el bus

Distribuido.- Cada mdulo puede controlar el acceso al bus

Temporizacin.- forma de controlar los tiempos en el bus

Sincrnico.- la presencia de un evento est determinada por la presencia de un reloj

Asincrnico.- la presencia de un evento en el bus es consecuencia y depende de

que se produzca un evento previo no precisan la existencia de una seal de reloj

SINCRONA

Asncrona

Asncrona

Elementos de diseo de un bus.

Anchura del bus

Direccin.-el ancho de este bus afecta a la capacidad del sistema

Datos.- mientras mas ancho es el bus de datos, mayor es el nmero de

bits que se transmiten a la vez

Tipo de transferencia de datos:

Lectura

Escritura

Lectura-modificacin-escritura

Lectura despus de escritura

Bloque

Vous aimerez peut-être aussi

- 3.1 y 3.2Document22 pages3.1 y 3.2CristianJonatanPas encore d'évaluation

- T2 Arquitectura de Un ComputadorDocument7 pagesT2 Arquitectura de Un ComputadorSamuelPas encore d'évaluation

- Arquitectura Parcial Nro 1Document30 pagesArquitectura Parcial Nro 1Pepito La RiojaPas encore d'évaluation

- Arquitectura de Computadoras (Clase 2) Estructura BásicaDocument39 pagesArquitectura de Computadoras (Clase 2) Estructura BásicaVictor Junco RenteraPas encore d'évaluation

- Unidad - 2 Arq - CompDocument10 pagesUnidad - 2 Arq - CompHéctor Francisco Díaz UribePas encore d'évaluation

- Curso de ArquitecturaDocument8 pagesCurso de Arquitectura54u1Pas encore d'évaluation

- Arqcom - Jose Ignacio Nota - TP2 - 1K4Document6 pagesArqcom - Jose Ignacio Nota - TP2 - 1K4Nacho NotaPas encore d'évaluation

- Diagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoDocument8 pagesDiagrama de Computadora y Funcionamiento-El Fenómeno CibernéticoAli SerranoPas encore d'évaluation

- Organización Del ProcesadorDocument12 pagesOrganización Del ProcesadorGeovanny Quiroz MoncerradPas encore d'évaluation

- Presentacion No. 2Document28 pagesPresentacion No. 2Einie VegaPas encore d'évaluation

- Buses Del SistemaDocument42 pagesBuses Del Sistemaluisoswal91Pas encore d'évaluation

- Sistemas Operativos - Introduccion A Los ComputadoresDocument9 pagesSistemas Operativos - Introduccion A Los ComputadoresJuan Segundo ArgayoPas encore d'évaluation

- Estructura Básica de Una ComputadoraDocument48 pagesEstructura Básica de Una ComputadoraAntony JaredPas encore d'évaluation

- 3ArqComp - CPUDocument44 pages3ArqComp - CPUsaraPas encore d'évaluation

- Perspectivas de Alto Nivel Del Funcionamiento y de Las Interconexiones Del ComputadorDocument17 pagesPerspectivas de Alto Nivel Del Funcionamiento y de Las Interconexiones Del ComputadorAldair Huamani Cusi0% (1)

- Tema 2Document21 pagesTema 2lucilafr.4739Pas encore d'évaluation

- Tarea 6 Sistemas DigitalesDocument6 pagesTarea 6 Sistemas DigitalesMartin GomezPas encore d'évaluation

- Sistemas I Informe 1Document21 pagesSistemas I Informe 1alexPas encore d'évaluation

- Tarea 6 Sistemas DigitalesDocument5 pagesTarea 6 Sistemas DigitalesAlexisPas encore d'évaluation

- Diagrama Bloques ComputadoraDocument6 pagesDiagrama Bloques ComputadoraLuis Felipe OsorioPas encore d'évaluation

- TP 4Document4 pagesTP 4Matias PiovesanPas encore d'évaluation

- UNIDAD 1 Clase 02 Modelo de VNDocument63 pagesUNIDAD 1 Clase 02 Modelo de VNDaniel JimenezPas encore d'évaluation

- Taller de Arquitectuta de ComputadoresDocument33 pagesTaller de Arquitectuta de ComputadoresTIC ́s Ayuda Para Docentes TecnologíaPas encore d'évaluation

- CPU Memoria Principal CPU Dispositivos de Entrada Salida BusesDocument31 pagesCPU Memoria Principal CPU Dispositivos de Entrada Salida BusesAdrian Alejandro Manrique BravoPas encore d'évaluation

- 2do Parcial S.ODocument289 pages2do Parcial S.OEddy BastidasPas encore d'évaluation

- Resumen-Sistemas de ComputacionDocument6 pagesResumen-Sistemas de ComputacionDilan Jauregui SanchezPas encore d'évaluation

- Funcionamiento de CpuDocument5 pagesFuncionamiento de CpuRodolfo FloresPas encore d'évaluation

- ResumenDocument9 pagesResumenBerenice Hermenegildo AdrianPas encore d'évaluation

- Arquitectura Von NeumannDocument8 pagesArquitectura Von NeumannDaniel Medrano IzquierdoPas encore d'évaluation

- Areli Bravo - Actividad 1Document19 pagesAreli Bravo - Actividad 1Juari RamosPas encore d'évaluation

- Diagrama A Bloques de Una ComputadoraDocument15 pagesDiagrama A Bloques de Una ComputadoraAnabelJulianaVarhenVilelaPas encore d'évaluation

- Historia de La Computacion FINALDocument19 pagesHistoria de La Computacion FINALMaria Losada Rojas100% (1)

- Resumen de Sistemas OperativosDocument85 pagesResumen de Sistemas OperativosDaniela CoccorulloPas encore d'évaluation

- ADC - El Ciclo de InstrucciónDocument14 pagesADC - El Ciclo de InstrucciónSamuel Rocha GarcíaPas encore d'évaluation

- Estructura y Funcionamiento de La CpuDocument28 pagesEstructura y Funcionamiento de La CpuLuis Oswaldo Velasquez LoveraPas encore d'évaluation

- Unidad IDocument10 pagesUnidad IJose Manuel Godoy EscribarPas encore d'évaluation

- Resumen Parcial 1Document16 pagesResumen Parcial 1Juanma BecerraPas encore d'évaluation

- Sistema Operativo CAP 1 - Jhonny Eysten Shapiama AlvaradoDocument4 pagesSistema Operativo CAP 1 - Jhonny Eysten Shapiama AlvaradoJhonny Shapiama MozombitePas encore d'évaluation

- Unidad de ControlDocument23 pagesUnidad de ControlWilliams Edison ArizapanaPas encore d'évaluation

- Actividad 5Document9 pagesActividad 5juan mezaPas encore d'évaluation

- MicrocontroladoresDocument13 pagesMicrocontroladoresLajuh PeñaPas encore d'évaluation

- Resumen Introducción A Los Sistemas InformáticosDocument10 pagesResumen Introducción A Los Sistemas InformáticosOscar Uriel Chavez EstradaPas encore d'évaluation

- Estructura Interna Del Computador-2Document37 pagesEstructura Interna Del Computador-2rocco palmettPas encore d'évaluation

- Microcontroladores - Teoria y TiposDocument33 pagesMicrocontroladores - Teoria y TiposJosé Rafael Córdova RangelPas encore d'évaluation

- Capitulo 1 Introducción A Los ComputadorasDocument46 pagesCapitulo 1 Introducción A Los ComputadorasJUAN CARLOS JUAREZPas encore d'évaluation

- Resumen Capitulo10Document4 pagesResumen Capitulo10Alan Mauricio Díaz GuerreroPas encore d'évaluation

- Polanco Luis Miguel Tarea1.Capitulo1Document6 pagesPolanco Luis Miguel Tarea1.Capitulo1Luis miguel PolancoPas encore d'évaluation

- Lógica de CPUDocument5 pagesLógica de CPURafael HernandezPas encore d'évaluation

- Investigación U2. ADC - Alonso Mata AdanDocument20 pagesInvestigación U2. ADC - Alonso Mata AdanADAN ALONSO MATAPas encore d'évaluation

- Modelo Von NewmanDocument32 pagesModelo Von NewmanGuillermoPas encore d'évaluation

- Sistemas OperativosDocument46 pagesSistemas Operativosalma.quinterosquirogaPas encore d'évaluation

- Taller Conceptos Iniciales Sistemas DistribuidosDocument37 pagesTaller Conceptos Iniciales Sistemas DistribuidosHOVAR STEVEN RINCÓN VIANCHÁPas encore d'évaluation

- Desarrollo Prueba 2018Document7 pagesDesarrollo Prueba 2018Mauricio VegaPas encore d'évaluation

- UNIDAD1 ARQUITECTURA EXAMEN 15-17hrs PDFDocument51 pagesUNIDAD1 ARQUITECTURA EXAMEN 15-17hrs PDFsamdiaz10Pas encore d'évaluation

- Estructura y Funcionamiento de La CpuDocument6 pagesEstructura y Funcionamiento de La CpuJose BanquezPas encore d'évaluation

- Organización y Arquitectura de Computadoras. Un Enfoque Práctico-71-97Document27 pagesOrganización y Arquitectura de Computadoras. Un Enfoque Práctico-71-97Kevin CastroPas encore d'évaluation

- Trabajo Sobre La UNIDAD 1 Y UNIDAD 2Document12 pagesTrabajo Sobre La UNIDAD 1 Y UNIDAD 2mauricio armasPas encore d'évaluation

- Transcripción de Estructura y Funcionamiento de La CPUDocument7 pagesTranscripción de Estructura y Funcionamiento de La CPUgermanPas encore d'évaluation

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Desarrollo de componentes software para el manejo de dispositivos. IFCT0609D'EverandDesarrollo de componentes software para el manejo de dispositivos. IFCT0609Pas encore d'évaluation

- Metodología de La Investigación - Sampieri - 6ta EDICIONDocument2 pagesMetodología de La Investigación - Sampieri - 6ta EDICIONMisfort194Pas encore d'évaluation

- Practica de Laboratorio 1,2,3Document8 pagesPractica de Laboratorio 1,2,3Uriel SalinasPas encore d'évaluation

- Sistema de Telefonia MovilDocument206 pagesSistema de Telefonia MovilMarv CastlePas encore d'évaluation

- Programas Gestión de ProyectosDocument120 pagesProgramas Gestión de ProyectosTazann24Pas encore d'évaluation

- Tuto Grabación Stk500 Con AvrdudeDocument4 pagesTuto Grabación Stk500 Con AvrdudeLuis Jimenez EgeaPas encore d'évaluation

- PR 1Document6 pagesPR 1NicoPas encore d'évaluation

- Actividad Integradora Mayo - Primer Año PDFDocument4 pagesActividad Integradora Mayo - Primer Año PDFAsesoria De Matematica En OrientePas encore d'évaluation

- Conformidad de Servicio Oli3Document1 pageConformidad de Servicio Oli3juan yader llantoyccaicoPas encore d'évaluation

- Intersección de Sólidos 1Document22 pagesIntersección de Sólidos 1Cristian MayeerPas encore d'évaluation

- SilaboDocument6 pagesSilabostagi_10Pas encore d'évaluation

- Syllabus Analisis de AlgoritmosDocument3 pagesSyllabus Analisis de AlgoritmosfffPas encore d'évaluation

- A Partir Del Siguiente Enunciado Se Desea Realiza El Modelo Entidad-Relación.Document8 pagesA Partir Del Siguiente Enunciado Se Desea Realiza El Modelo Entidad-Relación.Luis Martin Guevara CondoriPas encore d'évaluation

- La Encuesta y Sus TiposDocument17 pagesLa Encuesta y Sus TiposEduardo GtPas encore d'évaluation

- UniBeast Instalar OS X Mavericks en Cualquier PC Basada en Intel CompatiblesDocument14 pagesUniBeast Instalar OS X Mavericks en Cualquier PC Basada en Intel CompatiblesJose GarciaPas encore d'évaluation

- Taller Variables AleatoriasDocument2 pagesTaller Variables Aleatoriasjuan pereiraPas encore d'évaluation

- Guia 1Document13 pagesGuia 1Armando Cristhian Castro ChaupisPas encore d'évaluation

- Diferencias Siscont y ConcarDocument2 pagesDiferencias Siscont y ConcarAnonymous 9imgu5gF67% (12)

- Leyendas Bosque Seco EcuatorialDocument23 pagesLeyendas Bosque Seco EcuatorialAbdias GCPas encore d'évaluation

- ANEXO, Paradas de EmergenciaDocument5 pagesANEXO, Paradas de Emergenciajsierra333Pas encore d'évaluation

- Unidad 3: MRPDocument6 pagesUnidad 3: MRPlupisPas encore d'évaluation

- Tecnologias BlandasDocument9 pagesTecnologias BlandasMiguel Angel Mandujano LopezPas encore d'évaluation

- Ejemplo Aplicacion UMLDocument24 pagesEjemplo Aplicacion UMLtumamita2004Pas encore d'évaluation

- Mapa Mental TicsDocument1 pageMapa Mental TicsaminsayPas encore d'évaluation

- Tabla de Integrales Indefinidas PDFDocument1 pageTabla de Integrales Indefinidas PDFAndrePas encore d'évaluation

- MCVS-O1-103 Requerimientos de Usuario - TecnicoDocument6 pagesMCVS-O1-103 Requerimientos de Usuario - Tecnicovictor hugoPas encore d'évaluation

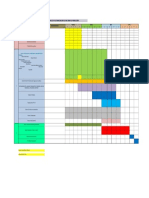

- Cronograma de Actividades - 2018Document1 pageCronograma de Actividades - 2018Arthur Suarez VegaPas encore d'évaluation

- Agenda - Visual Basic Basico - 2018 II Periodo 16-04 (Peraca 474)Document1 pageAgenda - Visual Basic Basico - 2018 II Periodo 16-04 (Peraca 474)Samir RodasPas encore d'évaluation

- Linea de Tiempo Años 90Document1 pageLinea de Tiempo Años 90Angily Paola CruzPas encore d'évaluation

- Semaforo Raspberry Pi 3Document7 pagesSemaforo Raspberry Pi 3Zavala Paéz Alejandro100% (1)

- A258 A259 Span SMDocument576 pagesA258 A259 Span SMesecasiPas encore d'évaluation