Académique Documents

Professionnel Documents

Culture Documents

Aula1 Intro Quartus

Transféré par

Fábio CavarsanCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Aula1 Intro Quartus

Transféré par

Fábio CavarsanDroits d'auteur :

Formats disponibles

Dispositivos Lgicos

Programveis

Introduo ao

Quartus II

Introduo ao Quartus II

"Altera's Quartus II software is such a superior

development environment that I am quickly

forgetting about any other PLD (programmable

logic device) design tool."

Can Nguyen, Principal Staff Engineer,

Broadband Communications Sector, Motorola

"QuartusIIsoftwareissuperiorcomparedtoother

programmablelogictoolofferings,whichallowsus

tofocusourtimeonmeetingcustomerneeds,

ratherthanlaboringovertoolusage.

Dr. Greg Caso, VP Engineering, Escape Communications

Introduo ao Quartus II Caractersticas

Entradas baseadas em texto (VHDL) ou diagrama esquemtico

(block diagram)

Projeto com uso de funes (blocos) de bibliotecas

portas lgicas, flip-flops, pinos e outras primitivas

possibilidade de criao de biblioteca do usurio (permite criao de

smbolos)

Ferramentas para simulao e anlise das sadas dos circuitos

(waveforms)

Software integrado para gerao de sistemas/plataformas: SOPC

Builder

Conselheiro para otimizao de temporizao e recursos

Implementao na plataforma UP1

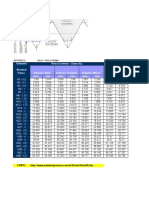

Introduo ao Quartus II Tipos de Arquivos

Introduo ao Quartus II Fluxo

Fluxo

de Desenvolvimento

Concepo do sistema em VHDL ou esquemtico

Submisso das entradas no sistema

Simulao

Correo de erros, quando necessrio

Implementao na UP1

Introduo ao Quartus II Fluxo

Introduo ao Quartus II Ambiente

Ambiente

de Projeto

Criar novo projeto

Entrada esquemtica

Editor

Compilar/mapear circuito no FPGA

Simulao

Resultado

(waveforms)

Ambiente de Projeto

Criar novo projeto

1. Criar novo projeto

2. Criar novo projeto

3. Escolha rea de trabalho

4. Nome do projeto

5. Nome do nvel de hierarquia mais alto do projeto

6. confirmar

Entrada esquemtica

Cria editor esquemtico

Entrada esquemtica - Editor

texto

Portas lgicas/pinos (E/S)

Fios e barramentos

zoom

Full screen on/off

Entrada esquemtica - Editor

primitivas

Portas lgicas/pinos

fios

pino

Compilar/Mapear circuito no FPGA

2. Compilar/mapear o circuito no FPGA

1. Salvar projeto

Compilar/Mapear circuito no FPGA

Simulao

1. Criar sinais para simulao

Simulao

4. Start

2. Click (boto direito)

OK

Sinais escolhidos

3. Selecione sinais p/simulao

4. Escolha sinais

Simulao

Full screen (on/off)

Click sinal de entrada p/formar onda de simulao

Simulao

1.

1.

2.

Gere ondas p/A,B e C.

a. Use um clock (para gerao automtica) ou

b. Gere os valores passo a passo

Ajuste tamanho do grid de amostragem (grid size). Ex: 10 ns

Tempo de simulao. Ex: 100 ns

Simulao

1.

Executar Simulao

Simulao Resultados

Introduo ao Quartus II Laboratrio

Atividade

Desenvolver um circuito de alarme de um automvel com a seguinte

caracterstica funcional: o alarme/advertncia deve ser acionado

quando a ignio estiver acionada (carro ligado) e pelos menos uma

das portas estiver aberta.

Introduo ao Quartus II Laboratrio

Atividade

Etapas do projeto:

Identificar os sinais de entrada e de sada do circuito;

Levantar a tabela verdade do circuito;

Deduzir e otimizar as equaes booleanas da cada sinal de sada;

Implementar o circuito no Quartus II;

Baixar o circuito na UP1 (plataforma de prototipao da Altera).

Essaatividadedeveserapresentada

atofinaldestaaula!

Introduo ao Quartus II UP1

UP1

Placa de prototipao da Altera

Introduo ao Quartus II Sugestes

Sugestes

Introduction to Quartus II (pdf)

www.cin.ufpe.br/~if675/arquivos/referencias/manuais/intro_to_quartus2.pdf

Getting Started With Quartus II Software

http://www.altera.com/products/software/products/quartus2/getting-started/qtsgetting-started.html

Quartus II Development Software Version 6.0

Literature

http://www.altera.com/literature/lit-qts.jsp

Sugesto

de Leitura:

de download:

Quartus II Web Edition Software Version 6.0

http://www.altera.com/products/software/products/quartus2web/sofquarwebmain.html

Vous aimerez peut-être aussi

- O Papel Da Internet Na Redução Da Pirataria No BrasilDocument2 pagesO Papel Da Internet Na Redução Da Pirataria No BrasilANDRE LUIZ RAMOS LINOPas encore d'évaluation

- 5-Apostila CubagemDocument30 pages5-Apostila CubagemREYNALDO MAMANIPas encore d'évaluation

- Odisseias - VoucherPDF 221203 162124Document1 pageOdisseias - VoucherPDF 221203 162124Maria SantosPas encore d'évaluation

- Controlando ESP32 Via WiFi Com Validação Por MACADRESSDocument19 pagesControlando ESP32 Via WiFi Com Validação Por MACADRESSdalton vidorPas encore d'évaluation

- Negociacao Modelo HarvardDocument3 pagesNegociacao Modelo HarvardCorporativa Brasil Cursos On-LinePas encore d'évaluation

- Aula 24Document28 pagesAula 24joda gomes britoPas encore d'évaluation

- TJ 19maioDocument3 pagesTJ 19maiogeorgedantasPas encore d'évaluation

- Aula 1 - ALGADocument47 pagesAula 1 - ALGAFabian LemosPas encore d'évaluation

- Geoprocessamento e Logística: Potencializando Resultados Com o Uso Da Tecnologia SIGDocument8 pagesGeoprocessamento e Logística: Potencializando Resultados Com o Uso Da Tecnologia SIGRamon Leal PessôaPas encore d'évaluation

- Them Bombs - Manual (PT Tablet-iPad 1.4)Document27 pagesThem Bombs - Manual (PT Tablet-iPad 1.4)WellingtonPas encore d'évaluation

- EstagioDocument12 pagesEstagioWilson PavãoPas encore d'évaluation

- Fluxograma Com As Técnicas de Vendas Do MEODocument1 pageFluxograma Com As Técnicas de Vendas Do MEOgrelha_tvPas encore d'évaluation

- Normas Elementos FixaçãoDocument6 pagesNormas Elementos FixaçãoGuilherme MendonçaPas encore d'évaluation

- Leia MeUpdV19Document10 pagesLeia MeUpdV19ivanilson zeula motomboPas encore d'évaluation

- Manual - Excel Intermédio e AvançadoDocument72 pagesManual - Excel Intermédio e AvançadoPaulo SousaPas encore d'évaluation

- Aprender Japones PlusDocument67 pagesAprender Japones PlusJoacy100% (1)

- Telecurso 2000 - Ensino Fund - Matemática 75Document4 pagesTelecurso 2000 - Ensino Fund - Matemática 75Matematica TC100% (1)

- InvoiceDocument8 pagesInvoiceedsonsilvafrinstalacoesPas encore d'évaluation

- Ortog On Line MagDocument110 pagesOrtog On Line MagCicero MoraesPas encore d'évaluation

- Manipulacao de Dados Com SQL Demo PDFDocument26 pagesManipulacao de Dados Com SQL Demo PDFJacqueline Karla AlvesPas encore d'évaluation

- VT 5000Document38 pagesVT 5000Flávio Alves TeixeiraPas encore d'évaluation

- Ensaio JobsDocument12 pagesEnsaio JobsCarla BertulezaPas encore d'évaluation

- JBL GO VM ManualDocument10 pagesJBL GO VM Manualfraustro2Pas encore d'évaluation

- UserDocument20 pagesUserMain soraka boladaPas encore d'évaluation

- Processamento Pedidos Servico Cliente - LOGISTICA - CEPADocument58 pagesProcessamento Pedidos Servico Cliente - LOGISTICA - CEPAClaudilenePas encore d'évaluation

- UC15.Serviços de RedesDocument132 pagesUC15.Serviços de RedesTaumar MoraisPas encore d'évaluation

- Manual - App UnimedPoaDocument11 pagesManual - App UnimedPoaGabriel LealPas encore d'évaluation

- PDF Auto Reset DemoDocument3 pagesPDF Auto Reset DemoMaxsaniel MedeirosPas encore d'évaluation

- Curso de Atpdraw p01 2016.1Document107 pagesCurso de Atpdraw p01 2016.1IgorFortal100% (2)

- Lista OficialDocument8 pagesLista OficialDarvin Perez HuaranccaPas encore d'évaluation