Académique Documents

Professionnel Documents

Culture Documents

Chapter 02

Transféré par

estraj19540 évaluation0% ont trouvé ce document utile (0 vote)

24 vues92 pagesDigital Logic Families

Copyright

© © All Rights Reserved

Formats disponibles

PPT, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDigital Logic Families

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPT, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

24 vues92 pagesChapter 02

Transféré par

estraj1954Digital Logic Families

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPT, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 92

Chapter 2

Combinational Logic Design

Copyright © 2013 Elsevier Inc. All rights reserved. 1

Figure 2.1 Circuit as a black box with inputs, outputs, and specifications

Copyright © 2013 Elsevier Inc. All rights reserved. 2

Figure 2.2 Elements and nodes

Copyright © 2013 Elsevier Inc. All rights reserved. 3

Figure 2.3 Combinational logic circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 4

Figure 2.4 Two OR implementations

Copyright © 2013 Elsevier Inc. All rights reserved. 5

Figure 2.5 Multiple-output combinational circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 6

Figure 2.6 Slash notation for multiple signals

Copyright © 2013 Elsevier Inc. All rights reserved. 7

Figure 2.7 Example circuits

Copyright © 2013 Elsevier Inc. All rights reserved. 8

Figure 2.8 Truth table and minterms

Copyright © 2013 Elsevier Inc. All rights reserved. 9

Figure 2.9 Truth table with multiple TRUE minterms

Copyright © 2013 Elsevier Inc. All rights reserved. 10

Figure 2.10 Ben’s truth table

Copyright © 2013 Elsevier Inc. All rights reserved. 11

Figure 2.11 Ben’s circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 12

Figure 2.12 Random three-input truth table

Copyright © 2013 Elsevier Inc. All rights reserved. 13

Figure 2.13 Truth table with multiple FALSE maxterms

Copyright © 2013 Elsevier Inc. All rights reserved. 14

Figure 2.14 Identity theorem in hardware: (a) T1, (b) T1′

Copyright © 2013 Elsevier Inc. All rights reserved. 15

Figure 2.15 Null element theorem in hardware: (a) T2, (b) T2′

Copyright © 2013 Elsevier Inc. All rights reserved. 16

Figure 2.16 Idempotency theorem in hardware: (a) T3, (b) T3′

Copyright © 2013 Elsevier Inc. All rights reserved. 17

Figure 2.17 Involution theorem in hardware: T4

Copyright © 2013 Elsevier Inc. All rights reserved. 18

Figure 2.18 Complement theorem in hardware: (a) T5, (b) T5′

Copyright © 2013 Elsevier Inc. All rights reserved. 19

Figure 2.19 De Morgan equivalent gates

Copyright © 2013 Elsevier Inc. All rights reserved. 20

Figure 2.20 Truth table showing Y and

Copyright © 2013 Elsevier Inc. All rights reserved. 21

Figure 2.21 Truth table showing minterms for

Copyright © 2013 Elsevier Inc. All rights reserved. 22

Figure 2.22 Truth table proving T11

Copyright © 2013 Elsevier Inc. All rights reserved. 23

Figure 2.23 Schematic of

Copyright © 2013 Elsevier Inc. All rights reserved. 24

Figure 2.24 Wire connections

Copyright © 2013 Elsevier Inc. All rights reserved. 25

Figure 2.25 Schematic of

Copyright © 2013 Elsevier Inc. All rights reserved. 26

Figure 2.26 Schematic using fewer gates

Copyright © 2013 Elsevier Inc. All rights reserved. 27

Figure 2.27 Priority circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 28

Figure 2.28 Priority circuit schematic

Copyright © 2013 Elsevier Inc. All rights reserved. 29

Figure 2.29 Priority circuit truth table with don’t cares (X’s)

Copyright © 2013 Elsevier Inc. All rights reserved. 30

Figure 2.30 Three-input XOR: (a) functional specification and (b) two-level logic

implementation

Copyright © 2013 Elsevier Inc. All rights reserved. 31

Figure 2.31 Three-input XOR using two-input XORs

Copyright © 2013 Elsevier Inc. All rights reserved. 32

Figure 2.32 Eight-input XOR using seven two-input XORs

Copyright © 2013 Elsevier Inc. All rights reserved. 33

Figure 2.33 Multilevel circuit using NANDs and NORs

Copyright © 2013 Elsevier Inc. All rights reserved. 34

Figure 2.34 Bubble-pushed circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 35

Figure 2.35 Logically equivalent bubble-pushed circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 36

Figure 2.36 Circuit using ANDs and ORs

Copyright © 2013 Elsevier Inc. All rights reserved. 37

Figure 2.37 Poor circuit using NANDs and NORs

Copyright © 2013 Elsevier Inc. All rights reserved. 38

Figure 2.38 Better circuit using NANDs and NORs

Copyright © 2013 Elsevier Inc. All rights reserved. 39

Figure 2.39 Circuit with contention

Copyright © 2013 Elsevier Inc. All rights reserved. 40

Figure 2.40 Tristate buffer

Copyright © 2013 Elsevier Inc. All rights reserved. 41

Figure 2.41 Tristate buffer with active low enable

Copyright © 2013 Elsevier Inc. All rights reserved. 42

Figure 2.42 Tristate bus connecting multiple chips

Copyright © 2013 Elsevier Inc. All rights reserved. 43

Figure 2.43 Three-input function: (a) truth table, (b) K-map, (c) K-map

showing minterms

Copyright © 2013 Elsevier Inc. All rights reserved. 44

Figure 2.44 K-map minimization

Copyright © 2013 Elsevier Inc. All rights reserved. 45

Figure 2.45 K-map for Example 2.9

Copyright © 2013 Elsevier Inc. All rights reserved. 46

Figure 2.46 Solution for Example 2.9

Copyright © 2013 Elsevier Inc. All rights reserved. 47

Figure 2.47 Seven-segment display decoder icon

Copyright © 2013 Elsevier Inc. All rights reserved. 48

Figure 2.48 Seven-segment display digits

Copyright © 2013 Elsevier Inc. All rights reserved. 49

Figure 2.49 Karnaugh maps for Sa and Sb

Copyright © 2013 Elsevier Inc. All rights reserved. 50

Figure 2.50 K-map solution for Example 2.10

Copyright © 2013 Elsevier Inc. All rights reserved. 51

Figure 2.51 Alternative K-map for Sa showing different set of

prime implicants

Copyright © 2013 Elsevier Inc. All rights reserved. 52

Figure 2.52 Alternative K-map for Sa showing incorrect nonprime

implicant

Copyright © 2013 Elsevier Inc. All rights reserved. 53

Figure 2.53 K-map solution with don’t cares

Copyright © 2013 Elsevier Inc. All rights reserved. 54

Figure 2.54 2:1 multiplexer symbol and truth table

Copyright © 2013 Elsevier Inc. All rights reserved. 55

Figure 2.55 2:1 multiplexer implementation using two-level

logic

Copyright © 2013 Elsevier Inc. All rights reserved. 56

Figure 2.56 Multiplexer using tristate buffers

Copyright © 2013 Elsevier Inc. All rights reserved. 57

Figure 2.57 4:1 multiplexer

Copyright © 2013 Elsevier Inc. All rights reserved. 58

Figure 2.58 4:1 multiplexer implementations: (a) two-level logic, (b)

tristates, (c) hierarchical

Copyright © 2013 Elsevier Inc. All rights reserved. 59

Figure 2.59 4:1 multiplexer implementation of two-input AND

function

Copyright © 2013 Elsevier Inc. All rights reserved. 60

Figure 2.60 Multiplexer logic using variable inputs

Copyright © 2013 Elsevier Inc. All rights reserved. 61

Figure 2.61 Alyssa’s circuit: (a) truth table, (b) 8:1 multiplexer implementation

Copyright © 2013 Elsevier Inc. All rights reserved. 62

Figure 2.62 Alyssa’s new circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 63

Figure 2.63 2:4 decoder

Copyright © 2013 Elsevier Inc. All rights reserved. 64

Figure 2.64 2:4 decoder implementation

Copyright © 2013 Elsevier Inc. All rights reserved. 65

Figure 2.65 Logic function using decoder

Copyright © 2013 Elsevier Inc. All rights reserved. 66

Figure 2.66 Circuit delay

Copyright © 2013 Elsevier Inc. All rights reserved. 67

Figure 2.67 Propagation and contamination delay

Copyright © 2013 Elsevier Inc. All rights reserved. 68

Figure 2.68 Short path and critical path

Copyright © 2013 Elsevier Inc. All rights reserved. 69

Figure 2.69 Critical and short path waveforms

Copyright © 2013 Elsevier Inc. All rights reserved. 70

Figure 2.70 Ben’s circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 71

Figure 2.71 Ben’s critical path

Copyright © 2013 Elsevier Inc. All rights reserved. 72

Figure 2.72 Ben’s shortest path

Copyright © 2013 Elsevier Inc. All rights reserved. 73

Figure 2.73 4:1 multiplexer propagation delays: (a) two-level logic, (b) tristate

Copyright © 2013 Elsevier Inc. All rights reserved. 74

Figure 2.74 4:1 multiplexer propagation delays: hierarchical using 2:1

multiplexers

Copyright © 2013 Elsevier Inc. All rights reserved. 75

Figure 2.75 Circuit with a glitch

Copyright © 2013 Elsevier Inc. All rights reserved. 76

Figure 2.76 Timing of a glitch

Copyright © 2013 Elsevier Inc. All rights reserved. 77

Figure 2.77 Input change crosses implicant boundary

Copyright © 2013 Elsevier Inc. All rights reserved. 78

Figure 2.78 K-map without glitch

Copyright © 2013 Elsevier Inc. All rights reserved. 79

Figure 2.79 Circuit without glitch

Copyright © 2013 Elsevier Inc. All rights reserved. 80

Figure 2.80 Truth tables for Exercises 2.1 and 2.3

Copyright © 2013 Elsevier Inc. All rights reserved. 81

Figure 2.81 Truth tables for Exercises 2.2 and 2.4

Copyright © 2013 Elsevier Inc. All rights reserved. 82

Figure 2.82 Circuit schematic

Copyright © 2013 Elsevier Inc. All rights reserved. 83

Figure 2.83 Circuit schematic

Copyright © 2013 Elsevier Inc. All rights reserved. 84

Figure 2.84 Circuit schematic

Copyright © 2013 Elsevier Inc. All rights reserved. 85

Figure 2.85 Truth table for Exercise 2.28

Copyright © 2013 Elsevier Inc. All rights reserved. 86

Figure 2.86 Truth table for Exercise 2.31

Copyright © 2013 Elsevier Inc. All rights reserved. 87

Figure 2.87 Multiplexer circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 88

Figure 2.88 Multiplexer circuit

Copyright © 2013 Elsevier Inc. All rights reserved. 89

Figure M 01

Copyright © 2013 Elsevier Inc. All rights reserved. 90

Figure M 02

Copyright © 2013 Elsevier Inc. All rights reserved. 91

UNN Figure 1

Copyright © 2013 Elsevier Inc. All rights reserved. 92

Vous aimerez peut-être aussi

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- An10587 PDFDocument11 pagesAn10587 PDFestraj1954Pas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- DKD-R 8-1 Englisch NeuDocument32 pagesDKD-R 8-1 Englisch Neugsv988Pas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Chap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)Document62 pagesChap. 8 Integrated-Circuit Logic Families: Chapter Outcomes (Objectives)estraj1954Pas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- ULN2803APG Datasheet en 20121126Document13 pagesULN2803APG Datasheet en 20121126Kang JadiJaya Otodidak100% (1)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- DKD-R 8-1 Englisch NeuDocument32 pagesDKD-R 8-1 Englisch Neugsv988Pas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Uart Spi I2cDocument17 pagesUart Spi I2cestraj1954100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Wems Electronics: EMI/EMC Filters: A Technical PresentationDocument55 pagesWems Electronics: EMI/EMC Filters: A Technical PresentationHilmi SanusiPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Parallel I/O Interface: Memory Actuator Output DeviceDocument14 pagesParallel I/O Interface: Memory Actuator Output Deviceestraj1954Pas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devotional When God SpeaksDocument8 pagesDevotional When God Speaksestraj1954Pas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- An 10587Document11 pagesAn 10587estraj1954Pas encore d'évaluation

- I2c BusDocument41 pagesI2c BusSoethree Yono100% (2)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- P-Values Explained by Data Scientist For Data ScientistsDocument8 pagesP-Values Explained by Data Scientist For Data Scientistsestraj1954Pas encore d'évaluation

- Spi I2c UartDocument1 pageSpi I2c Uartestraj1954100% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Development of A Perforated Diffusive Muffler For A Regenerative BlowerDocument8 pagesDevelopment of A Perforated Diffusive Muffler For A Regenerative Blowerestraj1954Pas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- ADu CM350Document17 pagesADu CM350estraj1954Pas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Clock Oscillators Surface Mount Type KC3225A-C3 Series: Features How To OrderDocument1 pageClock Oscillators Surface Mount Type KC3225A-C3 Series: Features How To Orderestraj1954Pas encore d'évaluation

- Unit I Mathematical Tools 1.1 Basic Mathematics For Physics: I. Quadratic Equation and Its SolutionDocument16 pagesUnit I Mathematical Tools 1.1 Basic Mathematics For Physics: I. Quadratic Equation and Its SolutionJit AggPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

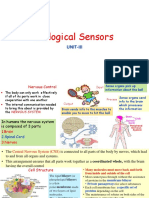

- Biological Sensors: Unit-IiiDocument64 pagesBiological Sensors: Unit-Iiiestraj1954Pas encore d'évaluation

- IDT SensingTechandSensorSolutions OVR 2018117Document16 pagesIDT SensingTechandSensorSolutions OVR 2018117estraj1954Pas encore d'évaluation

- Lecture Notes Methods of Mathematical Physics MATHDocument71 pagesLecture Notes Methods of Mathematical Physics MATHestraj1954Pas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Deep Learning Tutorial: Release 0.1Document137 pagesDeep Learning Tutorial: Release 0.1estraj1954Pas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- ADuCM350 PDFDocument40 pagesADuCM350 PDFestraj1954Pas encore d'évaluation

- Lecture Notes Methods of Mathematical Physics MATHDocument71 pagesLecture Notes Methods of Mathematical Physics MATHestraj1954Pas encore d'évaluation

- Biomedical Engineering EducationDocument4 pagesBiomedical Engineering Educationestraj1954Pas encore d'évaluation

- Bidirectional Current Source-TIDocument9 pagesBidirectional Current Source-TIestraj1954100% (1)

- Measurement Instrumentation PDFDocument10 pagesMeasurement Instrumentation PDFestraj1954Pas encore d'évaluation

- Code:: Ckielstra SuggestionDocument37 pagesCode:: Ckielstra Suggestionestraj1954100% (1)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Submersible Level TransmitterDocument1 pageSubmersible Level Transmitterestraj1954100% (1)

- Measurement Systems IntroductionDocument46 pagesMeasurement Systems Introductionsonu thiglePas encore d'évaluation

- Cs6201 Digital Principles and System Design: Unit IDocument19 pagesCs6201 Digital Principles and System Design: Unit IUttam NeelapureddyPas encore d'évaluation

- List of 7400 Series Integrated CircuitsDocument41 pagesList of 7400 Series Integrated CircuitsmanikandanPas encore d'évaluation

- Ldica Unit IVDocument72 pagesLdica Unit IV19501A0459 MAKANA PRASANNA LAKSHMIPas encore d'évaluation

- TMUX1109 5 V, 2.5 V, Low-Leakage-Current, 4:1, 2-Channel Precision MultiplexerDocument41 pagesTMUX1109 5 V, 2.5 V, Low-Leakage-Current, 4:1, 2-Channel Precision MultiplexerHaroldo CurtiPas encore d'évaluation

- Table of Electrical SymbolsDocument9 pagesTable of Electrical SymbolsmajanePas encore d'évaluation

- PGD An31n PDFDocument8 pagesPGD An31n PDFHaresh KPas encore d'évaluation

- Ie Ii-2011Document25 pagesIe Ii-2011Sagar PawarPas encore d'évaluation

- Curtis DC To 3 Phase Ac Motor Controller 1230Document72 pagesCurtis DC To 3 Phase Ac Motor Controller 1230Cykhong Khong0% (1)

- Multiplexer & DemultiplexerDocument22 pagesMultiplexer & DemultiplexerANJALI PATELPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- CS0413 Vlsi and Embedded System DesignDocument78 pagesCS0413 Vlsi and Embedded System DesignDr-Eng Imad A. ShaheenPas encore d'évaluation

- CO UNIT-2 NotesDocument35 pagesCO UNIT-2 NotesAmber HeardPas encore d'évaluation

- CD405xB CMOS Single 8-Channel Analog Multiplexer/Demultiplexer With Logic-Level ConversionDocument43 pagesCD405xB CMOS Single 8-Channel Analog Multiplexer/Demultiplexer With Logic-Level Conversionjohny cokechePas encore d'évaluation

- E-Cad and Vlsi LabDocument59 pagesE-Cad and Vlsi LabSsgn SrinivasaraoPas encore d'évaluation

- Digital ElectronicsDocument22 pagesDigital ElectronicsDhruv Paul100% (1)

- Digital Logic Design Chapter 5Document28 pagesDigital Logic Design Chapter 5Okezaki TemoyoPas encore d'évaluation

- BTS Label SetsDocument23 pagesBTS Label SetsRupesh PatelPas encore d'évaluation

- 74LS138Document5 pages74LS138jidul16Pas encore d'évaluation

- Unit Viii Cmos Testing: DefinitionDocument22 pagesUnit Viii Cmos Testing: DefinitionlokeshwarrvrjcPas encore d'évaluation

- FURQANDocument39 pagesFURQANsamsPas encore d'évaluation

- FBGA TutorialDocument6 pagesFBGA TutorialHamzeh AhmadPas encore d'évaluation

- Digital Manual FOR II CSEDocument49 pagesDigital Manual FOR II CSEMohanaprakash EcePas encore d'évaluation

- MCQ EdugripDocument109 pagesMCQ EdugripArasanfiveStevenPas encore d'évaluation

- Fanuc IC697VRD008 User ManualDocument59 pagesFanuc IC697VRD008 User ManualsunhuynhPas encore d'évaluation

- A-51x Series Distributed Control SystemDocument14 pagesA-51x Series Distributed Control SystemMarcelo ChocaPas encore d'évaluation

- Unit 3 DCN Lecture Notes 23 45Document41 pagesUnit 3 DCN Lecture Notes 23 45arun kaushikPas encore d'évaluation

- Agilent Data-Acquisition TES-34970A DatasheetDocument28 pagesAgilent Data-Acquisition TES-34970A DatasheetTeq ShoPas encore d'évaluation

- cd74hc4051 q1Document18 pagescd74hc4051 q1richardleonn2Pas encore d'évaluation

- 2 - Combinational Logic CircuitsDocument56 pages2 - Combinational Logic CircuitsSiegrique Ceasar A. JalwinPas encore d'évaluation

- Module - 08 F2833x Analogue Digital ConverterDocument28 pagesModule - 08 F2833x Analogue Digital ConverterMaria MEKLIPas encore d'évaluation

- MLLNDocument13 pagesMLLNksu2006100% (5)

- The Ancestor's Tale: A Pilgrimage to the Dawn of EvolutionD'EverandThe Ancestor's Tale: A Pilgrimage to the Dawn of EvolutionÉvaluation : 4 sur 5 étoiles4/5 (811)

- Fire Season: Field Notes from a Wilderness LookoutD'EverandFire Season: Field Notes from a Wilderness LookoutÉvaluation : 4 sur 5 étoiles4/5 (142)

- Alex & Me: How a Scientist and a Parrot Discovered a Hidden World of Animal Intelligence—and Formed a Deep Bond in the ProcessD'EverandAlex & Me: How a Scientist and a Parrot Discovered a Hidden World of Animal Intelligence—and Formed a Deep Bond in the ProcessPas encore d'évaluation

- Dark Matter and the Dinosaurs: The Astounding Interconnectedness of the UniverseD'EverandDark Matter and the Dinosaurs: The Astounding Interconnectedness of the UniverseÉvaluation : 3.5 sur 5 étoiles3.5/5 (69)

- Wayfinding: The Science and Mystery of How Humans Navigate the WorldD'EverandWayfinding: The Science and Mystery of How Humans Navigate the WorldÉvaluation : 4.5 sur 5 étoiles4.5/5 (18)