Académique Documents

Professionnel Documents

Culture Documents

Timimg Diagram

Transféré par

zxcddxzcdzxsc0 évaluation0% ont trouvé ce document utile (0 vote)

164 vues27 pagesTitre original

Timimg Diagram.pptx

Copyright

© © All Rights Reserved

Formats disponibles

PPTX, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPTX, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

164 vues27 pagesTimimg Diagram

Transféré par

zxcddxzcdzxscDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PPTX, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 27

Minimum mode & Maximum

Mode Timing Diagram

Sangeeta Ranjan

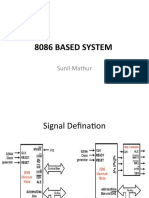

Minimum Mode 8086 System

• In a minimum mode 8086 system, the

microprocessor 8086 is operated in minimum

mode by strapping its MN/MX pin to logic 1.

• In this mode, all the control signals are given out

by the microprocessor chip itself. There is a single

microprocessor in the minimum mode system.

• The remaining components in the system are

latches, transreceivers, clock generator, memory

and I/O devices.

Minimum Mode 8086 System Design

• The clock generator generates the clock from the crystal

oscillator and then shapes it and divides to make it more

precise so that it can be used as an accurate timing

reference for the system.

• The clock generator also synchronizes some external

signal with the system clock.

• It has 20 address lines and 16 data lines, the 8086 CPU

requires three octal address latches and two octal data

buffers for the complete address and data separation.

Minimum Mode 8086 System Design

• The working of the minimum mode configuration system

can be better described in terms of the timing diagrams

rather than qualitatively describing the operations.

• The opcode fetch and read cycles are similar. Hence the

timing diagram can be categorized in two parts, the first is

the timing diagram for read cycle and the second is the

timing diagram for write cycle.

• The read cycle begins in T1 with the assertion of address

latch enable (ALE) signal and also M / IO signal. During

the negative going edge of this signal, the valid address is

latched on the local bus.

Minimum Mode 8086 System Design

• The working of the minimum mode configuration system

can be better described in terms of the timing diagrams

rather than qualitatively describing the operations.

• The opcode fetch and read cycles are similar. Hence the

timing diagram can be categorized in two parts, the first is

the timing diagram for read cycle and the second is the

timing diagram for write cycle.

• The read cycle begins in T1 with the assertion of address

latch enable (ALE) signal and also M / IO signal. During

the negative going edge of this signal, the valid address is

latched on the local bus.

General Bus Operation

• The 8086 has a combined address and data bus commonly

referred as a time multiplexed address and data bus. The

main reason behind multiplexing address and data over the

same pins is the maximum utilization of processor pins and

it facilitates the use of 40 pin standard DIP package.

• The bus can be DE multiplexed using a few latches and

trans receivers, when ever required.

• Basically, all the processor bus cycles consist of at least four

clock cycles. These are referred to as T1, T2, T3, T4. The

address is transmitted by the processor during T1. It is

present on the bus only for one cycle.

Minimum Mode 8086 System Design

• The BHE and A0 signals address low, high or both bytes.

From T1 to T4 , the M/IO signal indicates a memory or I/O

operation.

• At T2, the address is removed from the local bus and is

sent to the output. The bus is then tristate. The read (RD)

control signal is also activated in T2.

• The read (RD) signal causes the address device to enable

its data bus drivers. After RD goes low, the valid data is

available on the data bus.

• The addressed device will drive the READY line high.

When the processor returns the read signal to high level,

the addressed device will again tristate its bus drivers.

Minimum Mode 8086 System Design

A write cycle also begins with the assertion of ALE and

the emission of the address. The M/IO signal is again

asserted to indicate a memory or I/O operation. In T2, after

sending the address in T1, the processor sends the data to

be written to the addressed location.

• The data remains on the bus until middle of T4 state. The

WR becomes active at the beginning of T2 (unlike RD is

somewhat delayed in T2 to provide time for floating).

• The BHE and A0 signals are used to select the proper byte

or bytes of memory or I/O word to be read or write.

• The M/IO, RD and WR signals indicate the type of data

transfer as specified in table below.

Write Cycle Timing Diagram for Minimum Mode

Read Cycle Timing Diagram for Minimum Mode

Read Cycle Timing Diagram for Minimum Mode

Read Cycle Timing Diagram for Minimum Mode

• Hold Response sequence:

The HOLD pin is checked at leading edge of each clock

pulse. If it is received active by the processor before

T4 of the previous cycle or during T1 state of the

current cycle, the CPU activates HLDA in the next

clock cycle and for succeeding bus cycles, the bus will

be given to another requesting master.

• The control of the bus is not regained by the processor

until the requesting master does not drop the HOLD pin

low. When the request is dropped by the requesting

master, the HLDA is dropped by the processor at the

trailing edge of the next clock.

Read Cycle Timing Diagram for Minimum Mode

Bus Request and Bus Grant Timings in

Minimum Mode System

Maximum Mode Interface

• When the 8086 is set for the maximum-mode

configuration, it provides signals for implementing a

multiprocessor / coprocessor system environment.

• By multiprocessor environment we mean that one

microprocessor exists in the system and that each

processor is executing its own program.

• Usually in this type of system environment, there are

some system resources that are common to all processors.

• They are called as global resources. There are also other

resources that are assigned to specific processors. These

are known as local or private resources.

Maximum Mode Interface

• Coprocessor also means that there is a second processor in

the system. In this two processor does not access the bus at

the same time.

• One passes the control of the system bus to the other and

then may suspend its operation.

• In the maximum-mode 8086 system, facilities are provided

for implementing allocation of global resources and passing

bus control to other microprocessor or coprocessor.

Maximum Mode Interface

• 8288 Bus Controller – Bus Command and Control +Signals:

8086 does not directly provide all the signals that

are required to control the memory, I/O and interrupt

interfaces.

• Specially the WR, M/IO, DT/R, DEN, ALE and INTA,

signals are no longer produced by the 8086. Instead it

outputs three status signals S0, S1, S2 prior to the initiation

of each bus cycle. This 3- bit bus status code identifies

which type of bus cycle is to follow.

• S2S1S0 are input to the external bus controller device, the

bus controller generates the appropriately timed command

and control signals.

Maximum Mode Interface

• The 8288 produces one or two of these eight command

signals for each bus cycles. For instance, when the 8086

outputs the code S2S1S0 equals 001, it indicates that an I/O

read cycle is to be performed.

• In the code 111 is output by the 8086, it is signaling that no

bus activity is to take place.

• The control outputs produced by the 8288 are DEN, DT/R

and ALE. These 3 signals provide the same functions as

those described for the minimum system mode. This set of

bus commands and control signals is compatible with the

Multibus and industry standard for interfacing microprocessor

systems.

Maximum Mode Interface

• • In a minimum mode 8086 system, the microprocessor

8086 is operated in minimum mode by strapping its

MN/MX pin to logic 1.

• In this mode, all the control signals are given out by the

microprocessor chip itself. There is a single

microprocessor in the minimum mode system.

• The remaining components in the system are latches,

transreceivers, clock generator, memory and I/O devices.

Some type of chip selection logic may be required for

selecting memory or I/O devices, depending upon the

address map of the system.

Maximum Mode Interface

• Here the only difference between in timing diagram

between minimum mode and maximum mode is the status

signals used and the available control and advanced

command signals.

• R0, S1, S2 are set at the beginning of bus cycle.8288 bus

controller will output a pulse as on the ALE and apply a

required signal to its DT / R pin during T1

• In T2, 8288 will set DEN=1 thus enabling transceivers, and

• for an input it will activate MRDC or IORC. These signals

• are activated until T4. For an output, the AMWC or

• AIOWC is activated from T2 to T4 and MWTC or IOWC is

• activated from T3 to T4.

Timing Diagram in maximum

modes

References

• For more Notes Follow

http://www.edutechlearners.com

• https://www.geeksforgeeks.org/timing-diagra

m-of-inr-m/

• https://www.geeksforgeeks.org/timing-diagra

m-of-mov-instruction-in-microprocessor/

Vous aimerez peut-être aussi

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationD'EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationPas encore d'évaluation

- Features and Modes of 8086Document11 pagesFeatures and Modes of 8086ABHishekPas encore d'évaluation

- Unit II 8086 SYSTEM Bus Structure: BookDocument194 pagesUnit II 8086 SYSTEM Bus Structure: BookGomathi PsPas encore d'évaluation

- Ec6504 MPMC Unit 2Document194 pagesEc6504 MPMC Unit 2dkPas encore d'évaluation

- Pin Diagram of 8086Document21 pagesPin Diagram of 8086Radha SudheeraPas encore d'évaluation

- Microprocessor (ECC15101)Document10 pagesMicroprocessor (ECC15101)MATAVALAM CHANDU PRIYAPas encore d'évaluation

- Minimum and Maximum ModesDocument21 pagesMinimum and Maximum ModesSubash BasnyatPas encore d'évaluation

- Berry B Brey Part IDocument49 pagesBerry B Brey Part Ikalpesh_chandakPas encore d'évaluation

- Minimum and Maximum Mode of 8086Document9 pagesMinimum and Maximum Mode of 8086Ankit KumarPas encore d'évaluation

- Iii UnitDocument27 pagesIii UnitDilip Kumar AhirwarPas encore d'évaluation

- 21CS1302 - Camp - Unit 4 NotesDocument41 pages21CS1302 - Camp - Unit 4 Notespec libraryPas encore d'évaluation

- Unit III MPMC MaterialDocument33 pagesUnit III MPMC Materialsree2728Pas encore d'évaluation

- Pin Diagram of 8086Document21 pagesPin Diagram of 8086adithya123456100% (5)

- Microprocessors: BY: Prof. Dileep J Dept. of TCE K.S.I.TDocument16 pagesMicroprocessors: BY: Prof. Dileep J Dept. of TCE K.S.I.TsenthilPas encore d'évaluation

- Overview or Features of 8086Document33 pagesOverview or Features of 8086Supraja SundaresanPas encore d'évaluation

- Signal Groups of 8086Document18 pagesSignal Groups of 8086Macdonald DanielPas encore d'évaluation

- Maximum Mode 8086 SystemDocument9 pagesMaximum Mode 8086 Systemchenna838Pas encore d'évaluation

- Memory and Input Output InterfaceDocument16 pagesMemory and Input Output Interfacerobern ndoloPas encore d'évaluation

- 8086 NotesDocument43 pages8086 NotesSuma LathaPas encore d'évaluation

- MP8085 2Document38 pagesMP8085 2Ravi TejaPas encore d'évaluation

- Nri Group of Institution: - Prepared By: - Nikhil Kumar - Enroll No: 0511ec111056 - NirtDocument8 pagesNri Group of Institution: - Prepared By: - Nikhil Kumar - Enroll No: 0511ec111056 - NirtVishal PanwarPas encore d'évaluation

- The 8086 Microprocessor Architecture: (8086 Datasheet)Document31 pagesThe 8086 Microprocessor Architecture: (8086 Datasheet)Feyisa BekelePas encore d'évaluation

- 6 Maximum ModeDocument23 pages6 Maximum ModeTejaswi NisanthPas encore d'évaluation

- 8086 Min Max Modes ETCDocument17 pages8086 Min Max Modes ETCNageswara RaoPas encore d'évaluation

- Unit 2 NotesDocument26 pagesUnit 2 Notesabishek abiPas encore d'évaluation

- Minimum and Maximum Mode CPU ConfigurationDocument21 pagesMinimum and Maximum Mode CPU ConfigurationAmitabh DixitPas encore d'évaluation

- MIC Chap 1 NotesDocument15 pagesMIC Chap 1 NotesSonali AhirePas encore d'évaluation

- Unit 3 8086 Microprocessor InterfacingDocument29 pagesUnit 3 8086 Microprocessor InterfacingDere JesusPas encore d'évaluation

- Minimum and Maximum Mode of 8086 of 8086: Sutapa SarkarDocument26 pagesMinimum and Maximum Mode of 8086 of 8086: Sutapa SarkarNishal Bharadwaj NPas encore d'évaluation

- Minimum and Maximum Modes of 8086Document3 pagesMinimum and Maximum Modes of 8086Riya Chaudhary100% (1)

- Digital Logic and Microprocessor: Dr.M.Sindhuja Assistant Professor (Senior Grade) School of Electronics Vit, ChennaiDocument52 pagesDigital Logic and Microprocessor: Dr.M.Sindhuja Assistant Professor (Senior Grade) School of Electronics Vit, ChennaiNithish Kumar A NPas encore d'évaluation

- Panashe Mushinyi H180524V SE Department Microprocessor and Embeded Systems Assignment 1 and 2Document6 pagesPanashe Mushinyi H180524V SE Department Microprocessor and Embeded Systems Assignment 1 and 2panashePas encore d'évaluation

- 8086 Signals & Configurations: Bipin Krishna Assistant Professor ICE Department, MIT, Manipal Manipal UniversityDocument13 pages8086 Signals & Configurations: Bipin Krishna Assistant Professor ICE Department, MIT, Manipal Manipal UniversityBipin KrishnaPas encore d'évaluation

- 8086 Pin DiagramDocument9 pages8086 Pin Diagram12343567890100% (2)

- Pin Diagram of 8086 and Pin Description of 8086Document12 pagesPin Diagram of 8086 and Pin Description of 8086V'nod Rathode BPas encore d'évaluation

- Unit III 8086 Microprocessor InterfacingDocument26 pagesUnit III 8086 Microprocessor InterfacingRammanohar Lokiya100% (1)

- Unit 2Document55 pagesUnit 2Shubhankit SinghPas encore d'évaluation

- ECE 2211 Microprocessor and Interfacing: The 8088/8086 Microprocessors and Their Memory and I/O InterfacesDocument37 pagesECE 2211 Microprocessor and Interfacing: The 8088/8086 Microprocessors and Their Memory and I/O InterfacesZahid Ali ArainPas encore d'évaluation

- Unit 2 16 Bit Microprocessors 8086/8088Document33 pagesUnit 2 16 Bit Microprocessors 8086/8088Asha GusainPas encore d'évaluation

- Pin Diagram of 8086 MicroprocessorDocument14 pagesPin Diagram of 8086 Microprocessorkranthi6190Pas encore d'évaluation

- ECE 2211 Microprocessor and Interfacing: The 8088/8086 Microprocessors and Their Memory and I/O InterfacesDocument37 pagesECE 2211 Microprocessor and Interfacing: The 8088/8086 Microprocessors and Their Memory and I/O InterfacesSrikanth PrasadPas encore d'évaluation

- CT1 SolDocument16 pagesCT1 Soln200vermaPas encore d'évaluation

- 8086 Section 3-4Document4 pages8086 Section 3-4Jaspreet KaurPas encore d'évaluation

- TrackerDocument93 pagesTrackerashutosh kumarPas encore d'évaluation

- 6 +8284+Clock+GeneratorDocument4 pages6 +8284+Clock+GeneratorJayashreedas1990Pas encore d'évaluation

- 8086 Min Max Mode Operations ModifiedDocument78 pages8086 Min Max Mode Operations ModifiedRitu RathiPas encore d'évaluation

- Operating Modes of 8086 MicroprocessorDocument9 pagesOperating Modes of 8086 MicroprocessorMOHAMMED ASLAM CPas encore d'évaluation

- 8086 FullDocument72 pages8086 FullNandhini Nachiyar100% (4)

- Pinouts of 8086Document12 pagesPinouts of 8086Infinity Star GamingPas encore d'évaluation

- Mic Unit1Document21 pagesMic Unit1xboyxman1000Pas encore d'évaluation

- 8086 Based SystemDocument20 pages8086 Based SystemAakash GargPas encore d'évaluation

- 8086 Microprocessor Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Document40 pages8086 Microprocessor Interfacing: Dr.P.Yogesh, Senior Lecturer, DCSE, CEG Campus, Anna University, Chennai-25Janu100% (2)

- 8086 - Pin Diagram, Minimum Mode and Maximum ModeDocument43 pages8086 - Pin Diagram, Minimum Mode and Maximum Modevivek kilaparthiPas encore d'évaluation

- Mp&i Course File - unit-IIIDocument23 pagesMp&i Course File - unit-IIIvenkateshrachaPas encore d'évaluation

- Chapter 4 PPTDocument24 pagesChapter 4 PPTMengistu BirukePas encore d'évaluation

- PPT-3 8088 8086 PinDocument53 pagesPPT-3 8088 8086 PinMadhav Singh100% (1)

- 2-16 Bit Microprocessor 8086Document20 pages2-16 Bit Microprocessor 8086afzal_a75% (4)

- 8086 System Bus StructureDocument19 pages8086 System Bus StructureArman IslamPas encore d'évaluation

- Principles of Purchasing Nd1 Bam 117Document36 pagesPrinciples of Purchasing Nd1 Bam 117Alexander GabrielPas encore d'évaluation

- BSP Pipe ThreadDocument1 pageBSP Pipe ThreadgvmindiaPas encore d'évaluation

- CT Scanner Asteion Super 4 PDFDocument16 pagesCT Scanner Asteion Super 4 PDFYusef ManasrahPas encore d'évaluation

- AsfasdDocument61 pagesAsfasdsakfjsafkljsahdkljfhPas encore d'évaluation

- Itime FAQDocument20 pagesItime FAQadadaed adPas encore d'évaluation

- Workshop Solution For Bulk ProcessingDocument20 pagesWorkshop Solution For Bulk Processingmuruganandhan100% (2)

- Wafer 5825&6Document1 pageWafer 5825&6RB STPas encore d'évaluation

- Rm0421 Spc58xnx 32bit Power Architecture Microcontroller For Automotive Asild Applications StmicroelectronicsDocument4 101 pagesRm0421 Spc58xnx 32bit Power Architecture Microcontroller For Automotive Asild Applications StmicroelectronicsAlan TorreblancaPas encore d'évaluation

- Convert Sign Language To SpeechDocument29 pagesConvert Sign Language To SpeechBon DokPas encore d'évaluation

- OS-390 Project REC2Document2 pagesOS-390 Project REC2Justin OlinPas encore d'évaluation

- Isopropil MiristatDocument1 pageIsopropil MiristatnofaPas encore d'évaluation

- Algebra Questions For SSC CGL Set-3 PDFDocument7 pagesAlgebra Questions For SSC CGL Set-3 PDFRatnesh kumar DattaPas encore d'évaluation

- Unix FundamentalsDocument47 pagesUnix Fundamentalsdjay sharmaPas encore d'évaluation

- Јohn Lakos - Large-Scale C++ Volume I - Process and Architecture (2020, Pearson)Document1 023 pagesЈohn Lakos - Large-Scale C++ Volume I - Process and Architecture (2020, Pearson)asdasd asdasdPas encore d'évaluation

- NIELIT Recruitment For Scientist and Technical Assistants 2017 Official NotificationDocument6 pagesNIELIT Recruitment For Scientist and Technical Assistants 2017 Official NotificationKshitija100% (1)

- SiC EpitaxyDocument48 pagesSiC EpitaxyRamakrishnan RamPas encore d'évaluation

- Coursera KTLNF9NLR4CS PDFDocument1 pageCoursera KTLNF9NLR4CS PDFVictor JimenezPas encore d'évaluation

- AG-HMR10P AG-HMR10E: Operating InstructionsDocument106 pagesAG-HMR10P AG-HMR10E: Operating InstructionsbearjapanPas encore d'évaluation

- DR - Sri.Sri - Sri.Shivakumara Mahaswamy College of Engineering Department of Civil Engineering I InternalDocument2 pagesDR - Sri.Sri - Sri.Shivakumara Mahaswamy College of Engineering Department of Civil Engineering I InternalCivil EngineeringPas encore d'évaluation

- Managed IT Services RFP TemplateDocument11 pagesManaged IT Services RFP Templateedpaala67% (3)

- USER MANUAL iFMSDocument85 pagesUSER MANUAL iFMSVenu KumarPas encore d'évaluation

- Ma 0702 05 en 00 - Setup ManualDocument214 pagesMa 0702 05 en 00 - Setup ManualRoronoa ZorroPas encore d'évaluation

- STAENZ Academy Prospectus CDMP Small PDFDocument31 pagesSTAENZ Academy Prospectus CDMP Small PDFSheka PatraPas encore d'évaluation

- Multicalor 700.1 MD Multicalor 800.1 MD Multicalor 1000.1 MD Multicalor 1200.1 MDDocument24 pagesMulticalor 700.1 MD Multicalor 800.1 MD Multicalor 1000.1 MD Multicalor 1200.1 MDcristian villegasPas encore d'évaluation

- Oracle Process ExecutionDocument552 pagesOracle Process ExecutionVineethPas encore d'évaluation

- C+source Code On +scienific CalculatorDocument22 pagesC+source Code On +scienific CalculatorBittu76% (29)

- KDDDocument2 pagesKDDnagendraoraappsPas encore d'évaluation

- TEC - OPS - Supra MT - 750-1250 - 62-61921-20 - Rev - ENGDocument501 pagesTEC - OPS - Supra MT - 750-1250 - 62-61921-20 - Rev - ENGJennyJudithRuizSanchez100% (1)

- Scrip Cuota UsadaDocument1 pageScrip Cuota Usadahelgo56Pas encore d'évaluation

- Payment Information: Spark Mastercard Business Worldelite Account Ending in 2103Document11 pagesPayment Information: Spark Mastercard Business Worldelite Account Ending in 2103Lucy Marie RamirezPas encore d'évaluation