Académique Documents

Professionnel Documents

Culture Documents

Décodage Adresse1 Prof

Transféré par

BlaugranaCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Décodage Adresse1 Prof

Transféré par

BlaugranaDroits d'auteur :

Formats disponibles

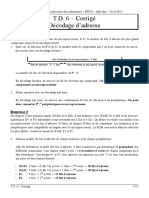

TD : DECODAGE DADRESSES

DECODAGE DADRESSES: TD n1

Objectif : Au cours de ce TD, nous allons voir les notions fondamentales concernant le

dcodage dadresses:

- Quel est le but du dcodage dadresse.

- Comment est-il implment dans une architecture microprocesseur.

- Comment tablir un plan mmoire dun systme microprocesseur existant.

I. PRESENTATION DU SYSTEME

On considre un systme base dun microprocesseur comprenant les divers lments

suivants :

- Un microprocesseur 8 bits ;

- Une mmoire ROM ;

- Une mmoire RAM ;

- Un Convertisseur Analogique Numrique (CAN) permettant de convertir

plusieurs tensions analogiques.

Le schma simplifi du systme est le suivant :

D[0..7]

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

ROM

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

RAM

D0

D1

D2

D3

D4

D5

D6

D7

CS

CS

A[0..9]

A8

A9

A10

A11

A12

CS_RAM

DECODAGE

DADRESSES

CS_ROM

Entres des

tensions

analogiques

S0

S1

V1

V2

V3

V4

CAN

CS_CAN

D0

D1

D2

D3

D4

D5

D6

D7

CS

LYCEE LA FAYETTE

1/7

TD : DECODAGE DADRESSES

II. VOCABULAIRE ET DEFINITION

Question II.1. Calculer la capacit de la mmoire RAM en octets et en kbits.

Capacit = 29 octets = 512 octets = 4 kbits

Question II.2. Calculer la capacit de la mmoire ROM en ko et en kbits.

Capacit = 210 octets = 1024 octets = 1 ko = 8 kbits

Question II.3. Comment se nome le bus D[0..7] ?

Cest le bus de donnes : Cest sur ce bus que sont prsentes les donnes lues sur les

divers circuits du systme.

Question II.4. Comment se nome le bus A[0..7] ?

Cest le bus dadresses : Cest sur ce bus que sont prsentes les adresses permettant

dadresser les divers circuits du systme.

Question II.5. Que signifie le terme

CS

? Sur quel tat logique cette entre est-elle valide ?

CS = Chip Select. Il permet la slection du botier. Cette entre est valide sur un tat

logique bas.

Question II.6. Cocher la bonne rponse : Lorsque le signal CS de la RAM et de la ROM est

ltat logique 1 .

Les sorties de la RAM et de la ROM sont 1 ou 0 suivant les

valeurs contenues dans les mmoires

Les sorties du circuit intgr sont en haute impdance HZ

Question II.7. Cocher la bonne rponse : Dans le cas o les signaux CS de la RAM et de la

ROM sont ltat bas en mme temps

Il ny a pas de conflit sur le bus de donnes

Il y a un conflit car les signaux D0 D7 de ces deux composants sont

prsents sur le bus de donnes.

LYCEE LA FAYETTE

2/7

TD : DECODAGE DADRESSES

Question II.8. Si on veut lire les donnes de la RAM, quels circuits doit-on dsactiver afin

dviter un conflit sur le bus de donnes ?

Il faut dsactiver la ROM et le CAN.

Question II.9. Si on veut lire les donnes de la ROM, quels circuits doit-on dsactiver afin

dviter un conflit sur le bus de donnes ?

Il faut dsactiver la RAM et le CAN.

Question II.10. Si on veut lire les donnes du CAN, quels circuits doit-on dsactiver afin

dviter un conflit sur le bus de donnes ?

Il faut dsactiver la RAM et la ROM.

Question II.11. Expliquer succinctement le rle du dcodage dadresses dans un tel systme.

Le dcodage dadresses permet de slectionner un seul circuit parmi tous ceux prsents

dans le systme. Cela permet de mettre les sorties des circuits non utiliss lors de

ladressage en haute impdance. Ainsi il ny a pas de conflits.

III. FONCTIONNEMENT DU CAN

Le CAN utilis dans ce systme permet de convertir jusqu 4 tensions analogiques. Les

tensions analogiques convertir sont slectionne laide des broches S0 et S1.

La table suivante indique comment sont slectionnes les tensions analogiques lentre du

CAN :

S1

0

0

1

1

S0

0

1

0

1

Tension analogique slectionne

V1

V2

V3

V4

Question III.1. Complter le tableau suivant :

A9

0

0

1

1

A8

0

1

0

1

LYCEE LA FAYETTE

Tensions analogique slectionne

V1

V2

V3

V4

3/7

TD : DECODAGE DADRESSES

IV. ETABLISSEMENT DU PLAN MEMOIRE DU SYSTEME

Afin de raliser la fonction dcodage dadresses, on utilise un circuit 74138. Le schma du

systme est le suivant :

D[0..7]

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

D0

D1

D2

D3

D4

D5

D6

D7

ROM

A0

A1

A2

A3

A4

A5

A6

A7

A8

RAM

D0

D1

D2

D3

D4

D5

D6

D7

CS

CS

A[0..9]

A8

A9

CS_ROM

BIN/OCT

A10

A11

A12

Entres des

tensions

analogiques

&

EN

15

14

13

12

11

10

9

7

0

1

2

3

4

5

6

7

CS_RAM

CS_CAN

S0

S1

V1

V2

V3

V4

CAN

D0

D1

D2

D3

D4

D5

D6

D7

CS

5

74LS138

DECODAGE

DADRESSES

La table de vrit du circuit 74138 est la suivante :

4

0

0

0

0

1

1

1

1

Entres

2

0

0

1

1

0

0

1

1

LYCEE LA FAYETTE

Sorties

1

0

1

0

1

0

1

0

1

0

0

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

2

1

1

0

1

1

1

1

1

3

1

1

1

0

1

1

1

1

4

1

1

1

1

0

1

1

1

5

1

1

1

1

1

0

1

1

6

1

1

1

1

1

1

0

1

7

1

1

1

1

1

1

1

0

4/7

TD : DECODAGE DADRESSES

Question IV.1. Complter le schma structurel de la page prcdente en reliant correctement

les broches 6, 4 et 5 (chacune au VCC ou la masse) du 74138 afin de le valider.

Question IV.2. En vous aidant de la table de vrit du 74138, complter le tableau suivant :

Adresses A[10..12]

A12

A11

A10

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

0

0

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

2

1

1

0

1

1

1

1

1

Sorties du 74138

3

4

1

1

1

1

1

1

0

1

1

0

1

1

1

1

1

1

5

1

1

1

1

1

0

1

1

6

1

1

1

1

1

1

0

1

7

1

1

1

1

1

1

1

0

Question IV.3. Quel doit tre le niveau du signal CS_RAM pour slectionner la RAM ?

Il faut CS_RAM = 0

Question IV.4. Quels doivent tre les niveaux logiques sur A10, A11 et A12 afin de

slectionner la RAM ?

Il faut A10=0 ; A11=0 et A12=0

Question IV.5. Quel doit tre le niveau du signal CS_ROM pour slectionner la ROM ?

Il faut CS_ROM = 0

Question IV.6. Quels doivent tre les niveaux logiques sur A10, A11 et A12 afin de

slectionner la ROM ?

Il faut A10 = 1 ; A11 = 0 ; A12 = 0

Question IV.7. Quel doit tre le niveau du signal CS_CAN pour slectionner le CAN ?

Il faut CS_CAN = 0.

Question IV.8. Quels doivent tre les niveaux logiques sur A10, A11 et A12 afin de

slectionner le CAN ?

Il faut A10 = 0 ; A11 = 1 et A12 = 0

LYCEE LA FAYETTE

5/7

TD : DECODAGE DADRESSES

On rappel que le CAN permet de faire lacquisition de 4 tensions analogiques. Les tensions

analogiques sont slectionnes laide des adresses A8 et A9.

Question IV.9. Complter le tableau suivant dcrivant les adresses hautes et basses

permettant de slectionner les circuits RAM, ROM et CAN.

Circuit

RAM

ROM

CAN : V1

CAN : V2

CAN : V3

CAN : V4

A12

0

0

0

0

0

0

0

0

0

0

0

0

A11

0

0

0

0

1

1

1

1

1

1

1

1

A10

0

0

1

1

0

0

0

0

0

0

0

0

A9

1

0

1

0

0

0

0

0

1

1

1

1

A8

1

0

1

0

0

0

1

1

0

0

1

1

A7

1

0

1

0

1

0

1

0

1

0

1

0

A6

1

0

1

0

1

0

1

0

1

0

1

0

A5

1

0

1

0

1

0

1

0

1

0

1

0

A4

1

0

1

0

1

0

1

0

1

0

1

0

A3

1

0

1

0

1

0

1

0

1

0

1

0

A2

1

0

1

0

1

0

1

0

1

0

1

0

A1

1

0

1

0

1

0

1

0

1

0

1

0

A0

1

0

1

0

1

0

1

0

1

0

1

0

Question IV.10. Dduire de la question prcdente les plages dadresses permettant la

slection des diffrents circuits :

Circuit

RAM

ROM

CAN

V1

V2

V3

V4

Plage dadresses (en hexadcimal)

0000 03FF

0400 07FF

0800 08FF

0900 09FF

0A00 0AFF

0B00 0BFF

Question IV.11. Combien de ko la plage dadresses de la ROM permet-elle dadresser ?

0400 07FF = 1024 octets = 1 ko

Question IV.12. Combien de ko la plage dadresses de la RAM permet-elle dadresser ?

0000 03FF = 1024 octets = 1 ko

Question IV.13. En comparant la capacit de la RAM avec le nombre de ko qui peuvent tre

adresss sur la RAM, donner la plage dadresses inutilise dans le systme pour la RAM.

Adresses inutilises par la RAM : 0200 03FF soit 512 octets.

LYCEE LA FAYETTE

6/7

TD : DECODAGE DADRESSES

Question IV.14. Lors du dveloppement dun programme permettant dadresser les

diffrentes entres analogiques du CAN, quelles adresses choisirez-vous pour adresser les

entres V1, V2, V3 et V4 ?

V1 : 0800

V2 : 0900

V3 : 0A00

V4 : 0B00

Question IV.11. Complter le plan mmoire ci-dessous en utilisant les adresses que vous avez

rserves pour les diffrentes entres du CAN.

0B00h

0AFFh

CAN : V4

0900h

08FFh

CAN : V2

CAN : V3

CAN : V1

0BFFh

0A00h

09FFh

0800h

07FFh

ROM

VIDE

0400h

03FFh

0200h

01FFh

RAM

0000h

LYCEE LA FAYETTE

7/7

Vous aimerez peut-être aussi

- Architecture Du Microprocesseur 6809 de MotorolaDocument14 pagesArchitecture Du Microprocesseur 6809 de MotorolaPhylipe Rodrigez100% (1)

- Adressage MemoireDocument10 pagesAdressage MemoireLibre HamataPas encore d'évaluation

- Conversion Analogique NumériqueDocument9 pagesConversion Analogique NumériqueOmar Fouaz Taleb BahmedPas encore d'évaluation

- Introduction Aux MC STM32 PDFDocument9 pagesIntroduction Aux MC STM32 PDFZied HouanebPas encore d'évaluation

- TD Exam PDFDocument12 pagesTD Exam PDFpapPas encore d'évaluation

- Calcul Capacite MemoiresDocument25 pagesCalcul Capacite MemoiresAbdelmoumenAbdelmoumenPas encore d'évaluation

- Chapitre 9 Les Timers en MikrocDocument14 pagesChapitre 9 Les Timers en MikrocRadwane LourhmatiPas encore d'évaluation

- TD Decodage AdressesDocument10 pagesTD Decodage AdressesDhafer MezghaniPas encore d'évaluation

- TD 06 CorrigeDocument12 pagesTD 06 CorrigeOmar KhayyamPas encore d'évaluation

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- IjDocument7 pagesIjAbderrahmane WardiPas encore d'évaluation

- Un - Syst - Me - Microprocesseur - PDF Filename - UTF-8''Un Système À MicroprocesseurDocument11 pagesUn - Syst - Me - Microprocesseur - PDF Filename - UTF-8''Un Système À MicroprocesseurLynda MOKRANIPas encore d'évaluation

- M - Microprocesseurs Et DSP-Chap2Document17 pagesM - Microprocesseurs Et DSP-Chap2MENANI ZineddinePas encore d'évaluation

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- 1 Architecture de 8255Document10 pages1 Architecture de 8255Yogbake HansPas encore d'évaluation

- TP3: Conception Schématique Des Microprocesseurs: ObjectifDocument6 pagesTP3: Conception Schématique Des Microprocesseurs: ObjectifDor SafPas encore d'évaluation

- CorrigéExamen 2020-2021Document3 pagesCorrigéExamen 2020-2021Moujahed GassoumiPas encore d'évaluation

- TP Moto 6809Document7 pagesTP Moto 6809gamerzxs681Pas encore d'évaluation

- 68 HC 11Document15 pages68 HC 11Abdelhadi TaoufikPas encore d'évaluation

- Série 5Document3 pagesSérie 5Blidi AymenPas encore d'évaluation

- Mise en Route Du Compilateur MPLAB XC8Document11 pagesMise en Route Du Compilateur MPLAB XC8nawzatPas encore d'évaluation

- Guide Moto6809Document23 pagesGuide Moto6809fatima zahra benmeriemePas encore d'évaluation

- 04 Microprocesseur 8086Document18 pages04 Microprocesseur 8086nesrine ninaPas encore d'évaluation

- Exercice 0:: Tp1: Architecture Des MicrocontroleursDocument3 pagesExercice 0:: Tp1: Architecture Des MicrocontroleursأمينPas encore d'évaluation

- Cours APM 02 PDFDocument13 pagesCours APM 02 PDFLeroy Lionel SonfackPas encore d'évaluation

- Ser TD4 20222023Document4 pagesSer TD4 20222023ramzi ayadi100% (1)

- Port Parallèle Pia 8255Document11 pagesPort Parallèle Pia 8255alex bbapPas encore d'évaluation

- Chapitre 4 Alimentation - Moteur - Pas - À - PasDocument37 pagesChapitre 4 Alimentation - Moteur - Pas - À - Paskhaled100% (1)

- tp1 - Comninatoire - IsisDocument10 pagestp1 - Comninatoire - IsisRiham Glif100% (1)

- Temporisation - Les Variables en AssembleurDocument16 pagesTemporisation - Les Variables en AssembleurMolka ABIDPas encore d'évaluation

- E X Memoire2Document3 pagesE X Memoire2حميد خلفاوي100% (1)

- TD 1 Les Mémoires: 1. Partie ThéoriqueDocument2 pagesTD 1 Les Mémoires: 1. Partie ThéoriqueAla DorbozPas encore d'évaluation

- Assembleur x86Document96 pagesAssembleur x86Ibtihel MechleouiPas encore d'évaluation

- TD#3Document2 pagesTD#3Marouane TaibiniPas encore d'évaluation

- TD N 2Document4 pagesTD N 2Cesar Malki100% (1)

- Exo Ensl CoDocument14 pagesExo Ensl CoAnonymous DZg1vCRdj50% (2)

- Correction Du td1 ArmDocument2 pagesCorrection Du td1 Armazza memmi100% (1)

- Corrtd 1Document7 pagesCorrtd 1wafa wafaPas encore d'évaluation

- TD1 19corrDocument5 pagesTD1 19corrSaid ReganiPas encore d'évaluation

- Corrigé TD 154Document3 pagesCorrigé TD 154MBADJOUN Daniel100% (1)

- tp3 Ing 2015 PDFDocument7 pagestp3 Ing 2015 PDFDorian GreyPas encore d'évaluation

- TD 2Document5 pagesTD 2csm schoolPas encore d'évaluation

- TD N 4 (Supplemetaire) FpgaDocument2 pagesTD N 4 (Supplemetaire) FpgaLE BARONPas encore d'évaluation

- C - Memoire Corrigés - CopieDocument5 pagesC - Memoire Corrigés - CopieBrady C'est DieuPas encore d'évaluation

- Chapitre 5-HW SW CodesignDocument52 pagesChapitre 5-HW SW Codesignhelakaraa0% (3)

- TD Assembleur Lp2 Mirtax86Document8 pagesTD Assembleur Lp2 Mirtax86Oumar Farouk Achirou ElhadjiPas encore d'évaluation

- Examen Rattrapage Architectures Avancées Sur SoC 2019Document6 pagesExamen Rattrapage Architectures Avancées Sur SoC 2019Dhafer MezghaniPas encore d'évaluation

- Les MemoiresDocument45 pagesLes MemoiresWalter FopaPas encore d'évaluation

- Enonce Du TP 2 MicroP Microprocesseurs TP 03 03 10Document3 pagesEnonce Du TP 2 MicroP Microprocesseurs TP 03 03 10abderrazzak2011Pas encore d'évaluation

- 05 Les Interfaces E-S Du 8086Document9 pages05 Les Interfaces E-S Du 8086MENANI ZineddinePas encore d'évaluation

- Exercices Architecture Des Processeurs Et MicroprocesseursDocument4 pagesExercices Architecture Des Processeurs Et MicroprocesseursGeorges Le Mignon Ole100% (1)

- ch7 Memoires PDFDocument9 pagesch7 Memoires PDFYoucef Br'sPas encore d'évaluation

- Exercices Assembleur M1 ELT ER Serie 2 Avec CorrigéDocument5 pagesExercices Assembleur M1 ELT ER Serie 2 Avec CorrigéAmir Na DzPas encore d'évaluation

- Cours Electronique Numérique PDFDocument12 pagesCours Electronique Numérique PDFImad EdinePas encore d'évaluation

- Exercice 21 - 22 - 23Document8 pagesExercice 21 - 22 - 23Riham abPas encore d'évaluation

- Série 01 PDFDocument4 pagesSérie 01 PDFÃčĥ ŖăfPas encore d'évaluation

- Interfaçage Du Microprocesseur 8086Document29 pagesInterfaçage Du Microprocesseur 8086Abderrazzak Riali50% (2)

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- Wa0000.Document2 pagesWa0000.Paréto BessanhPas encore d'évaluation