Académique Documents

Professionnel Documents

Culture Documents

TD - Série #3: Exercice 1: Nombre Signés

Transféré par

Our Tv0 évaluation0% ont trouvé ce document utile (0 vote)

17 vues1 pageTitre original

TD3

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

17 vues1 pageTD - Série #3: Exercice 1: Nombre Signés

Transféré par

Our TvDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 1

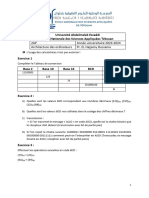

Année universitaire : 2023 - 2024

Module : Architecture des ordinateurs et assembleur

Pr. Safae Berrichi

TD - Série N° 3

Exercice 1 : Nombre signés

1. Coder sur 4 bits les valeurs suivantes : 7, 2, -7 et −2 avec les représentations : SVA, CA1 et

CA2.

2. Coder −15 en complément à 2 sur 1 octet.

3. Décoder cette valeur binaire 10100010 représentée en complément à 2.

4. Coder les entiers 18 et −18 sur un octet en utilisant la représentation par le signe et la valeur

absolue. Montrer que l’addition binaire de ces entiers ainsi codés produit un résultat incorrect.

Montrer qu’en revanche le résultat est correct si ces entiers sont codés en utilisant la représentation

par le complément à 2.

Exercice 2 : Calculs arithmétiques

1. Effectuer sur 8 bits les opérations suivantes en binaire. Préciser, pour chaque opération, la retenue et

le débordement. :

a. 53 + 72

b. 78 – 23

c. 51 + 127

d. −3 − 127

2. Effectuer les opérations suivantes en héxadécimal:

a. (56 + 2C)16

b. (56-2C)16

3. Effectuer la multiplication de chacune des opérations suivantes :

a. 1101 et 110

b. 1111 et 101

c. 10110 et 11

4. Donner le reste et le quotient de chacune des opérations suivantes :

a. 1100000 / 110

b. 111111 / 11

c. 1110100 / 101

Exercice 3 : Nombres réels

a. Coder sur 8 bits en binaire les parties fractionnaires suivantes : 24,625

1. Décoder les nombres suivants : 0,10110000 et 110.11011001

2. Effectuer la somme des deux nombres (100,10)2, et (1,1010)2

3. Convertir le nombre décimal 8,625 en virgule flottante suivant la norme IEEE 754

4. Soient les 2 nombres codés suivant la norme IEEE 754 et représentés en hexadécimal :

3EE00000 et 3D800000. Donner le résultat sous forme IEEE 754 et sous forme décimale.

1|1Pages

Vous aimerez peut-être aussi

- TD 1 - Représentation Des Nombres en MachineDocument3 pagesTD 1 - Représentation Des Nombres en Machinejamouci50% (2)

- Exercises - TD1 DSPDocument2 pagesExercises - TD1 DSPINTTICPas encore d'évaluation

- TD 1.systémes de Numération - BéjaiaDocument2 pagesTD 1.systémes de Numération - Béjaiabig0% (1)

- TD 1Document4 pagesTD 1Khalil SelmiPas encore d'évaluation

- TD 1Document3 pagesTD 1mahmoud01 ayachiPas encore d'évaluation

- Structure MachineDocument2 pagesStructure MachineYoussouf KadiPas encore d'évaluation

- Serie CodageDocument2 pagesSerie CodageFati Ezzaki100% (2)

- Série 1 Codage BinaireDocument2 pagesSérie 1 Codage Binaireham douaaPas encore d'évaluation

- Série 1 Systèmes Logiques 09-11-2020Document1 pageSérie 1 Systèmes Logiques 09-11-2020mimouPas encore d'évaluation

- Enoncé & Corrigé - Série N°1 - SysLogique - 08-02-2020Document8 pagesEnoncé & Corrigé - Série N°1 - SysLogique - 08-02-2020kouame narcisse kouakou100% (1)

- EnregistrementDocument2 pagesEnregistrementOumar SeyePas encore d'évaluation

- TD2 PDFDocument2 pagesTD2 PDFYoussef ZghariPas encore d'évaluation

- Info1 TD 10-MinDocument2 pagesInfo1 TD 10-MinzakiPas encore d'évaluation

- TD1 - Architecture Des Ordi-1Document4 pagesTD1 - Architecture Des Ordi-1Moussango Edimo GeorgesPas encore d'évaluation

- Dut Gp1 Travaux Dirigés TD #2 Informatique IndustrielleDocument2 pagesDut Gp1 Travaux Dirigés TD #2 Informatique IndustrielleMalak ElguessPas encore d'évaluation

- TD ElectroniqueDocument72 pagesTD ElectroniquedanielkefonPas encore d'évaluation

- TD1 - Gi & IdsdDocument2 pagesTD1 - Gi & IdsdIkram ElaimaPas encore d'évaluation

- td1 Elect Num2020 Smi3 2020 PDFDocument2 pagestd1 Elect Num2020 Smi3 2020 PDFmouad friginiPas encore d'évaluation

- Série 1Document2 pagesSérie 1Khalid ElaPas encore d'évaluation

- 2015 08 21 TD2 Representationinformation 0708S1Document4 pages2015 08 21 TD2 Representationinformation 0708S1Mēđ GouigaPas encore d'évaluation

- TD Systèmes Logiques-ConvertiDocument69 pagesTD Systèmes Logiques-ConvertijemaiPas encore d'évaluation

- Exercice MathématiqueDocument8 pagesExercice MathématiqueNabila TouisiPas encore d'évaluation

- Exercice 1Document2 pagesExercice 1Lavie SensPas encore d'évaluation

- TD N°2 InfDocument2 pagesTD N°2 Infstephaniemakeu7Pas encore d'évaluation

- TD - Eléctronique Numérique Avec-CorrectionDocument45 pagesTD - Eléctronique Numérique Avec-CorrectionLenise MorenoPas encore d'évaluation

- TD 1Document2 pagesTD 1Sãb ÎnePas encore d'évaluation

- SERIE1Document4 pagesSERIE1osome1680Pas encore d'évaluation

- TD2Document1 pageTD2adil.benyousseffPas encore d'évaluation

- TD 1 PDFDocument2 pagesTD 1 PDFYoussef ZghariPas encore d'évaluation

- Td1 Electronic-Num Elhanaoui FSTEDocument2 pagesTd1 Electronic-Num Elhanaoui FSTEtariqPas encore d'évaluation

- TD Systèmes LogiquesDocument68 pagesTD Systèmes LogiquesRaf elaz100% (1)

- Poly TD SMDocument4 pagesPoly TD SMDah Mañůs100% (1)

- Série1 Des Travaux DirigésDocument2 pagesSérie1 Des Travaux Dirigéschihab meggPas encore d'évaluation

- TD3 Architecture Des Ordinateurs 2023-2024Document3 pagesTD3 Architecture Des Ordinateurs 2023-2024amiricanbooyPas encore d'évaluation

- Département de Physique Smi / S3 Electronique Numérique TD #1Document1 pageDépartement de Physique Smi / S3 Electronique Numérique TD #1SAHTA OMARPas encore d'évaluation

- TD1 Numérisation Et CodageDocument1 pageTD1 Numérisation Et CodageSoulaima BouhlelPas encore d'évaluation

- numerique SerieDocument2 pagesnumerique SerieBilal EL MANSSOURIPas encore d'évaluation

- 2020TD1 8086Document1 page2020TD1 8086Lakhdar BekkariPas encore d'évaluation

- 1ere Année Classe Préparatoire CP1Document7 pages1ere Année Classe Préparatoire CP1BENDOUDA DjamilaPas encore d'évaluation

- Travaux Dirigés N°1: Systèmes de NumérationDocument4 pagesTravaux Dirigés N°1: Systèmes de NumérationSlim Guessoum100% (2)

- TP2 Representation Des Donnees CorrigeDocument5 pagesTP2 Representation Des Donnees CorrigeAnonymous JIjLxKYApNPas encore d'évaluation

- Cri td1Document2 pagesCri td1Douceur D'étéPas encore d'évaluation

- Série 1Document1 pageSérie 1النوري أيمن - NOURI AYMENPas encore d'évaluation

- Exer Fiche 1 Rep Nombres CorrectionDocument4 pagesExer Fiche 1 Rep Nombres CorrectionMame diarra NdackPas encore d'évaluation

- TD Architecture Ordinateur 2023 2024 EtudiantsDocument5 pagesTD Architecture Ordinateur 2023 2024 Etudiantswww.doukoureabdoulaye1100% (1)

- Exerccies Maths AppliquéesDocument5 pagesExerccies Maths AppliquéesOuss AmaPas encore d'évaluation

- TDs EletroNUm + CorrigéDocument41 pagesTDs EletroNUm + CorrigéGhaffari WalidPas encore d'évaluation

- TD1 Représentation de Linformation1Document3 pagesTD1 Représentation de Linformation1Essia AmriPas encore d'évaluation

- Examen PDFDocument6 pagesExamen PDFWissal BelaouidelPas encore d'évaluation

- Info1 TD 3Document6 pagesInfo1 TD 3zakiPas encore d'évaluation

- Codage CorrectionDocument6 pagesCodage CorrectionUsman AhmedPas encore d'évaluation

- TD Représentation InformationDocument4 pagesTD Représentation InformationKamer Love100% (2)

- Initiation À L'architecture Des Ordinateurs Travaux Dirigés N°2 Représentation Des DonnéesDocument5 pagesInitiation À L'architecture Des Ordinateurs Travaux Dirigés N°2 Représentation Des DonnéesEl Amrani LailaPas encore d'évaluation

- TD1 Electronique NumériqueDocument1 pageTD1 Electronique NumériqueDouaa GhazouaniPas encore d'évaluation

- TD N1 m1Document12 pagesTD N1 m1Ibrahim FerouliPas encore d'évaluation

- TD2Document3 pagesTD2Laeticia KacimiPas encore d'évaluation

- TD Systemes Logiques Circuits CombinatoiresDocument68 pagesTD Systemes Logiques Circuits CombinatoiresChouaib OujhainPas encore d'évaluation

- Serie de TD N01Document2 pagesSerie de TD N01lotfi bouchefiratPas encore d'évaluation