Académique Documents

Professionnel Documents

Culture Documents

SujetStageMaster2Guerin 201112

SujetStageMaster2Guerin 201112

Transféré par

Ģârgâr Said0 évaluation0% ont trouvé ce document utile (0 vote)

8 vues2 pagesTitre original

SujetStageMaster2Guerin_201112

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

8 vues2 pagesSujetStageMaster2Guerin 201112

SujetStageMaster2Guerin 201112

Transféré par

Ģârgâr SaidDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

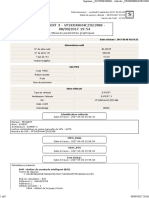

L a b o r a t o i r e d ’ I n t é g r a t i o n d e s S ys t è m e s e t d e s T e c h n o l o g i e s

Département Architecture, Conception et Logiciels Embarqués

Sujet de stage de fin d’étude Ingénieur / Master M2 (bac+5)

Titre : Evaluation de la sûreté de fonctionnement d’un système embarqué multiprocesseur sur

puce

Résumé : Le stage proposé s'inscrit dans le domaine de la fiabilisation des systèmes

multiprocesseurs sur puce pour l'embarqué. Les circuits intégrés fabriqués en technologie

classique, ex. CMOS 32nm, sont sujets à des phénomènes de variation et de dégradation. Cet

état de fait se traduit par le rejet d'un nombre significatif de puces en cours de fabrication qui

subissent des déviations extrêmes, causant ainsi une chute non acceptable du rendement de

fabrication. Le problème se posera également pendant l'utilisation du circuit et affecte sa

fiabilité. Les paramètres électriques subiront des variations dynamiques qui sont causées par la

combinaison de plusieurs phénomènes physiques tels que: le "IR-drop", le "NBTI", les porteurs

chauds, les cycles thermiques, l'"electromigration", etc. Cela résulte en général par l'apparition

d'un retard dans les délais de propagation du circuit puis d'une erreur causant ainsi une panne

du circuit. Habituellement, le problème de la fiabilité des circuits intégrés est traité pendant

l’étape de fabrication. Les lignes de production sont généralement soumises à diverses

procédures de qualification et de réajustement de leurs paramètres de réglage afin d’atteindre

un niveau de fiabilité suffisant (exprimé en général en Failure-In-Time, FIT). En parallèle, des

tests accélérés (coûteux) peuvent être effectués sur différents lots de circuits afin d’éliminer

ceux étant les plus fragiles. La complexité à concevoir des architectures de calcul

multiprocesseurs combinée à la difficulté à maîtriser tous les phénomènes liés aux nouvelles

technologies de fabrication nécessite un changement radical dans l’approche du problème, au

risque de retarder le « time-to-market » ou de réduire le niveau de sûreté de fonctionnement

dans le cas contraire.

Le laboratoire a développé une méthodologie pour l’estimation de la fiabilité d’un tel système.

Elle est implémentée sous la forme d’un simulateur intégré dans le flot de conception. Cela

permet d’évaluer la fiabilité du circuit avec des valeurs réalistes des paramètres électriques du

circuit. L’objectif du stage est de proposer une méthodologie d’évaluation de la sureté de

fonctionnement d’un système embarqué multiprocesseur avec l’aide des outils existants dans le

domaine. La méthodologie doit pouvoir s’inscrire dans celle existante. Il s’agira ainsi de

comprendre tout d’abord les différentes étapes de conception d’un circuit intégré, d’analyser

ensuite la méthodologie actuellement en cours pour l’évaluation de la fiabilité d’un circuit et de

proposer enfin une nouvelle méthode.

Le candidat devra évoluer de manière autonome et faire preuve d'initiatives dans ses choix. Il

travaillera conjointement avec les équipes du CEA LIST et du LASQUO.

Durée : 6 mois

Pré-requis :

Connaissances théoriques sur l’architecture des ordinateurs

Commissariat à l’Energie Atomique

Centre de Saclay – LIST/DACLE - Bâtiment 528 - Point courrier 94 - 91191 Gif sur Yvette Cedex

Tél. : 01.69.08.49.67 – Fax : 01.69.08.83.95 – email : jrlequepeys@cea.fr

Etablissement Public à caractère Industriel et Commercial

R.C.S. PARIS B 775 685 019

Contact : Olivier Héron – olivier.heron@cea.fr

2/2

Vous aimerez peut-être aussi

- Exercices PreactionneursDocument17 pagesExercices PreactionneursLalouli AbderrezzakPas encore d'évaluation

- Presentation SEMS 14 15 PDFDocument20 pagesPresentation SEMS 14 15 PDFMaurice ComlanPas encore d'évaluation

- Exam Janv17 Graphes CorrectionDocument5 pagesExam Janv17 Graphes CorrectionMaurice Comlan100% (1)

- Exam 201306 CorDocument4 pagesExam 201306 CorMaurice ComlanPas encore d'évaluation

- Chapitre 10 - Quelques CitationsDocument4 pagesChapitre 10 - Quelques CitationsMaurice ComlanPas encore d'évaluation

- Aide Mémoire Design PatternDocument21 pagesAide Mémoire Design PatternAymen Bouazizi100% (1)

- Netruning HomebrewDocument13 pagesNetruning HomebrewasturPas encore d'évaluation

- Exe Bache A EauDocument1 pageExe Bache A EauRoubio Mohamed50% (2)

- D16 AFD Tableau de Bord Energie V01Document12 pagesD16 AFD Tableau de Bord Energie V01firas khalfallahPas encore d'évaluation

- Fast Lane - MS-WS-011T00Document3 pagesFast Lane - MS-WS-011T00Etti Roi NoirPas encore d'évaluation

- TP Dim Syst PV1Document5 pagesTP Dim Syst PV1star d'orPas encore d'évaluation

- Présentation Générale de DidapagesDocument6 pagesPrésentation Générale de Didapagesclasses_TICE100% (1)

- APOGEE Prepress 7.0. Didacticiel. Pour Windows Et Macintosh. Version Du Document 7.0.1Document170 pagesAPOGEE Prepress 7.0. Didacticiel. Pour Windows Et Macintosh. Version Du Document 7.0.1francois.toluafePas encore d'évaluation

- Les Avantages de L'informatiqueDocument1 pageLes Avantages de L'informatiqueBenaissa AminaPas encore d'évaluation

- Chapitre 1Document34 pagesChapitre 1Mohamed BouchouichaPas encore d'évaluation

- Operateur/Operatrice Call Center: Qu'est-Ce Que Le Métier "Opérateur (Rice) Call Center" ?Document4 pagesOperateur/Operatrice Call Center: Qu'est-Ce Que Le Métier "Opérateur (Rice) Call Center" ?N'DRI Yao GaelPas encore d'évaluation

- Notice Sepam Serie80 Fonctions FRDocument272 pagesNotice Sepam Serie80 Fonctions FRDerouich2019Pas encore d'évaluation

- Note de CourDocument14 pagesNote de CourAbdelfettah OranPas encore d'évaluation

- A6 SujetDocument1 pageA6 SujetFatima KanounPas encore d'évaluation

- TP TestsAuto RobotFramework TaherDocument3 pagesTP TestsAuto RobotFramework TaherNassim GafsiPas encore d'évaluation

- Détection Et Correction ErreursDocument8 pagesDétection Et Correction ErreursParfumerie Actu'EllePas encore d'évaluation

- Les Protocoles de CommunicationDocument4 pagesLes Protocoles de CommunicationDjelloul Benoudina100% (1)

- Lab4 NoSQLDocument10 pagesLab4 NoSQLKais BarhoumiPas encore d'évaluation

- Catia v5 Machining Brochure FRDocument8 pagesCatia v5 Machining Brochure FRCharradi ZakariaPas encore d'évaluation

- Recommandation Pro Rage Pac Air Eau Habitat Individuel 01conception Reno 2013 12Document89 pagesRecommandation Pro Rage Pac Air Eau Habitat Individuel 01conception Reno 2013 12paulPas encore d'évaluation

- Utilisation Logipicv2Document20 pagesUtilisation Logipicv2alyamor100% (1)

- These Amine Baina 2009 CNRSDocument152 pagesThese Amine Baina 2009 CNRSA videoPas encore d'évaluation

- Instruction Sheet For Electric Locomotive BR 193 Vectron: Funktion / Funzione / Function / FonctionsDocument2 pagesInstruction Sheet For Electric Locomotive BR 193 Vectron: Funktion / Funzione / Function / FonctionsGavril AndrisanPas encore d'évaluation

- Ie3 Norme Cei 60034 30 PDFDocument2 pagesIe3 Norme Cei 60034 30 PDFKDAPas encore d'évaluation

- Commandes de Gestion Des FichiersDocument9 pagesCommandes de Gestion Des FichiersJean Elvis BijinamaPas encore d'évaluation

- BALI Cours GSIT MaintenanceDocument36 pagesBALI Cours GSIT Maintenanceleharani soheibPas encore d'évaluation

- Tepee 3Document8 pagesTepee 3syyPas encore d'évaluation

- La Technologie ModerneDocument2 pagesLa Technologie Modernehicikab639Pas encore d'évaluation

- Le Courant Porteur en LigneDocument4 pagesLe Courant Porteur en LigneFathi SaiPas encore d'évaluation