Académique Documents

Professionnel Documents

Culture Documents

Examen Programmation Parallèle

Transféré par

Business CarCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Examen Programmation Parallèle

Transféré par

Business CarDroits d'auteur :

Formats disponibles

Examen Programmation Parallèle – Durée 2H

Exercice 1

La machine décrite ci-dessus utilise le protocole MESI pour maintenir la cohérence du cache. Dans la

suite, Rp(a) signifie que le processeur p lit un octet de l'adresse a. Wp(a) = v signifie que le processeur

p écrit v à l'emplacement mémoire a. Les adresses sont représentées en binaire. Initialement, toutes

les lignes de cache sont invalides et tous les emplacements mémoire contiennent 0. On peut

remarquer, en lisant les adresses, que toutes les opérations portent sur un même bloc.

a. Montrez les transitions des lignes de cache et la latence dans le tableau ci-dessous, sachant que :

Un cache hit prend 1 cycle,

Un cache miss prend 8 cycles,

Un write back prend 8 cycles,

Une transition I - M prend 2 cycles

Une transition S - M prend 2 cycles.

b. Quelle est la pénalité (latence totale) de cette séquence de code ?

c. Trouvez une meilleure séquence d’exécution qui va engendrer la plus petite pénalité.

Exercice 2

En utilisant une approche basée sur l’espionnage, et le protocole MESI, remplir le tableau ci-dessous.

Sachant que trois processeurs se partagent la variable b. Les caches C1, C2 et C3 sont considérés

comme initialement à l’état Invalide (I). La mémoire est notée Mem.

Action Bus Tr Fournit par C1 C2 C3

P1 PrRd

P3 PrRd

P3 PrWr

P1 PrRd

P2 PrRd

Exercice 3

Soit le programme parallèle ci-dessous avec deux threads Thread1 et Thread2. Les variables A et B

sont initialement à 0 chacune. En considérant qu’un modèle de cohérence séquentielle est utilisé.

a. Donner deux (autres : différents de l’exemple) exécutions possibles pour ce programme ainsi

que la valeur affichée :

Par exemple une exécution possible ainsi que la valeur affichée : (1) → (2) → (3) → (4) : 01

b. Donner une exécution impossible et le résultat correspondant.

Dr. El Hadji Bassirou TOURE – M2 GL ISI

Vous aimerez peut-être aussi

- Exam-Arch 2010Document6 pagesExam-Arch 2010abir cherifPas encore d'évaluation

- DS SEPCcor 14 11 2017-1Document11 pagesDS SEPCcor 14 11 2017-1Dhia BenkhaledPas encore d'évaluation

- TD2 2021-2022Document2 pagesTD2 2021-2022ayoub attiPas encore d'évaluation

- Exercices Chiffrement Et DéchiffrementDocument4 pagesExercices Chiffrement Et DéchiffrementNasandratra SandiPas encore d'évaluation

- TD OrdonnancementDocument4 pagesTD OrdonnancementbenfatahPas encore d'évaluation

- Exe MCDDocument3 pagesExe MCDHaingonirina Ignace33% (3)

- TD1 MCD PDFDocument2 pagesTD1 MCD PDFSanaa JhPas encore d'évaluation

- TD Chiffrement Affine - CorrectionDocument6 pagesTD Chiffrement Affine - CorrectionTo MH100% (1)

- Serie 3 - Principes FondamentauxDocument2 pagesSerie 3 - Principes FondamentauxKhawla mimi100% (1)

- Serie TD MahseurDocument12 pagesSerie TD MahseurSelma RahimPas encore d'évaluation

- TD1 SQL Cor PDFDocument4 pagesTD1 SQL Cor PDFissamPas encore d'évaluation

- DS Corrigé Réseaux 2Document6 pagesDS Corrigé Réseaux 2helakaraaPas encore d'évaluation

- Corrigé Type Interrogation Novembre 2013Document6 pagesCorrigé Type Interrogation Novembre 2013Samir MOUHOUBIPas encore d'évaluation

- TD4 TCPDocument1 pageTD4 TCPSifDinPas encore d'évaluation

- TD AtmDocument2 pagesTD AtmNoblaPas encore d'évaluation

- TD1. Arbre CouvrantDocument2 pagesTD1. Arbre Couvrantsafe selmi100% (1)

- Examen AO Corrig Univ Guelma 2018Document6 pagesExamen AO Corrig Univ Guelma 2018Siaka Dycosh BertePas encore d'évaluation

- CPCG TD1Document2 pagesCPCG TD1Bella SalimaPas encore d'évaluation

- DS RLE 2015 - CorrigéDocument5 pagesDS RLE 2015 - Corrigébaklouti lindaPas encore d'évaluation

- Examen 2Document5 pagesExamen 2Mouhcine RomaniPas encore d'évaluation

- CH 4 - TCP - UDPDocument53 pagesCH 4 - TCP - UDPstecka gigoPas encore d'évaluation

- TD - Réseaux InformatiquesDocument2 pagesTD - Réseaux InformatiquesIsmail ElouargaPas encore d'évaluation

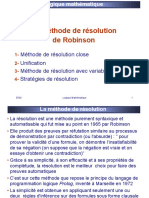

- Principe de Resolution de Robinson-CH4Document71 pagesPrincipe de Resolution de Robinson-CH4youssef ghaouiPas encore d'évaluation

- QCM TP IgpDocument3 pagesQCM TP IgpSOUKHRATIPas encore d'évaluation

- Correction TDDocument7 pagesCorrection TDibouPas encore d'évaluation

- Masterpro Final 2005 CorrectionDocument4 pagesMasterpro Final 2005 CorrectionChayma Ben ZekriPas encore d'évaluation

- Correction Exos de RéseauxDocument4 pagesCorrection Exos de RéseauxluqmanPas encore d'évaluation

- EMD SE 2021 SolutionDocument4 pagesEMD SE 2021 SolutionfatimaPas encore d'évaluation

- Question de Cours Reseaux 2Document4 pagesQuestion de Cours Reseaux 2Eslemhoum MedlPas encore d'évaluation

- Présentation Des Réseaux Locaux Commutés TD - 2Document3 pagesPrésentation Des Réseaux Locaux Commutés TD - 2Mustapha OulcaidPas encore d'évaluation

- 2m ISI Web-AvanceDocument5 pages2m ISI Web-AvanceMohammed SeriariPas encore d'évaluation

- QCM Si 2012 CGP Mpa A v1Document2 pagesQCM Si 2012 CGP Mpa A v1coyote41100% (1)

- TP SGBD SamyaSagarDocument25 pagesTP SGBD SamyaSagarMohamed Aziz MastourPas encore d'évaluation

- TD EthernetDocument5 pagesTD EthernetMohamed Sallami RehoumaPas encore d'évaluation

- Exposé Réseaux de Nouvelle GénérationDocument11 pagesExposé Réseaux de Nouvelle GénérationNaomie MogounPas encore d'évaluation

- 02exercices2 PDFDocument5 pages02exercices2 PDFDadi Mohamed BéchirPas encore d'évaluation

- Chap 7Document21 pagesChap 7Elaasry AbdellahPas encore d'évaluation

- Devoir À RendreDocument2 pagesDevoir À Rendrezakaria zezezzePas encore d'évaluation

- CorrectionExamen1ereSessionNFA002 2011-2012Document9 pagesCorrectionExamen1ereSessionNFA002 2011-2012lamalama8Pas encore d'évaluation

- TD Interblocage 2021Document4 pagesTD Interblocage 2021chaouki Ague100% (1)

- Correction CC2Document4 pagesCorrection CC2milouxzilouPas encore d'évaluation

- Cours Compilation Chapitre 3Document12 pagesCours Compilation Chapitre 3Emma HcnPas encore d'évaluation

- Interblocage PDFDocument5 pagesInterblocage PDFHmidaPas encore d'évaluation

- SystemeDocument1 pageSystemeNaquis Tepiele100% (1)

- Technologies Du Web PDFDocument3 pagesTechnologies Du Web PDFSelma ArabiPas encore d'évaluation

- 3 1 TD3 Ethernet - CSMA - CD - CorrectionDocument4 pages3 1 TD3 Ethernet - CSMA - CD - Correctionamani sayariPas encore d'évaluation

- 3 Sujets Concours Dacces Au Doctorat en Informatique ReseauxDocument15 pages3 Sujets Concours Dacces Au Doctorat en Informatique Reseauxcloud master100% (1)

- TD3 Big DataDocument2 pagesTD3 Big DataMohamed Sidi BrahimPas encore d'évaluation

- Chapitre 3Document49 pagesChapitre 3Hamza BeninePas encore d'évaluation

- Exercice 1: Les Interruptions LogiciellesDocument2 pagesExercice 1: Les Interruptions LogiciellesMounia ChakkourPas encore d'évaluation

- 2014 05 Examen Compilation CorrectionDocument4 pages2014 05 Examen Compilation CorrectionChouichi Ghada100% (1)

- Solutionnaire Exo - 1-2-3-4Document2 pagesSolutionnaire Exo - 1-2-3-4Colmain NassiriPas encore d'évaluation

- Exam SE1 2010-2011Document4 pagesExam SE1 2010-2011Khaled AbdessalemPas encore d'évaluation

- TD Cryptographie - LP ASR - 120251Document9 pagesTD Cryptographie - LP ASR - 120251stanis kamdoumPas encore d'évaluation

- DS Sepc 20 11 2015Document9 pagesDS Sepc 20 11 2015Dhia BenkhaledPas encore d'évaluation

- Examen Et corrigérattrapageSD2023 - 231109 - 073149Document3 pagesExamen Et corrigérattrapageSD2023 - 231109 - 073149Djihene BabaheniniPas encore d'évaluation

- TD1Document4 pagesTD1Nouaman MohamedPas encore d'évaluation

- Série Exercices TD1Document2 pagesSérie Exercices TD1Colmain Nassiri100% (2)

- Tdscheduling2020 2021Document3 pagesTdscheduling2020 2021Atashi Tsunagu (“Albedo”)Pas encore d'évaluation

- Open MPDocument2 pagesOpen MPJalel IbtiPas encore d'évaluation