Académique Documents

Professionnel Documents

Culture Documents

Atelier 1 - 2023 - 2024

Atelier 1 - 2023 - 2024

Transféré par

Mõ Hà Mèd SaidaniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Atelier 1 - 2023 - 2024

Atelier 1 - 2023 - 2024

Transféré par

Mõ Hà Mèd SaidaniDroits d'auteur :

Formats disponibles

Département Génie Electrique Cycle Ingénieur GEMI

Atelier sur le module Systèmes embarqués Temps réel

202023/2024

Programmation VHDL

Pr. Amami

Atelier : Implementation du code VHDL pour la synthèse des compteurs

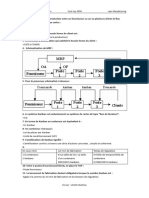

Atelier 1 : Description en VHDL d’un compteur 3bits : le compteur arrête de

compter si Raz est égale à 1

Pr. Amami Benaissa, FST Tanger 2023/2024

Pr. Amami Benaissa, FST Tanger 2023/2024

-- Compteurs 3 bits synchrone

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

ENTITY Compteur IS

PORT (

clk,raz :IN std_logic;

qs : OUT std_logic_vector(3 downto 0)); -- sortie véritable

END Compteur;

ARCHITECTURE Compteur_3bits OF Compteur IS

SIGNAL q : std_logic_vector(3 downto 0); -- signal intermédiaire

BEGIN

-- toujours faire :

qs <= q;

Pr. Amami Benaissa, FST Tanger 2023/2024

-- et en même temps RAZ synchrone

PROCESS(clk) BEGIN

IF clk'event and clk='1' THEN

IF raz='1' THEN

q<=(OTHERS=>'0');

ELSE

q<=q+1;

END IF;

END IF;

END PROCESS;

END Compteur_3bits;

Pr. Amami Benaissa, FST Tanger 2023/2024

Atelier 2 : Réalisation d’un Compteur 8 bits est avec reset son affichage sur

les 8 leds de la carte Spartan 3E

Pr. Amami Benaissa, FST Tanger 2023/2024

-- Compteur 8 bit sur spartan 3 E

------------------------------------------------------------------------------

----

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity compteurspartan3E is

port (

CLK : in STD_LOGIC;

RESET_Switch_0 : in STD_LOGIC;

LED : out STD_LOGIC_VECTOR(7 downto 0)

);

end compteurspartan3E;

architecture Behavioral of compteurspartan3E is

signal COUNTER: STD_LOGIC_VECTOR(7 downto 0); -- déclaration du signal COUNTER

(8bits)

signal PRESCALER: STD_LOGIC_VECTOR(25 downto 0); -- déclatation d'un PRESCALER

(26bits)

begin

CounterProcess : process(RESET_Switch_0, CLK) -- sensibilté du process

begin

if rising_edge(CLK) then -- si le compteur est sur le front montant et

if RESET_Switch_0 = '1' then -- si l'intereupteur RESET_Switch_0 est à 1

alors

PRESCALER <= (others => '0'); -- mettre PRESCALER à 0

COUNTER <= (others => '0'); -- mettre le conpteur à 0 aussi

else -- sinon

if PRESCALER < "10111110101111000010000000" then -- si PRESCALER est <

50000000

PRESCALER <= PRESCALER + 1; --incrementer PRESCALER

else -- sinon

PRESCALER <= (others => '0'); -- mettre PRESCALER à 0

COUNTER <= COUNTER + 1; --incrementer le compteur

end if ;

end if;

end if;

end process ;

LED <= COUNTER; --affichage de la valeur de compteur (8bit) sur les 8 leds

end Behavioral;

Pr. Amami Benaissa, FST Tanger 2023/2024

Voici le fichier UCF pour la simulation de compteur 8 bits sur la carte spartan 3 E

NET LED(0) LOC = "F12" | IOSTANDARD=LVTTL;

NET LED(1) LOC = "E12" | IOSTANDARD=LVTTL;

NET LED(2) LOC = "E11" | IOSTANDARD=LVTTL;

NET LED(3) LOC = "F11" | IOSTANDARD=LVTTL;

NET LED(4) LOC = "C11" | IOSTANDARD=LVTTL;

NET LED(5) LOC = "D11" | IOSTANDARD=LVTTL;

NET LED(6) LOC = "E9" | IOSTANDARD=LVTTL;

NET LED(7) LOC = "F9" | IOSTANDARD=LVTTL;

NET RESET_Switch_0 LOC = "L13" | IOSTANDARD=LVTTL;

NET CLK LOC = "C9" | IOSTANDARD=LVTTL;

Atelier 3 : Elaboration d’une horloge 24 fois plus lente que l’horloge

principale

1. cet exemple, nous allons créer un compteur allant de 0 à 23 et en même temps, nous allons utiliser ce signal pour

générer une horloge qui est 24 fois plus lente que celle a l’entrée. Pour ce faire, il faut commencer par réaliser que,

pour compter jusqu'à 23, il faut 5 bits, puisque 25=32). Par la suite, on devrait aussi savoir qu’un compteur est

compose de flip flops et de logique. Il faut donc avoir un process séquentiel (avec clock). Un compteur devrait

augmenter son compte à chaque front montant d’horloge SAUF quand il arrive à 23. Quand il arrive à 23, il doit

recommencer à 0. Ceci est réalisé par le processus principale suivant :

Il est a remarquer que s_compt_sortie n’est pas le nom du signal de sortie. Nous allons créer un fil interne qui sera

connecté a cette sortie. Nous avons le droit de lire et d’écrire dans les fils internes. Par la suite, nous connecterons ce

fil interne a la sortie.

Pour générer l’horloge de sortie, il faut regarder la valeur du compteur et générer ‘1’ la moitie du temps et générer

‘0’ durant l’autre moitie. Pour cette raison, nous avons :

2.. Imaginons cette fois-ci qu’on veuille contrôler le compteur avec un signal externe. Nous voulons que le

compteur incrémente seulement quand un bouton est pesé. Quand on relâche le bouton, on aimerait que le compte

arrête.Pour ce faire, il faut procéder de la même manière que l’exemple précédent. La différence, cependant, est qu’il

y aune condition de plus pour que le compteur fonctionne : « A chaque front montant d’horloge, SI LE BOUTON

EST PESE, tu peux agir comme un compteur. » Le process deviendrait donc ceci :

Pr. Amami Benaissa, FST Tanger 2023/2024

Exemple 18 : Compteur pour faire clignoter deux diodes de de la carte

Spartan 3E, une avec une fréquence de 1hz et l’autre avec une fréquence de 0,5

Hzs :

Tester et Expliquer le code suivant

-- clignotement de deux diodes de la carte Spartan 3E à des fréquences ----

-- différentes

------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Blink_LED is

port (

CLK : in STD_LOGIC;

LED_0 : out STD_LOGIC;

LED_1 : out STD_LOGIC

);

end Blink_LED;

architecture Behavioral of Blink_LED is

signal Counter2: STD_LOGIC_VECTOR(23 downto 0); -- Blink with 0.5 Hz

signal Counter1: STD_LOGIC_VECTOR(24 downto 0); -- Blink with 1 Hz

signal CLK_1Hz: STD_LOGIC;

signal CLK_demiHz: STD_LOGIC;

begin

Prescaler1 : process( CLK)

begin

if rising_edge(CLK) then

if Counter1 < "1011111010111100001000000" then -- Blink with 0.5 Hz

Counter1 <= Counter1 +1;

else

CLK_1Hz <= not CLK_1Hz;

Counter1 <=(others => '0');

end if ;

end if;

end process Prescaler1;

Prescaler2 : process( CLK)

begin

if rising_edge(CLK) then

if Counter2 < "101111101011110000100000" then -- Blink with 0.5 Hz

Counter2 <= Counter2 +1;

else

CLK_demiHz <= not CLK_demiHz;

Counter2 <=(others => '0');

end if ;

end if;

end process Prescaler2;

LED_0 <= CLK_1Hz;

LED_1 <= CLK_demiHz;

Pr. Amami Benaissa, FST Tanger 2023/2024

end Behavioral;

NET LED_1 LOC = "E12" | IOSTANDARD=LVTTL;

NET LED_0 LOC = "F12" | IOSTANDARD=LVTTL;

NET CLK LOC = "C9" | IOSTANDARD=LVTTL;

Pr. Amami Benaissa, FST Tanger 2023/2024

Vous aimerez peut-être aussi

- Question de Cours Communications Par SatellitesDocument2 pagesQuestion de Cours Communications Par SatellitesMõ Hà Mèd SaidaniPas encore d'évaluation

- Réponse Sys EmbarquésDocument5 pagesRéponse Sys EmbarquésMõ Hà Mèd SaidaniPas encore d'évaluation

- Cour Electrotechnique Suite (Partie 3) + Suite TDDocument16 pagesCour Electrotechnique Suite (Partie 3) + Suite TDMõ Hà Mèd SaidaniPas encore d'évaluation

- CC Lean + CorrectionDocument4 pagesCC Lean + CorrectionMõ Hà Mèd SaidaniPas encore d'évaluation

- BouayadNacer RamdaniBDocument67 pagesBouayadNacer RamdaniBMõ Hà Mèd SaidaniPas encore d'évaluation

- Plan-Lean ManufDocument3 pagesPlan-Lean ManufMõ Hà Mèd SaidaniPas encore d'évaluation

- TP GeDocument5 pagesTP GeMõ Hà Mèd SaidaniPas encore d'évaluation

- Analyse Des RisquesDocument2 pagesAnalyse Des RisquesMõ Hà Mèd SaidaniPas encore d'évaluation

- TD3 CorrigeDocument4 pagesTD3 CorrigeMõ Hà Mèd SaidaniPas encore d'évaluation

- Cour Electronique de Puissance GE ET S4 Partie 3Document11 pagesCour Electronique de Puissance GE ET S4 Partie 3Mõ Hà Mèd SaidaniPas encore d'évaluation

- Exercicessolutions 210113 215108Document2 pagesExercicessolutions 210113 215108Mõ Hà Mèd SaidaniPas encore d'évaluation

- TD5 Ing 2021-22Document2 pagesTD5 Ing 2021-22Mõ Hà Mèd SaidaniPas encore d'évaluation

- EXAMEN GRH (AutoRecovered)Document5 pagesEXAMEN GRH (AutoRecovered)Mõ Hà Mèd SaidaniPas encore d'évaluation

- Les Unités Normalisées PuDocument58 pagesLes Unités Normalisées PuMõ Hà Mèd SaidaniPas encore d'évaluation

- Réseaux ÉlectriquesDocument3 pagesRéseaux ÉlectriquesMõ Hà Mèd SaidaniPas encore d'évaluation

- Chapitre VI - Modélisation Des LignesDocument11 pagesChapitre VI - Modélisation Des LignesMõ Hà Mèd SaidaniPas encore d'évaluation

- TD3 Ing22-23Document2 pagesTD3 Ing22-23Mõ Hà Mèd SaidaniPas encore d'évaluation

- Liens Vidéos Méthode de GaussDocument2 pagesLiens Vidéos Méthode de GaussMõ Hà Mèd SaidaniPas encore d'évaluation

- TD2 Ing22-23Document1 pageTD2 Ing22-23Mõ Hà Mèd SaidaniPas encore d'évaluation