Académique Documents

Professionnel Documents

Culture Documents

Add Fpga

Transféré par

amidi5555913Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Add Fpga

Transféré par

amidi5555913Droits d'auteur :

Formats disponibles

ADDITION SUR FPGA (~ 50 minutes)

Les structures périodiques sont assez fréquentes sur circuit intégré. On en trouve notamment

de type linéaire (1D) au sein des unités arithmétiques utilisées pour les calculs sur les entiers,

tel un additionneur série n bits réalisé par aboutement de n cellules FA (full adder =

additionneur binaire complet). Il en existe aussi de type matriciel (2-D) tels les bancs mémoire

et les « matrices de portes » (Gate Arrays en anglais). Ces « GA », qui servent à réaliser des

fonctions booléennes arbitraires (voir un exemple simpliste à la page suivante) vont constituer

le cadre de travail du présent exercice.

Dans un GA, la maille périodique est une cellule choisie pour son universalité. Pour implanter

une fonction booléenne arbitraire f sur un GA, il faut procéder en 3 phases :

1) exprimer f sous la forme d’un schéma n’ayant recours qu’aux fonctionnalités offertes

par la cellule périodique universelle. Cette phase est appelée « mapping » en anglais

(pas de traduction française satisfaisante). Sauf dans des cas triviaux, les

fonctionnalités de la cellule périodique doivent être utilisées plusieurs fois, ce qui

suppose de recourir à plusieurs cellules.

2) « placer » f, c’est-à-dire choisir sur le GA quelles cellules – parmi toutes celles

présentes dans la matrice – vont servir à son implantation.

3) « router » f, c’est-à-dire interconnecter entre elles les entrées/sorties des cellules

retenues par le « placeur » pour que f puisse être effectivement obtenu. Le routage est

d’autant plus court et simple que les cellules retenues sont voisines et judicieusement

placées les unes par rapport aux autres. Physiquement, le routage consiste à mettre en

place des connexions par fils métalliques circulant au-dessus de la matrice de portes.

En fait, les phases 2 et 3 sont très interdépendantes et souvent traitées ensemble au sein de ce

que l’on appelle l’opération de « placement-routage ».

Les GA les plus répandus aujourd’hui sont les FPGA, pour « Field Programmable Gate

Arrays », c’est-à-dire des matrices de portes à interconnexions programmables par champ

électrique. Dans ces FPGA, la matrice de portes est surmontée d’un réseau de communication

programmable par logiciel qui permet d’établir, dans certaines limites, toutes les liaisons

souhaitées entre entrées et sorties de toutes les cellules. Ces composants ont achevé de faire

de l’électronique numérique moderne une discipline purement informaticienne du point de

vue de l’utilisateur. Dans les FPGA actuels, la cellule périodique a une complexité de l’ordre

d’une dizaine de portes NAND, et cette cellule périodique est répétée jusqu’à plusieurs

millions de fois. Ces FPGA sont parfaitement adaptés au prototypage d’applications ainsi qu’à

de la production en petite et moyenne série. L’enseignement de l’électronique numérique à

l’ENSTA en 2ème et 3ème année est justement basé sur l’utilisation de FPGA et de chaînes

logicielles permettant de les configurer à volonté.

Ici, c’est à la main que l’on va implanter la cellule FA sur FPGA. On considère un FPGA dont

la cellule périodique est un MUX (multiplexeur 2 vers 1). Le mapping va donc consister en

une expression sous forme de BDD. On utilisera comme ordre des variables : cin, a, b.

a) Etablir le BDD représentant la fonction majorité qui fournit la retenue cout. Procéder en

dessinant un arbre binaire de MUX à trois étages et en faisant apparaître la table de vérité au

niveau des feuilles. Puis simplifier le BDD pour l’amener sous sa forme réduite.

b) Exploiter maintenant la « version BDD » ( f(x,Y) = MUX[x,f(1,Y),f(0,Y)] ) du principe

d’expansion de Boole pour établir les BDD correspondant à la retenue (fonction majorité) et à

Addition sur FPGA - 1/5

la somme (fonction parité). Arrêter chaque branche dès qu’apparaît une variable, la masse (0),

ou l’alimentation (1). En profiter au passage pour identifier la manière dont certains

opérateurs booléens unaires et binaires usuels sont implantés au moyen d’un (ou deux) MUX.

c) A sauter s’il reste moins de 20 mn avant la fin de la PC cout s

Voici ci-contre un autre circuit à base de MUX qui implante 0 1 0 1

un additionneur binaire complet. Vérifier son fonctionnement. a 0 1

Quel rapport y a-t-il avec les BDD ?

cin

b

d) La figure ci-dessous montre une petite portion de FPGA à base de portes NAND, c’est-à-

dire une matrice périodique de portes NAND dont entrées et sorties peuvent être connectées

arbitrairement (dans certaines limites) via à un réseau de communication associé. Les canaux

de communication possibles apparaissent en trait fin. Physiquement, ce sont des pistes (fils)

métalliques. Canaux horizontaux et canaux verticaux courent à des niveaux différents et ne se

touchent donc pas quand ils se croisent. Les portions utilisées des canaux sont indiquées en

trait gras. Les points noirs indiquent des « soudures » entre canaux horizontaux et verticaux.

Dans certains FPGA, ces soudures sont réalisées au moyen de fusibles ou d’antifusibles que

l’on fait griller ou claquer (technologie programmable une seule fois), dans d’autres, elles sont

réalisées par des multiplexeurs pilotés logiciellement (technologie reprogrammable).

cout

b s

cin

Un concepteur a déjà fait le travail de « mapping », de placement et de routage de la cellule

FA. Vérifier son travail et en commenter la qualité, notamment dans la perspective de

l’implantation d’additionneurs série.

e) Dans le début de l’exercice, c’est un FPGA à base de MUX qui était considéré. De ce fait,

l’existence d’un « mapping » était garantie quelle que soit la fonction à implanter, grâce à la

version BDD de l’expansion de Boole. Qu’en est-il sur un FPGA à base de portes NAND ?

Addition sur FPGA - 2/5

Corrigé

a) Le BDD non réduit apparaît en haut à gauche ci-dessous. Le symbole rectangulaire avec un

0 et 1 à l’intérieur représente (comme vu en cours) un multiplexeur (alias sélecteur) 2 vers 1

avec signal de contrôle sur le côté. Si le signal de contrôle vaut 0 (resp. 1), c’est la donnée en

face de 0 (resp. 1) qui passe. On réduit le BDD en 3 temps. Le BDD réduit obtenu représente

de manière unique la fonction majorité. Les variables a, b, cin n’interviennent ici qu’au niveau

du contrôle des multiplexeurs (connexions horizontales). Dans la question suivante, orientée

vers l’implantation, on se permettra de se servir des variables en tant que données en entrée

d’un multiplexeur, prenant ainsi une légère distance avec le caractère canonique de la

représentation BDD.

cout cout

cin 0 1 Suppression cin 0 1

des faux choix

a 0 1 0 1 a 0 1 0 1

0 1

b 0 1 0 1 0 1 0 1 b 0 1 0 1

0 0 0 1 0 1 1 1 Suppression 0 1 0 1

des doublons

non terminaux

cout cout

cin 0 1 cin 0 1

Suppression

a 0 1 0 1 des doublons a 0 1 0 1

terminaux 0 1

b 0 1 b 0 1

0 1

0 1

b) Voir figure ci-dessous.

cout = a·b + a·cin + b·cin s = a ⊕ b ⊕ cin

cin 0 1 cin 0 1

a·b a+b a⊕b (a ⊕ b)’

a 0 1 0 1 a 0 1 0 1

0 b b 1 b b’ b’ b

AND OR XOR b 0 1

1 0

NOT

c) Pour les curieux, on vérifie tout de même qu’il s’agit bien d’un FA. On reconnaît tout

d’abord les portes XOR implantées par MUX, à gauche et à droite, d’après la question

précédente. Pour le MUX du centre, on vérifie ensuite que cout = MUX(a⊕b,cin,b) = a’·b·cin

+ a·b’·cin + a·b, qui est une expression booléenne de la fonction majorité. Il s’agit donc bien

d’un additionneur binaire complet. Il n’utilise que 5 MUX au lieu des 7 dont nous avions

besoin dans la question précédente. Pour abaisser ainsi le coût, il y a une astuce : la variable

Addition sur FPGA - 3/5

de contrôle des 2 MUX situés en haut n’est pas une variable d’entrée, mais une fonction, en

l’occurrence a⊕b. Ainsi, ce circuit sort du cadre strict des BDD. Il n’en est pas moins

intéressant en vue de l’implantation sur la matrice de MUX. Pour information, ce circuit n’a

pas été conçu par un être humain mais découvert par un ordinateur ayant brutalement passé en

revue tous les montages possibles par ordre croissant du nombre de MUX. Deux

implantations du FA avec seulement 5 MUX ont été trouvées au bout de plusieurs jours de

calcul par une station de travail du milieu des années 90.

d) La vérification du mapping consiste à s’assurer que les portes NAND utilisées ont bien été

connectées de manière à calculer les fonctions cout et s. Une méthode systématique, amorcée

sur la figure ci-dessous, consiste à établir la fonction booléenne calculée par chaque porte.

cout

(ab)’ (a b)’ a b

a’

a R U T Y

cin’

b’

b S V X Z s

a+b

cin

Mais c’est un peu fastidieux et pas forcément très instructif. Fort d’une analyse partielle du

montage, on peut aussi tenter de se mettre à la place du concepteur et deviner sa démarche. Or

un résultat important de la PC2 était justement une cellule FA optimisée en vitesse, avec la

porte NAND privilégiée pour sa rapidité. Le schéma de cette cellule est rappelé ci-dessous à

gauche et c’est effectivement lui qui a servi de point de départ au mapping.

a b

x y x y x’ y’ x y

x y

cout cin

= =

(x⊕y)’

(x⊕y)’ (x⊕y)’

Addition sur FPGA - 4/5

Partant de ce montage, il a fallu implanter porte OR et porte XNOR avec des portes NAND,

ce qui se fait facilement grâce aux lois de De Morgan (ou bien en jouant avec les bulles). En

effet a+b = (a’·b’)’ et (x⊕y)’ = xy+x’y’ = ( (xy)’ · (x’y’)’ ). Une porte XNOR s’implante

donc au moyen de 3 portes NAND en disposant des entrées complémentées, comme le montre

la figure ci-dessus à droite, qui rappelle au passage comment avait été implanté (a⊕b)’ dans la

cellule FA de la PC2. Par ailleurs, un inverseur est obtenu simplement en connectant entre

elles les deux entrées d’une porte NAND. C’est en suivant ces principes que la cellule FA a

été « mappée » en portes NAND. Revenant à la figure qui présente l’implantation sur le

FPGA, des lettres apparaissent dans certaines portes NAND afin de pouvoir les désigner. On

identifie désormais facilement les triplets RST et XYZ qui implantent chacun une porte

XNOR. On les reconnaît grâce à leur entrées croisées complémentées : chacune des deux

entrées va telle quelle vers une porte NAND et complémentée vers l’autre. Les deux portes U

et V constituent la chaîne de propagation de la retenue au sein du FA, coeur du travail de la

PC2. Les autres portes NAND sont utilisées en inverseur.

Il reste à commenter le travail de placement-routage. La cellule « full adder » a été implantée

de façon compacte (sans trou) au sein d’un rectangle de taille 6X2. Cette forme rectangulaire

aplatie est bien adaptée à l’aboutement de plusieurs FA les uns aux dessus des autres afin

d’implanter facilement un additionneur série. D’ailleurs, les retenues entrante et sortante sont

déjà positionnées pour que cet aboutement se fasse naturellement. Le placement des cellules a

été fait de manière à rendre le routage le plus court possible et, de fait, les connexions établies

ne servent presque qu’à relier entre elles des portes NAND immédiatement voisines.

e) Cette question a déjà été évoquée à plusieurs reprises. On la f(0,Y) x f(1,Y)

traite ici rigoureusement. On montre récursivement que toute x’

fonction booléenne peut s’implanter uniquement avec des

portes NAND à 2 entrées en exhibant une version « tout

NAND » de l’expansion de Boole. C’est à peu de choses près

un travail déjà fait en PC2 pour minimiser le délai de calcul

d’une fonction par rapport à la variable x. Ci-contre, on

rajoute simplement une porte NAND servant d’inverseur pour

produire x’.

f(x,Y)

Addition sur FPGA - 5/5

Vous aimerez peut-être aussi

- Cours Electronique NumeriqueDocument50 pagesCours Electronique NumeriqueDheker Amara100% (1)

- Presentation API Rest, RestFull Et Symfony APIDocument64 pagesPresentation API Rest, RestFull Et Symfony APIOusseynou Diop100% (2)

- Corrige Examen Fpga 2012 2013Document6 pagesCorrige Examen Fpga 2012 2013amidi5555913100% (2)

- Automatique ExercicesDocument4 pagesAutomatique ExercicesOmar Demnati75% (4)

- Laison Srie ModbusDocument8 pagesLaison Srie Modbusamidi5555913Pas encore d'évaluation

- Catalogue IAP - DZ 2018Document797 pagesCatalogue IAP - DZ 2018amidi5555913100% (8)

- Cours Machine SynchroneDocument7 pagesCours Machine SynchroneGELMSE80% (5)

- Cours Fonctions LogiquesDocument9 pagesCours Fonctions LogiquesHîChàmBàQàsPas encore d'évaluation

- Cours Sur Les TransistorsDocument9 pagesCours Sur Les TransistorsAyoub AbPas encore d'évaluation

- 3eme GE PDFDocument223 pages3eme GE PDFOumayma Shili100% (2)

- Bipolaire Cours - Projection - MASSON PDFDocument190 pagesBipolaire Cours - Projection - MASSON PDFamidi5555913Pas encore d'évaluation

- Fichier InformatiqueDocument6 pagesFichier Informatiqueamidi5555913Pas encore d'évaluation

- (Ingdz - Com - Azou Annabi) Cours Electrotechnique BaseDocument78 pages(Ingdz - Com - Azou Annabi) Cours Electrotechnique BaseSoufiane HazelPas encore d'évaluation

- IRSN Demarches de Surete Controle Commande Numerique 2017Document39 pagesIRSN Demarches de Surete Controle Commande Numerique 2017amidi5555913Pas encore d'évaluation

- 149-Fiche Technique Eng 902pDocument8 pages149-Fiche Technique Eng 902pamidi5555913Pas encore d'évaluation

- Vanne AutomatiqueDocument2 pagesVanne Automatiqueamidi5555913Pas encore d'évaluation

- Communique Vignette2018 FRDocument2 pagesCommunique Vignette2018 FRamidi5555913Pas encore d'évaluation

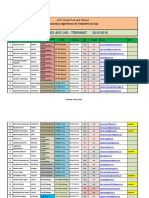

- DELEGUES AIG 2015 2018 Au 6 Sept 2016finale 4Document5 pagesDELEGUES AIG 2015 2018 Au 6 Sept 2016finale 4amidi5555913Pas encore d'évaluation

- 100 Manuel PlantwatchProDocument56 pages100 Manuel PlantwatchProamidi5555913Pas encore d'évaluation

- 815 GDA Automate SecuriteDocument9 pages815 GDA Automate Securitejocky1972Pas encore d'évaluation

- Ghid de CumparareDocument5 pagesGhid de CumpararePop-Coman SimionPas encore d'évaluation

- IP12Document1 pageIP12amidi5555913Pas encore d'évaluation

- B 8002180 ADocument12 pagesB 8002180 Aamidi5555913Pas encore d'évaluation

- MVXseries FRDocument4 pagesMVXseries FRamidi5555913Pas encore d'évaluation

- TS1131Document1 pageTS1131amidi5555913Pas encore d'évaluation

- HabilitationDocument10 pagesHabilitationamidi5555913Pas encore d'évaluation

- 8 ModbusDocument9 pages8 Modbusamidi5555913Pas encore d'évaluation

- Melancon SchutzDocument7 pagesMelancon Schutzamidi5555913Pas encore d'évaluation

- La Chute LibreDocument3 pagesLa Chute Libreamidi5555913Pas encore d'évaluation

- EplanDocument148 pagesEplanpo545Pas encore d'évaluation

- P10 CertDocument19 pagesP10 CertdidatazePas encore d'évaluation

- Prosit 2Document24 pagesProsit 2Wajjih AlouiniPas encore d'évaluation

- TD4 Pa-ApiDocument3 pagesTD4 Pa-Apiismail.moussaPas encore d'évaluation

- Matière: Programmation Orientée Objet TP5Document3 pagesMatière: Programmation Orientée Objet TP5BlaN7kPas encore d'évaluation

- 10-Fiche 9 444 445 453 Documentation Enregistrements V2Document13 pages10-Fiche 9 444 445 453 Documentation Enregistrements V2adam_3000Pas encore d'évaluation

- Jeu de DéDocument18 pagesJeu de DéachbanimonaPas encore d'évaluation

- Programme Formation TS PDFDocument7 pagesProgramme Formation TS PDFIyade FePas encore d'évaluation

- Merise 1Document18 pagesMerise 1Fortune SohnangouPas encore d'évaluation

- Serie 3xDocument4 pagesSerie 3xdieslenPas encore d'évaluation

- Affichage BoudaaDocument5 pagesAffichage BoudaaSara AboubakrPas encore d'évaluation

- RPI2DMD 2 Quick Start Guide March 2020 V2Document4 pagesRPI2DMD 2 Quick Start Guide March 2020 V2willoute1Pas encore d'évaluation

- OpenmairieDocument119 pagesOpenmairieBakary DjabyPas encore d'évaluation

- Ofppt Logo - Google SearchDocument1 pageOfppt Logo - Google SearchAbderrazak IdrissiPas encore d'évaluation

- Rapport Final PFE PDFDocument52 pagesRapport Final PFE PDFbaha eddine Ben SassiPas encore d'évaluation

- ExamComplexité2021 2022 CorrigéDocument5 pagesExamComplexité2021 2022 CorrigéEdina ADJARO PATOUSSIPas encore d'évaluation

- Articles I McdonaldsDocument8 pagesArticles I McdonaldsciscomouhPas encore d'évaluation

- Intégration Des Big Data Avec L Approche ETLDocument20 pagesIntégration Des Big Data Avec L Approche ETLBadoo BadouPas encore d'évaluation

- Atelier 4 CssDocument5 pagesAtelier 4 Cssbarhoumi oussamaPas encore d'évaluation

- AjaxDocument31 pagesAjaxAhmet ElY'yPas encore d'évaluation

- Rapport Abd Fateh 2022Document72 pagesRapport Abd Fateh 2022saifmaddouri112Pas encore d'évaluation

- Livre Blanc SQL ServerDocument23 pagesLivre Blanc SQL Servera.rharrabPas encore d'évaluation

- Pmtic Env NumeriqueDocument125 pagesPmtic Env NumeriqueOuijdane AICHPas encore d'évaluation

- CV NouiliDocument2 pagesCV Nouilihamza orfPas encore d'évaluation

- C.V. de Jean-Michel DoudouxDocument4 pagesC.V. de Jean-Michel DoudouxAbraham ABOUA BOROPas encore d'évaluation

- MoCoAUDITSOFT - Présentation D'un Exemple de RéalisationDocument67 pagesMoCoAUDITSOFT - Présentation D'un Exemple de RéalisationBenoît-René RIVIEREPas encore d'évaluation

- FR - Eon v5 UtilisationDocument83 pagesFR - Eon v5 UtilisationHajjiNizarPas encore d'évaluation

- Applications Générales ArcGisDocument23 pagesApplications Générales ArcGisNassima TabloulPas encore d'évaluation

- Types Des Collections enDocument8 pagesTypes Des Collections enKawtar HachimyPas encore d'évaluation

- Legifrance Modernise Guide de Prise en Main Rapide v1.2Document25 pagesLegifrance Modernise Guide de Prise en Main Rapide v1.2nemiosPas encore d'évaluation