Académique Documents

Professionnel Documents

Culture Documents

Bases 1

Transféré par

Charbel TadrosTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Bases 1

Transféré par

Charbel TadrosDroits d'auteur :

Formats disponibles

Le langage VHDL P.

N ENSEIRB

Les bases

1.0 Introduction

1.1 Historique

Le VHDL (Very High Speed Integrated Circuit, Hardware Description Lan-

guage) est le fruit du besoin de normalisation des langages de description de

matériel (Première norme IEEE 1076-87 en décembre 1987).

Auparavant, chaque fournisseur de CAO proposait son propre langage de modéli-

sation (GHDL chez GENRAD, BLM ou M chez Mentor Graphics, Verilog chez

Cadence etc...) mais aussi un autre langage pour la synthèse et encore un autre

pour le test. Au début des années 80, le ministère de la défense des Etats Unis

(D.O.D) confiait le soin à Intermetrics, IBM et Texas Instruments de mettre au

point ce langage. L’objectif était bien sûre de s’assurer une certaine indépen-

dance vis à vis des fournisseurs de matériels et de logiciels et ainsi une assurance

de maintenabilité des équipements.

En 1994 la version IEEE 1076-93 suivie du standard IEEE 1164 fut établie.

Celui-ci rajoute la notion de forces sur les signaux et est souvent appelé MVL9

(multivalued logic, nine values).

Il y aura aussi la norme IEEE 1076.3 (Numeric Standart pour la synthèse).

En 1995, afin de normaliser les méthodes de modélisation des retards des circuits

ASIC ou FPGA, de grands industriels se sont associés dans la ”VITAL initiative”

(VHDL Initiative Toward ASIC Libraries) fournissant des bibliothèques normali-

sées VITAL. Ceci est concrétisé par la norme IEEE 1076.4

Très récemment, le VHDL a connu une nouvelle extension avec la première

norme IEEE-1076.1-1999 du langage de modélisation mixte VHDL-AMS

1.2 Qu’est ce que le VHDL?

Le VHDL est un langage portable qui va trouver place dans le cycle de concep-

tion du niveau spécification au niveau porte mais aussi lors de la génération des

vecteurs de test. La description VHDL est inséparable de la simulation de type

événementielle.

On peut apprécier le coté généraliste du langage et développer un niveau d’abs-

traction souhaité. Ce sera le cas pour des routines de test ou des descriptions

comportementales. On fera alors de la modélisation.

Les bases Page 1

ENSEIRB P.N Le langage VHDL

Il est aussi possible de rester le plus prés possible du niveau portes et utiliser un

VHDL de synthèse qui apparaît comme un sous-ensemble du VHDL. Comme

langage source d’un synthétiseur, le VHDL permet d’étendre très largement les

bibliothèques en conception d’Asic ou encore de favoriser la conception descen-

dante. Les descriptions sont alors fortement documentées.

On peut aussi être obligé d’utiliser des descriptions VHDL puisque des outils de

description de plus haut niveau sont capables de générer du VHDL privilégiant la

forme netlist; le langage est alors la couche d’interface indispensable (car porta-

ble) dans le flot de conception.

Le VHDL de synthèse est très différent du

VHDL généraliste mais compatible.

1.3 Remarque

Il ne faut pas opposer le VHDL aux autres outils de description plus traditionnels

tels que la schématique. En effet, les systèmes de CAO savent de plus en plus tra-

duire un schéma en VHDL ou inversement créer un schéma à partir du VHDL.

La mixité est aussi une excellente pratique puisqu’en définitive pour qu’une des-

cription soit bonne c’est à dire lisible il faut savoir ce que l’on cache et ce que

l’on montre et comment.

2.0 Unités de conception

2.1 Définition

Une unité de conception est une partie de programme qui peut être compilée

séparément. Cet aspect modulaire est la base de la structuration de la description.

Le support du programme est un fichier texte qui peut contenir une ou plusieurs

unités.

Par défaut le résultat de compilation sera placé dans une bibliothèque ayant

comme nom logique WORK. Pour la compilation de plusieurs unités, un certain

ordre devra être respecter à cause de leur dépendance éventuelle.

Les unités de conception primaires correspondent à la vue externe des objets.

•La spécification d’entité (ENTITY) (très proche du symbole en schémati-

que) définie les signaux d’entrées-sortie, leur type ainsi que leur mode (lec-

ture seule, écriture seule, lecture-écriture) ainsi que les procédures

éventuellement associées (par exemple: vérifications de relations temporel-

les). La généricité permet de parametrer ces définitions.

Page 2 Les bases

Le langage VHDL P.N ENSEIRB

•La spécification de paquetage (PACKAGE) permet de regrouper des

déclarations de types et/ou de sous-programmes et en fait de construire des

bibliothèques. Elle offre ainsi la possibilité d’exporter un de ces objets.

Les unités de conception secondaires correspondent aux algorithmes des modè-

les et des sous-programmes.

•L’architecture (ARCHITECTURE) est relative à une entité. Elle contient

les fonctionnalités et éventuellement les relations temporelles du modèle

(dans une description en vue de la synthèse, il ne doit pas y avoir de retards,

ceux-ci sont liés à la technologie).

•Le corps de paquetage (PACKAGE BODY), pas toujours nécessaire, con-

tient l’écriture proprement dite des fonctions ou des procédures déclarées

au niveau paquetage.

La configuration (CONFIGURATION) est une unité de conception primaire qui

permet de créer un couple entité-architecture (plusieurs architectures pouvant

être associées à une entité). Dans les cas simple, elle peut être remplacée par une

ligne comportant la clause USE...

Vue externe

Entity Package Configuration

Architecture Package Body

Description Types, sous-programmes

2.2 Exemple simple

1 ENTITY comparateur IS

2 PORT(

3 SIGNAL a : IN bit_vector(7 DOWNTO 0);

4 SIGNAL b : IN bit_vector(7 DOWNTO 0);

5 SIGNAL egal : OUT bit);

6 END ;

•Le mot clef SIGNAL peut être omis car pris par défaut

•Le mode IN protège le signal en écriture.

•Le mode OUT protège le signal en écriture.

7 ARCHITECTURE simple OF comparateur IS

8 -- zone de déclaration vide

9 BEGIN

10 egal <= ’1’ WHEN a = b ELSE ’0’;

11 END simple ;

Les bases Page 3

ENSEIRB P.N Le langage VHDL

3.0 Description Structurelle

C´est une description de type hiérarchique par liste de connexions tout à fait

comparable à la réalisation d´un circuit imprimé comprenant des supports, des

circuits et des équipotentielles.

Une description est structurelle si elle comporte un ou plusieurs composants (mot

clé: COMPONENT). Ceux-ci jouent le rôle de support pour le câblage. Ils doi-

vent donc avoir le même aspect extérieur que les modèles qu´ils vont supporter. Il

est, bien sûre, possible de concevoir des structures imbriquées donc à plusieurs

niveaux de hiérarchie.

Pour de telles descriptions, la marche à suivre est la suivante:

• Déclarer autant de composants que nécessaire: COMPONENT...(exem-

ple lignes 10 et suivantes de structure1, page 4))

• Déclarer les listes de signaux internes nécessaires pour le câblage:

SIGNAL... (exemple ligne 7de structure1, page 4)

• Déclarer quel modèle (couple entité-architecture) doit être utilisé sur

chaque composant. C´est la configuration: clause USE...(exemple lignes

22,23 de structure1)

• Instancier chaque composant en indiquant sa liste de connexions: PORT

MAP... (exemple lignes 26 et suivantes de structure1)

3.1 Exemple d’école

Soit à décrire un simple compteur 4 bits synchrone avec autorisation de comp-

tage et sortie report selon la spécification d’entité suivante:

1 ENTITY compteur4 IS

2 PORT ( h, raz, compter : IN BIT;

3 sortie : OUT BIT_VECTOR( 3 DOWNTO 0);

4 plein : OUT BIT);

5 END;

Le modulo n’est pas fixé à priori et pourra raisonnablement être compris entre 9

et 16.

h sortie

raz

plein

compter

Page 4 Les bases

Le langage VHDL P.N ENSEIRB

3.1.1 Première description de type structurelle

La première idée de découpe structurelle est de considérer le cas général d´une

machine de Moore et de séparer l´état de la machine (4 bascules D) des équations

logiques de type état_présent : état_futur ici représentées par le bloc «calcul» qui

fixe le modulo.

6 ARCHITECTURE structure1 OF compteur4 IS

7 SIGNAL d, s , sb : BIT_VECTOR( 3 DOWNTO 0);

8

9 -- déclaration des composants nécéssaires

10 COMPONENT bascule

11 PORT (h, d, raz : IN BIT;

12 s, sb : OUT BIT);

13 END COMPONENT;

14

15 COMPONENT calcul

16 PORT ( s, sb : IN BIT_VECTOR( 3 DOWNTO 0);

17 compter : IN BIT;

18 d : OUT BIT_VECTOR( 3 DOWNTO 0);

19 plein : OUT BIT);

20 END COMPONENT;

21 -- configuration(si pas d’unité CONFIGURATION)

22 --FOR ALL : bascule USE ENTITY WORK.bascule_d(simple);

23 --FOR ALL : calcul USE ENTITY WORK.equations(par_10);

24 BEGIN

25 ba : bascule -- instanciation par position

26 PORT MAP ( h, d(3), raz, s(3), sb(3));

27 bb : bascule -- instanciation par dénomination

28 PORT MAP ( h => h, d => d(2), raz => raz, s => s(2), sb => sb(2));

29 bc : bascule -- instanciation par position et dénomination

30 PORT MAP ( h, d(1), sb => sb(1), s => s(1), raz => raz);

31 bd : bascule -- instanciation par dénomination

32 PORT MAP ( sb => sb(0), s => s(0), h => h, d => d(0), raz => raz);

33 combi : calcul

Les bases Page 5

ENSEIRB P.N Le langage VHDL

34 PORT MAP ( s, sb, compter, d, plein);

35 sortie <= s;

36 END structure1;

Le bloc «calcul» est lui-même défini par une entité et une architecture associée

(dans notre exemple, l´implantation d´une décade).

1 ENTITY equations IS

2 PORT ( s, sb : IN BIT_VECTOR( 3 DOWNTO 0);

3 compter : IN BIT;

4 d : OUT BIT_VECTOR( 3 DOWNTO 0);

5 plein : OUT BIT);

6 END;

7

8 --Implantation directe des équations d´une décade

9 -- A = b*c*d + a * /d

10 -- B = /b * c*d + b* ( /c+/d)

11 -- C = /a*/c*d + c*/d

12 -- D = /d

13 -----------------------------------------------------------------------------

14 ARCHITECTURE par_10 OF equations IS

15 SIGNAL pas_compter : BIT;

16

17 BEGIN

18 pas_compter <= NOT compter;

19 d(3) <= (compter AND s(2) AND s(1) AND s(0))

20 OR (s(3) AND (sb(0) OR pas_compter)) ;

21 d(2) <= (compter AND sb(2) AND s(1) AND s(0))

22 OR ( s(2) AND (pas_compter OR sb(1) OR sb(0)));

23 d(1) <= (compter AND sb(3) AND sb(1) AND s(0))

24 OR ( s(1) AND (pas_compter OR sb(0)));

25 d(0) <= compter XOR s(0);

26

27 plein <= s(3) AND s(0);

28 END ;

De même, la bascule D possède son propre modèle (ou ses propres modèles)

1 -- Fichier : bascule_d_e.vhd

1 ENTITY bascule_d IS

2

3 PORT ( h, d ,raz, ra1 : IN BIT;

4 s, sb : OUT BIT);

5

6 USE WORK.utils.all;

7 CONSTANT Tsetup : Time := 5 ns;

8 BEGIN

9 verif_precond (h,d, Tsetup);

10 END bascule_d ;

11

12 -- Fichier : bascule_d_a3.vhd

13 -- Non syhthétisable

14 -- bascule d avec différenciation des retards Tplh et Tphl

15

Page 6 Les bases

Le langage VHDL P.N ENSEIRB

16 ARCHITECTURE avec_retards OF bascule_d IS

17 CONSTANT Tplh : TIME := 2 ns; -- concerne s ou sb

18 CONSTANT Tphl : TIME := 3 ns; -- concerne s ou sb

19 CONSTANT Tplh_asyn : TIME := 1 ns; -- raz concerne sb

20 CONSTANT Tphl_asyn : TIME := 2 ns; -- concerne s

21

22 BEGIN

23

24 p1: PROCESS (ra1, raz, h)

25 BEGIN

26 IF ra1 = ’1’ AND raz = ’0’ THEN

27 s <= ’1’ after Tplh_asyn;

28 sb <= ’0’ after Tphl_asyn;

29 ELSIF ( ra1 = ’0’ AND raz = ’1’) THEN

30 s <= ’0’ after Tphl_asyn;

31 sb <= ’1’ after Tplh_asyn;

32 ELSIF ( ra1 = ’1’ AND raz = ’1’) THEN

33 s <= ’1’ after Tplh_asyn;

34 sb <= ’1’ after Tplh_asyn;

35 ELSE IF (h = ’1’ AND h’EVENT) THEN -- front montant

36 IF (d = ’0’) THEN

37 s <= ’0’ after Tphl;

38 sb <= ’1’ after Tplh;

39 ELSE s <= ’1’ after Tplh;

40 sb <= ’0’ after Tphl;

41 END IF;

42 END IF;

43 END IF;

44 END PROCESS p1;

45

46 END avec_retards;

3.1.2 Deuxième description de type structurelle

L´instruction GENERATE permet de réaliser des instanciations récurrentes, des

instanciations conditionnelles.

Dans l´exemple précédent, les quatre instanciations de bascules peuvent ainsi

être écrit plus simplement en considérant une variable de boucle i variant de 0 à

3. Cette variable rentre dans la définition des signaux nécessaires au câblage mais

aussi à la génération automatique des étiquettes d´instanciation des composants.

7 ARCHITECTURE structure2 OF compteur4 IS

8

9 SIGNAL d, s, sb : BIT_VECTOR( 3 DOWNTO 0);

10 -- déclaration des composants nécéssaires

11 COMPONENT bascule

12 PORT ( h, d, raz : IN BIT;

13 s, sb : OUT BIT);

14 END COMPONENT;

15

16 COMPONENT calcul

17 PORT ( s, sb : IN BIT_VECTOR( 3 DOWNTO 0);

18 compter : IN BIT;

19 d : OUT BIT_VECTOR( 3 DOWNTO 0);

20 plein : OUT BIT);

Les bases Page 7

ENSEIRB P.N Le langage VHDL

21 END COMPONENT;

22 -- configuration (si pas d’unite CONFIGURATION)

23 -- FOR ALL : bascule USE ENTITY WORK.bascule_d(simple);

24 -- FOR combi : calcul USE ENTITY WORK.equations(par_10);

25 BEGIN

26 -- instanciation des composants

27

28 implant : FOR i IN 0 TO 3 GENERATE

29 b : bascule

30 PORT MAP (h, d(i), raz, s(i), sb(i));

31 END GENERATE;

32 combi : calcul

33 PORT MAP ( s, sb, compter, d, plein);

34

35 sortie <= s;

36

37 END structure2;

3.1.3 Troisieme description de type comportementale

En fait un compteur est une fonction de bas niveau qui se décrit très facilement

sans décomposition, on préférera en général cette dernière description (synthéti-

sable) de type comportementale et non hiérarchique.

38 ARCHITECTURE decade OF compteur4 IS

39 USE WORK.utils.ALL;

40

41 SIGNAL tmp : natural RANGE 0 TO 9 := 0;

42 BEGIN

43 P1: PROCESS

44 BEGIN

45 WAIT UNTIL front_montant(h) ;

46 IF raz = ’1’ THEN

47 tmp <= 0;

48 ELSIF compter = ’1’ THEN

49 IF tmp < 9 THEN

50 tmp <= tmp + 1;

51 ELSE

52 tmp <= 0;

53 END IF;

54 END IF;

55 END PROCESS;

56

57 sortie <= convert(tmp,4);

58

59 plein <= ’1’ WHEN tmp = 9 ELSE ’0’;

60

61 END;

Page 8 Les bases

Le langage VHDL P.N ENSEIRB

3.2 Configuration

3.2.1 Objet

Lorsqu’il y a hiérarchie, il est toujours nécessaire de préciser pour chaque com-

posant instancié, quel est le modèle (couple entité-architecture) choisi. Cela se

fait par l’emploi d’une clause USE qui peut être soit locale dans la zone de décla-

ration de l’architecture structurelle, soit explicitement dans une unité CONFIGU-

RATION explicite. Le second cas offre l’avantage d’une compilation séparée et

est parfaitement adapté aux ”gros” projets tandis que la première méthode est

plus adaptée aux cas simples sans problème particulier de configuration (par

exemple un seul modèle disponible).

3.2.2 Application

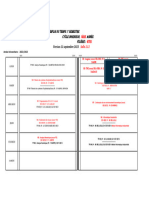

La figure ci-dessous montre les différentes possibilités de configuration.de

compteur4

ENTITY

compteur4

ARCHITECTURE ARCHITECTURE ARCHITECTURE

structure1 structure2 decade

ENTITY ENTITY

equations bascule_d

ARCHITECTURE

par_10

ARCHITECTURE ARCHITECTURE ARCHITECTURE

rtl portes avec_retards

Les bases Page 9

ENSEIRB P.N Le langage VHDL

Pour cet exemple on pourrait considérer:

1 CONFIGURATION compteur4_cfg OF compteur4 IS

2 FOR structure1

3 FOR ALL : bascule USE ENTITY WORK.bascule_d(rtl);

4 END FOR;

5 FOR ALL : calcul USE ENTITY WORK.equations(par_10);

6 END FOR;

7 END FOR;

8 END compteur4_cfg;ou bien...

9

10 CONFIGURATION compteur4_cfg2 OF compteur4 IS

11 FOR structure2

12 FOR implant (0 TO 3)

13 FOR ALL : bascule

14 USE ENTITY WORK.bascule_d(avec_retards);

15 END FOR;

16 END FOR;

17 FOR ALL : calcul USE ENTITY WORK.equations(par_10);

18 END FOR;

19 END FOR;

20 END compteur4_cfg2;

3.3 Compilation

Les unités de conception sont bien compilables séparément mais il faut respecter

la dépendances des fichiers. On peut ainsi compiler sans problème toutes les enti-

tés, puis toutes les architectures en remontant la hiérarchie du circuit, puis la con-

figuration.

De façon générale, au niveau de la compilation, le fichier n’est qu’un support de

texte. Il peut comporter toutes les unités de conception mais dans l’ordre de

compilation! Inversement il peut être souhaitable de s’astreindre à n’avoir

qu’une unité par fichier comme dans l’exemple suivant:

• Fichier compteur4_e.vhd: ENTITY compteur4

• Fichier bascule_d_e.vhd: ENTITY bascule_d

• Fichier equations10.vhd: ENTITY equations, ARCHITECTURE

par_10

• Fichier bascule_d_a1.vhd: ARCHITECTURE rtl

•Fichier bascule_d_a2.vhd ARCHITECTURE portes

• Fichier bascule_d_a3.vhd: ARCHITECTURE avec_retards

• Fichier compteur4_a1.vhd: ARCHITECTURE structure1

• Fichier compteur4_a2.vhd: ARCHITECTURE structure2

• Fichier compteur4_a3.vhd: ARCHITECTURE decade

• Fichier compteur4_cfg.vhd: CONFIGURATION

•Fichier utils.vhd PACKAGE

Page 10 Les bases

Le langage VHDL P.N ENSEIRB

4.0 Simulation événementielle

4.1 Les signaux

Le signal est un objet de première importance car c’est lui qui permet de connec-

ter entre eux les circuits implantés sous forme de processus.Il joue un rôle équi-

valent à celui du noeud ou NET en schématique.

Un signal est caractérisé par

•Un type déclaré

•Un état en référence à ce type

•Un ou plusieurs pilotes (driver) qui lui sont associé

Le pilote du signal contient une liste de couples état-heure celle-ci étant comptée

relativement à l´heure actuelle du simulateur.

Au moment de son exécution, l´instruction VHDl suivante

s <= ´0´, ´1´ AFTER 10 ns,´0´ AFTER 25 ns ;

placera dans la pilote de s:

heure état

0 ´0´

10 ´1´

25 ´0´

Le pilote est en fait une mémoire associée au signal.

4.2 Les événements

On appelle événement tout changement d’état d´un signal. (Alors qu´une transac-

tion est une opération effectuée sur le signal mais qui peut ne pas se traduire par

un événement).Tant qu’un événement potentiel se trouve dans le pilote mais n´est

pas affecté au signal, il est dit non mûr.

4.3 Les processus

Les processus constituent les éléments calculatoires de base du simulateur. Au

niveau descriptif, ils peuvent être explicites (PROCESS) ou implicites (Voir ins-

tructions concurrentes). Du point de vue de l’exécution, on peut affirmer que

«Tout est Processus».

Les bases Page 11

ENSEIRB P.N Le langage VHDL

Tout est Processus

Les Processus sont concurrents

Un processus vit toujours depuis le chargement du code exécutable dans le simu-

lateur. Il ne peut prendre fin qu’avec la simulation mais peut par contre être

endormi pour une durée plus ou moins longue. L’instruction WAIT, obligatoire

au moins une fois, synchronise le processus. Elle possède trois formes pouvant

être combinées :

WAIT ON événement; WAIT FOR durée; WAIT UNTIL condition; WAIT;

Le processus s’exécute au moins une fois jusqu’à rencontrer le WAIT, puis la

condition de réveil une fois validée, l’exécution continue de façon séquentielle et

cyclique (après la fin, le début).

Toujours au moins un WAIT

Un seul WAIT en synthèse

4.4 Déroulement de la simulation

La simulation d’un modèle porte sur les signaux utilisés pour le décrire. Elle est

de type événementielle. Le principe est le suivant:

Au départ l’ heure de simulation est fixée à 0. Des stimuli sont associés aux

signaux d’entrées.

La simulation fonctionne selon le principe d’une roue temporelle.

•Les événements non mûrs sont classés selon les heures futures croissan-

tes.

•L’heure de simulation courante est avancée au premier événement non

mûr de la liste

•Cet événement réveille un processus qui s’exécute immédiatement et

affecte des pilotes.

4.4.1 Premier exemple: Génération d´horloge

SIGNAL h : bit;

BEGIN

horloge : PROCESS

BEGIN

h <= ‘0’, ‘1’ AFTER 75 ns;

WAIT FOR 100 ns;

END PROCESS;

Ce processus produit un signal répétitif de période 100 ns avec 75ns pour le

niveau bas et 25 ns pour le niveau haut.

Page 12 Les bases

Le langage VHDL P.N ENSEIRB

4.4.2 Deuxième exemple: Mémoire Set-Reset

Ce deuxième exemple est purement didactique et non synthétisable

1 ENTITY memoire_rs IS

2 PORT ( s, r : IN BIT;

3 q, qb : OUT BIT);

4 END;

5

6 ARCHITECTURE processus OF memoire_rs IS

7

8 CONSTANT Tplh : TIME := 2 ns;

9 CONSTANT Tphl : TIME := 1 ns;

10 SIGNAL qi : BIT := ‘0’;

11 SIGNAL qbi : BIT := ‘1’;

12 BEGIN

13

14 n1 : PROCESS

15 VARIABLE qtmp : BIT;

16 BEGIN

17 WAIT ON s, qi ;

18 qtmp := s NOR qi; -- la primitive NOR

19 IF qtmp /= qbi THEN -- Test du changement eventuel

20 IF qtmp = ‘0’ THEN

21 qbi <= qtmp AFTER Tphl;

22 ELSE

23 qbi <= qtmp AFTER Tplh;

24 END IF;

25 END IF;

26 END PROCESS;

27

28 n2 : PROCESS

29 VARIABLE qtmp : BIT;

30 BEGIN

31 WAIT ON r, qbi ;

32 qtmp := r NOR qbi; -- la primitive NOR

33 IF qtmp /= qi THEN -- Test du changement eventuel

34 IF qtmp = ‘0’ THEN

35 qi <= qtmp AFTER Tphl;

36 ELSE

37 qi <= qtmp AFTER Tplh;

38 END IF;

39 END IF;

40 END PROCESS;

41 q <= qi;

42 qb <= qbi;

43 END;

Les bases Page 13

ENSEIRB P.N Le langage VHDL

/s + + + + + + + + + + + + +

/r + + + + + + + + + + + + +

/q + + + + + + + + + + + + +

/qb + + + + + + + + + + + + +

0.0 2.0 4.0 6.0 8.0 10.0 12.0

Time(ns)

Expliquer le déroulement de la simulation

5.0 VHDL Langage à instructions concurrentes

5.1 Présentation

•Ces instructions se situent entre BEGIN et END de l’architecture

•L’ordre d’écriture des instructions concurrentes est indifférent.

•Une instruction concurrente est un processus implicite ou explicite sensi-

ble à une liste de signaux de synchronisation.

Au moment de la simulation, toutes les instructions concurrentes sont remplacées

par leur processus équivalent (voir paragraphe 6.4).

Application: Le processus correspond souvent à un circuit simple. Les con-

nexions entre circuits sont automatiquement implantées par les signaux

d’échange.

5.2 Affectation concurrentes des signaux

Les affectations concurrentes de signaux sont particulièrement adaptées à la des-

cription de circuits combinatoires. (Les entrées sont alors les signaux d’activa-

tion des processus équivalents). On parlera de description par flot de données.

Une fonction combinatoire s’exprime simple-

ment par une instruction concurrente

Page 14 Les bases

Le langage VHDL P.N ENSEIRB

5.2.1 Affectation simple

s <= a AND b AFTER 10 ns;

5.2.2 Affectation conditionnelle

On veut par exemple décoder une sortie de compteur:

neuf <= ‘1’ WHEN etat = “1001” ELSE ‘0’;

5.2.3 Affectation avec sélection

Soit à décrire directement un circuit multiplexeur.

SIGNAL e0, e1, e2, e3, s : BIT;

SIGNAL ad : NATURAL RANGE 0 TO 3;

BEGIN

WITH ad SELECT

s <= e0 WHEN 0,

e1 WHEN 1,

e2 WHEN 2,

e3 WHEN OTHERS;

END;

5.3 Affectation séquentielle des signaux

5.3.1 Contexte

Dans un processus déclaré ou dans un sous-programme, il ne peut y avoir que

des instructions séquentielles c’est à dire exécutées dans l’ordre d’écriture l’une

après l’autre. On retrouve ici la programmation classique et le débutant ne man-

quera pas de dire “ça ressemble à du PASCAL”.

5.3.2 Signal et Variable

Une variable ne peut exister que dans un contexte séquentiel, elle est affectée

immédiatement. Elle n’est pas visible à l’extérieur d’un processus

x := 1 + 2; -- x prend la valeur 3

Le signal est le seul objet qui peut être affecté soit de façon concurrente, soit de

façon séquentielle selon le contexte. Il est l’agent de communication entre pro-

cessus.

L’affectation du signal est différé à cause de son pilote. Lors de l’affectation

séquentielle, le ou les couples valeur_future:heure_de_simulation sont placés

dans le pilote. La valeur sera (ou dans quelques cas conflictuels, ne sera pas)

Les bases Page 15

ENSEIRB P.N Le langage VHDL

effectivement passée au signal au moment de la suspension du Process par une

instruction WAIT. (Remarque: on peut être amené à écrire WAIT FOR 0 ns; pour

forcer cette affectation à être immédiate).

C’est le pilote du signal qui est affecté et non

le signal lui-même

s <= 1 + 2 AFTER 10 ns; -- le pilote de s recoit le couple de valeurs 3,10

5.3.3 Illustration 1

L’exemple suivant illustre ce point fondamental.

1 ENTITY varsig IS

2 END;

3

4 ARCHITECTURE exercise OF varsig IS

5 SIGNAL aa, aaa : INTEGER := 3;

6 SIGNAL bb, bbb : INTEGER := 2;

7

8 BEGIN

9 P1: PROCESS

10 VARIABLE a: INTEGER :=7;

11 VARIABLE b: INTEGER :=6;

12 BEGIN

13 WAIT FOR 10 ns;

14 a := 1; --- a est égal à 1

15 b := a + 8 ; --- b est égal à 9

16 a := b - 2 ; --- a est égal à 7

17 aa <= a; -- 7 dans pilote de aa

18 bb <= b ; -- 9 dans pilote de bb

19 END PROCESS;

20 -- à l’heure H = 10 ns , aa prend la valeur 7 , bb prend la valeur 9

21 -- entre 0 et 10 ns aa vaut 1 et bb vaut 2

22

23 P2: PROCESS

24 BEGIN

25 WAIT FOR 10 ns;

26 aaa <= 1 ; -- 1 dans pilote de aa

27 bbb <= aaa + 8; -- 11 dans pilote de b

28 aaa <= bbb - 2; -- 0 dans pilote de aaa

29 END PROCESS;

30 -- à l’heure H = 10 ns , aaa prend la valeur 0, bbb prend la valeur 11

31 -- entre 0 et 10 ns aaa vaut 1 et bbb vaut 2

32 END;

Remarque: De deux affectations successives d’un même signal, seule la

deuxième compte. Le pilote du signal constitue une mémoire associée au signal.

5.3.4 Illustration 2: Mémorisation implicite du signal

Soit dans un PROCESS la séquence suivante ( sur des type bit)

Page 16 Les bases

Le langage VHDL P.N ENSEIRB

WAIT UNTIL h = ’1’;

x <= e; -- e est mis dans le pilote de x

y <= x; -- la valeur actuelle de x est mis dans le pilote de y

On a réalisé un registre à décalage à 2 étages.

Alors que la séquence:

WAIT UNTIL h = ’1’;

x := e; -- x prend la valeur e

y <= x; -- la valeur actuelle de x est mis dans le pilote de y

montre que x n’est qu’un intermédiaire de calcul. En fait, y va recevoir e. C’est une bascule de

type D.

5.4 Processus équivalents aux instructions concurrentes

Puisque «tout est processus», il est toujours possible de décrire un circuit par un

processus explicite même si sa description en instruction concurrente est plus

simple.

Les exemples précédents (paragraphe 5.0) sont réécrits ci-dessous. On notera

dans chaque cas l´emploi de l´instruction WAIT (obligatoire).

•L´affectation concurrente du signal s devient une affectation séquentielle

1 P1: PROCESS

2 BEGIN

3 WAIT ON a, b ;

4 s <= a AND b AFTER 10 ns;

5 END PROCESS;

•Même remarque pour le signal «neuf»

1 P2: PROCESS

2 BEGIN

3 WAIT ON etat ;

4 IF etat = ”1001” THEN

5 neuf <= ´1´ ;

6 ELSE

7 neuf <= ´0´ ;

8 END PROCESS;

•la sortie est combinatoire puisque ne dépendant que de la valeur d´entrée

1 P3: PROCESS

2 BEGIN

3 WAIT ON e0, e1, e2, e3 ;

4 CASE ad IS

5 WHEN 0 => s <= e0 ;

6 WHEN 1 => s <= e1 ;

7 WHEN 2 => s <= e2 ;

8 WHEN 3 => s <= e3 ;

9 END CASE;

10 END PROCESS;

5.5 Application: Descriptions des fonctions séquentielles simples

Ces fonctions sont les plus souvent utilisées dans les descriptions au niveau RTL

(Register Transfert Logic) c´est à dire synthétisable. L´affectation d´un signal

Les bases Page 17

ENSEIRB P.N Le langage VHDL

passant par un pilote, celui-ci fournit souvent le mécanisme de mémorisation

implicite.

Il n´y a, en gros que deux types de circuits: mémorisation de type simple

mémoire (latch) avec synchronisation sur niveau, circuit fondamentalement asyn-

chrone; mémorisation avec synchronisation sur front (bascule), circuit fonda-

mentalement synchrone. L´écriture est strictement la même si le nombre de bits

est supérieur à un (latch ou registres), il suffira de remplacer un type bit par un

type bit_vector par exemple.

Le dernier cas concerne un circuit de type mixte comme une bascule synchrone

avec remise à zéro asynchrone.

•simple mémoire (latch)

1 P1: PROCESS

2 BEGIN

3 WAIT ON h, d;

4 IF h = ´1´ THEN

5 q <= d ;

6 END IF;

7 -- mémorisation implicite lorsque la condition est fausse

8 END PROCESS;

•bascule D avec raz synchrone

1 P2: PROCESS

2 BEGIN

3 WAIT UNTIL h´event and h = ´1´;

4 IF raz = ´1´ THEN

5 q <= ´0´;

6 ELSE

7 q <= d;

8 END IF;

9 -- raz prioritaire

10 END PROCESS;

•bascule D avec raz asynchrone

1 P3: PROCESS

2 BEGIN

3 WAIT ON h, raz ;

4 IF raz = ´1´ THEN

5 q <= ´0´;

6 ELSIF h´event AND h = ´1´ THEN

7 q <= d;

8 END IF;

9 -- raz prioritaire

10 -- mémorisation implicite lorsque la condition est fausse

11 END PROCESS;

6.0 Le délai Delta

On appelle ainsi un retard nul pour l’utilisateur mais correspondant à une unité

d’itèration du simulateur. La forme la plus simple du délai delta est la suivante:

Page 18 Les bases

Le langage VHDL P.N ENSEIRB

s <= e; -- équivalent à: s <= e AFTER 0 ns;

Au moment de la simulation, il n’y a que des processus communiquant entre eux

par des événements sur des signaux. On peut alors voir trois types de temps.

•Le cycle machine caractéristique du processeur exécutant la simulation.

A part des problèmes éventuels de patience à avoir, il ne rentre pas dans la

discussion actuelle.

•Le timestep qui représente la résolution du simulateur (le plus petit temps

simulable hormis 0). Il est fixé en standard à 1 femto seconde. C’est la base

de temps utile pour la simulation.

•Le délai delta sans intérêt à priori pour l’utilisateur (retard nul), mais

essentiel si l’on veut comprendre les problèmes de simultanéités.

L’exemple simple de descriptions équivalentes pour l’utilisateur illustre les diffé-

rences dans les délais delta.

1 ENTITY delta IS

2 PORT ( a,b,c : IN BIT;

3 s : OUT BIT);

4 END;

5

6 ARCHITECTURE un_process OF delta IS

7 BEGIN

8

9 un : PROCESS ( a, b, c)

10 VARIABLE i1, i2 : BIT; -- variables internes

11 BEGIN

12 -- l’ordre d’écriture est nécessaire

13 i1 := a AND b ; -- S1

14 i2 := c OR i1 ; -- S2

15 s <= NOT i2 ; -- S3

16 END PROCESS;

17 END un_process;

18

19 ARCHITECTURE concurrent OF delta IS

20 SIGNAL i1, i2 : BIT; -- signaux internes

21 BEGIN

22 -- n’importe quel ordre pour les instructions

23 i2 <= c OR i1 ; -- C1

24 i1 <= a AND b ; -- C2

25 s <= NOT i2 ; -- C3

26 END;

27

28 ARCHITECTURE plus_simple OF delta IS

29 BEGIN

30 s <= NOT( c OR (a AND b)); -- C0

31 END;

La première et la dernière architecture contiennent un seul PROCESS = Une ité-

ration. Dans tous les cas, la sortie sera affectée à heure de simulation + 1 δ.

Les bases Page 19

ENSEIRB P.N Le langage VHDL

La deuxième contient trois processus équivalents et concurrents relies par des

signaux. Chaque processus nécessité une itération. Dans le pire cas, la sortie sera

affectée à heure de simulation + 3 δ, ou alors ce sera heure de simulation + 2 δ.

a b b

b a c

a c

C2

c

S1

i1

C0 S2

C1

i2 S3

C3

s

s s

7.0 Conclusion

Les exemples simples de ce chapitre ont suggéré les principes suivants en ce qui

concerne la description de circuits:

• Dans la mesure du possible, dans une description, on séparera les parties

clairement séquentielles et les parties clairement combinatoires.

• Pour chaque bloc combinatoire, les instructions concurrentes sont en

général plus directement adaptées.

•Pour chaque bloc séquentiel, les processus explicites sont en général plus

simples à écrire ou à lire. Attention aux mémorisations implicites du signal.

Utiliser au maximum les variables !

Une bonne description est une description lisible. En application des principes ci-

dessus, elle apparaîtra comme un ensemble d’instructions concurrentes et de pro-

cessus concurrents, la liaison entre ces différents blocs se faisant de manière

dynamique (par les signaux) au moment de la simulation ou alors lors de la syn-

thèse du circuit global.

Une bonne description est une description

lisible.

Page 20 Les bases

Vous aimerez peut-être aussi

- Astuces Et Code Vba Pour Excel en FrancaisDocument68 pagesAstuces Et Code Vba Pour Excel en Francaisbassir2010Pas encore d'évaluation

- Cours VHDL Et FPGADocument135 pagesCours VHDL Et FPGAMounira Tarhouni100% (1)

- Impact Du Numerique Dans La Profession de L39expertise Comptable Guide A L39usage Des Salarie.e.sDocument20 pagesImpact Du Numerique Dans La Profession de L39expertise Comptable Guide A L39usage Des Salarie.e.sEya SouissiPas encore d'évaluation

- Programmation Pascal + Exercices CorrigésDocument60 pagesProgrammation Pascal + Exercices CorrigésMohamed Zahry71% (14)

- Conception Et Réalisation D'Un Logiciel de Gestion D'Un Cabinet DentaireDocument37 pagesConception Et Réalisation D'Un Logiciel de Gestion D'Un Cabinet DentaireAbdeldjalil BensiahmedPas encore d'évaluation

- Cours Electronique Numérique Avancée ESTA Pr. F. NADIR (Partie3)Document46 pagesCours Electronique Numérique Avancée ESTA Pr. F. NADIR (Partie3)siss emyPas encore d'évaluation

- Chapitre 5 VHDLDocument91 pagesChapitre 5 VHDLdhdhPas encore d'évaluation

- MEMOIRE BIGDATA Quentin-MathieuDocument93 pagesMEMOIRE BIGDATA Quentin-MathieuNdeye Nafissatou Thiaw Thiaw100% (1)

- Cours VHDLmodfinal1Document57 pagesCours VHDLmodfinal1kheledPas encore d'évaluation

- UE Cybersecurite-TP DVWA v0.6Document58 pagesUE Cybersecurite-TP DVWA v0.6Pape Mignane FayePas encore d'évaluation

- Multiplieur 4 4Document17 pagesMultiplieur 4 4mariemPas encore d'évaluation

- Vhdl GESA Part 1Document65 pagesVhdl GESA Part 1kawtar elbirakiPas encore d'évaluation

- Cours VHDLDocument82 pagesCours VHDLYasser Sdiki0% (1)

- Cours Partie2Document84 pagesCours Partie2Khaled OmraniPas encore d'évaluation

- Cours VHD13-14-1Document30 pagesCours VHD13-14-1Mohamed ZarboubiPas encore d'évaluation

- Typologie FTTHDocument23 pagesTypologie FTTHJaouad AssagPas encore d'évaluation

- TP VHDL 2020-2021Document26 pagesTP VHDL 2020-2021elhaoudar.nassimaPas encore d'évaluation

- Langage VHDLDocument13 pagesLangage VHDLchaimae kacemiPas encore d'évaluation

- Cours VHDLDocument32 pagesCours VHDLYoussef SadikPas encore d'évaluation

- Chap Langage VHDLDocument7 pagesChap Langage VHDLmed.dbara20Pas encore d'évaluation

- Cour VHDL Amami 5 - 2016 PDFDocument71 pagesCour VHDL Amami 5 - 2016 PDFmedPas encore d'évaluation

- 11 Chapitre5.1Document4 pages11 Chapitre5.1Achraf SahriPas encore d'évaluation

- Poly VHDL 2022-2023 Paysage ST JeromeDocument118 pagesPoly VHDL 2022-2023 Paysage ST Jeromeclaude feunePas encore d'évaluation

- Chapitre 1Document16 pagesChapitre 1dhaouadi hazemPas encore d'évaluation

- Cours VHDL 3Document22 pagesCours VHDL 3Amina GhardallouPas encore d'évaluation

- Introduction VHDLDocument24 pagesIntroduction VHDLlaz_chikhi1574Pas encore d'évaluation

- VHDL Chap 2Document134 pagesVHDL Chap 2HIND GUENDOUZPas encore d'évaluation

- Cours 2 VHDLDocument30 pagesCours 2 VHDLAMEL REBBOUCHEPas encore d'évaluation

- VHDL Bousmah 2022Document137 pagesVHDL Bousmah 2022salma chtiouiPas encore d'évaluation

- Support Cours VHDLDocument136 pagesSupport Cours VHDLKhochtali YoussefPas encore d'évaluation

- Chapitre IV - VHDL - 2020Document30 pagesChapitre IV - VHDL - 2020silami fatihaPas encore d'évaluation

- Crs VHDL VFDocument9 pagesCrs VHDL VFtahiri.ahmed2005Pas encore d'évaluation

- Chapitre 1 Introduction To VHDLDocument20 pagesChapitre 1 Introduction To VHDLDhekra JebaliPas encore d'évaluation

- 9 Chapitre5.1Document2 pages9 Chapitre5.1Houssem ReggamPas encore d'évaluation

- Fpga VHDLDocument13 pagesFpga VHDLKdiPas encore d'évaluation

- Licence SRT VHDLDocument38 pagesLicence SRT VHDLsanokho ndiayePas encore d'évaluation

- VhdlexDocument10 pagesVhdlexRiyadh Ben AbdallahPas encore d'évaluation

- Cours À ReproduireDocument7 pagesCours À Reproduiremrd9991Pas encore d'évaluation

- Cours 1 VHDLDocument14 pagesCours 1 VHDLIbra YAACOUBIPas encore d'évaluation

- System 1 Id 048Document8 pagesSystem 1 Id 048Kam ZegPas encore d'évaluation

- Cours2021-2022 Chapitre2Document28 pagesCours2021-2022 Chapitre2Zoghlami AbirPas encore d'évaluation

- Abdou. Cours API - Chapitre II .API. m2 Ce & ElmDocument27 pagesAbdou. Cours API - Chapitre II .API. m2 Ce & ElmsethabdellahPas encore d'évaluation

- CHPITR3Document84 pagesCHPITR3KhadidjaPas encore d'évaluation

- Cours Api Part 5 2022Document19 pagesCours Api Part 5 2022Nour ouzeriPas encore d'évaluation

- VHDL - SBIHIDocument19 pagesVHDL - SBIHIaminefoura6Pas encore d'évaluation

- 4 VHDLDocument66 pages4 VHDLbastaouiiPas encore d'évaluation

- Chap 2 RLPDocument10 pagesChap 2 RLPJiba LassryPas encore d'évaluation

- Le VHDL en Pratique v1.0Document85 pagesLe VHDL en Pratique v1.0Abdelhamid Bahri100% (1)

- Chap5 VHDL UnlockedDocument21 pagesChap5 VHDL UnlockedilyPas encore d'évaluation

- Chap02 - Concepts de Base Du LangageDocument20 pagesChap02 - Concepts de Base Du LangageArrow ArrowPas encore d'évaluation

- Le Langage de Description VHDLDocument46 pagesLe Langage de Description VHDLHicham MahfoudiPas encore d'évaluation

- SynthDocument16 pagesSynthAZEDDINEPas encore d'évaluation

- TP VHDL FpgaDocument13 pagesTP VHDL FpgaJoel Minkeu100% (1)

- Abel PDFDocument9 pagesAbel PDFIbrahima Gueye100% (1)

- Le Langage VHDL A.elkari PDFDocument122 pagesLe Langage VHDL A.elkari PDFAhmed DoghmiPas encore d'évaluation

- Cours INF1427 Module 4 1Document7 pagesCours INF1427 Module 4 1AlainPas encore d'évaluation

- Le Langage VHDL ELKARIDocument112 pagesLe Langage VHDL ELKARIAhmed DoghmiPas encore d'évaluation

- cours1_VHDLDocument48 pagescours1_VHDLFatima Zahra MoughraouiPas encore d'évaluation

- Cours1 VHDLDocument48 pagesCours1 VHDLYASSINE KERWIPas encore d'évaluation

- Langage VHDL 2020Document39 pagesLangage VHDL 2020lolPas encore d'évaluation

- TP 2Document9 pagesTP 2soyed mohamedPas encore d'évaluation

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihPas encore d'évaluation

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- CatalogueDocument24 pagesCatalogueludogravePas encore d'évaluation

- 3 Sys-FichDocument44 pages3 Sys-FichSalah AllouchiPas encore d'évaluation

- CI11 4 1 TP Bureauadistance - EleveDocument8 pagesCI11 4 1 TP Bureauadistance - ElevePhilippeTavernierPas encore d'évaluation

- Module Reseau Td1Document6 pagesModule Reseau Td1كلي غرورPas encore d'évaluation

- Master PRISME Produits de L'information Spécialisée Et Médiation ÉlectroniqueDocument6 pagesMaster PRISME Produits de L'information Spécialisée Et Médiation Électroniqueufr IDISTPas encore d'évaluation

- Cours MicroservicesDocument18 pagesCours MicroservicesBochra ArfaouiPas encore d'évaluation

- 3.5.5 Packet Tracer - Investigate The TCP Ip and Osi Models in Action - FR FRDocument6 pages3.5.5 Packet Tracer - Investigate The TCP Ip and Osi Models in Action - FR FRdhaouadi hazemPas encore d'évaluation

- TP3 SolDocument10 pagesTP3 SolLatifa YahiaPas encore d'évaluation

- Production de Documents Na9laDocument1 pageProduction de Documents Na9laSimo Es100% (1)

- MedaliDocument1 pageMedaliJlizi DaliPas encore d'évaluation

- 6.2.4.4 Packet Tracer - Configuring IPv6 Static and Default Routes InstructionsDocument3 pages6.2.4.4 Packet Tracer - Configuring IPv6 Static and Default Routes InstructionsAbdel GansonrePas encore d'évaluation

- mali-jo-2023-36Document40 pagesmali-jo-2023-36sagaraismaila8Pas encore d'évaluation

- Examen Ccna r&Sv6 Ccna4Document7 pagesExamen Ccna r&Sv6 Ccna4ndiguidePas encore d'évaluation

- Cours Laravel 9 Les Bases Configuration Session Et Gestion de FichiersDocument10 pagesCours Laravel 9 Les Bases Configuration Session Et Gestion de FichiersSatis factionPas encore d'évaluation

- LMD 2016-2017 PDFDocument5 pagesLMD 2016-2017 PDFAssia NourPas encore d'évaluation

- gtr1 - 15 09 2023Document1 pagegtr1 - 15 09 2023ayaPas encore d'évaluation

- 03 Manipulation Des Données Sous MS ExcelDocument34 pages03 Manipulation Des Données Sous MS ExcelViperDi ABPas encore d'évaluation

- Rapport de Stage Pfsense - CopieDocument34 pagesRapport de Stage Pfsense - CopieMamindraibe FloretPas encore d'évaluation

- 13L2 Si-Td3 PDFDocument4 pages13L2 Si-Td3 PDFAnonymous Wpl47Bwu4Pas encore d'évaluation

- 01 Algo03 Ghazi IntroDocument13 pages01 Algo03 Ghazi IntroMillionard Junior PaulPas encore d'évaluation

- 14171 Epreuve e2 Bac Pro Sn Septembre 2021 Risc SujetDocument19 pages14171 Epreuve e2 Bac Pro Sn Septembre 2021 Risc SujetgaleratomPas encore d'évaluation

- TD Architecture Des Ordinateurs 2021-2022Document5 pagesTD Architecture Des Ordinateurs 2021-2022Ouattara larsonPas encore d'évaluation

- CC 217+CorrigéDocument4 pagesCC 217+CorrigéYaacoub El GuezdarPas encore d'évaluation

- Model de RapportDocument19 pagesModel de RapportDelondon AlasckoPas encore d'évaluation

- Java ExamenDocument17 pagesJava ExamenBlarnola LukumaPas encore d'évaluation