Académique Documents

Professionnel Documents

Culture Documents

Fascicule TP Circuits - Fpga 3se

Transféré par

Ben Ahmed AbdelhamidTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Fascicule TP Circuits - Fpga 3se

Transféré par

Ben Ahmed AbdelhamidDroits d'auteur :

Formats disponibles

Atelier «

Circuits FPGA »

Réalisation d’un système d’affichage numérique par une

carte FPGA

Consignes :

- Faire valider le travail relatif à chaque module du système étudié

par l’enseignant.

- Faire valider le code par l’enseignant avant la programmation de la

carte.

I- Introduction :

I-1- Objectifs :

Cet atelier constitue un complément au cours « circuits FPGA » destiné aux

étudiants de la 3ème année licence EEA de spécialité systèmes embarqués et il a

pour but de :

- Découvrir l’architecture des FPGA ainsi que la carte de développement

Digilent basée sur le circuit FPGA SPARTAN-XL-3E.

- Développer des systèmes numériques programmables simples

(multiplexeur, compteur...).

- Simuler des systèmes numériques avec Xilinx ISE.

- Réaliser un système numérique à base de la carte FPGA d’étude

I-2- Les circuits logiques programmables

Ajouter des informations concernant cette section.

I-3- Les circuits FPGA

Ajouter des informations concernant cette section.

I-4- Le développement d’un système on chip FPGA

Ajouter des informations concernant cette section.

[Ecrire le nom et prénom de chaque membre du groupe ici] 1

Atelier « Circuits FPGA »

II- Description des différents outils :

II-1- Le SPARTAN XL-3E - XC3S500E

Ajouter des informations concernant cette section.

II-2- La carte de développement FPGA Spartan-3E XC3S500E de Digilent

Ajouter des informations concernant cette section.

FIGURE 1: CARTE DE DÉVELOPPEMENT FPGA SPARTAN-3E XC3S500E

II-3- Les Outils de développement :

Ajouter des informations concernant cette section.

III- Structuration et simulation du système d’étude

III-1- Structure d’un projet VHDL :

[Ecrire le nom et prénom de chaque membre du groupe ici] 2

Atelier « Circuits FPGA »

Pour décrire les différents systèmes numériques, nous utiliserons le logiciel de

chez Xilinx : ISE Webpack. Ce logiciel est disponible gratuitement, moyennant une

inscription, sur le site de xilinx (www.xilinx.com).

Ce logiciel permet de décrire des systèmes en VHDL ou Verilog, de les tester (de

manière fonctionnelle ou temporelle) et de créer un fichier binaire compatible avec la

cible (ici un FPGA Spartan 3E).

Un projet VHDL est très souvent décomposé en sous-structures, appelées

modules ou composants. Comme on pourrait le faire sur un circuit imprimé, il s’agit

d’instancier différents composants et de les relier entre eux par des fils (signaux en

VHDL) pour réaliser le système complet.

Chacun de ces modules est alors décrit dans un fichier source indépendant. Chacun

de ces fichiers sources peut alors être testé indépendamment en lui associant un

fichier de simulation (ou testbench).

Enfin des fichiers de contraintes permettent de faire le lien entre la description

logicielle et la structure matérielle de la cible et de son environnement (position des

entrées, des sorties...).

III-2- Les phases de développement d’un système sur puce (SoC)

La figure 1 suivante résume les différentes phases nécessaires au développement

d’un système sur puce en générale (SoC) et un système FPGA en particulier.

L’écriture des différents modules (ou composants) est la première chose à

réaliser. Ceux-ci peuvent être décrits et testés séparément.

Ensuite, il est possible (et fortement conseillé) de vérifier la syntaxe de la

description, en faisant appel à la fonction "Check Syntax" dans la partie "Synthetize

XST". Cette étape est assez rapide et ne nécessite pas de connaître la cible,

contrairement à l’étape d’après.

[Ecrire le nom et prénom de chaque membre du groupe ici] 3

Atelier « Circuits FPGA »

FIGURE 2: LES PHASES DE DÉVELOPPEMENT D’UN SYSTÈME SUR PUCE (SOC)

Viens ensuite la phase de synthèse ("Synthetize XST") puis de placement et

de routage ("Implement Design"). Ces étapes nécessitent la connaissance, d’une

part, de la cible (FPGA ou CPLD) et, d’autre part, de l’environnement du circuit

(entrées/sorties associées aux autres composants de la maquette). Il est donc

nécessaire, avant de réaliser ces étapes-là, de faire l’assignation des broches du

composant avec la description fournie. Pour cela, vous pouvez vous aider de la

fonction "Assign Package Pins" dans la partie "User Constraints" et de la

documentation de la maquette fournie en début de ce document.

Il est aussi possible à ce stade de lancer différentes simulations :

- Fonctionnelle : permettant de savoir si le fonctionnement du système est

celui décrit ;

[Ecrire le nom et prénom de chaque membre du groupe ici] 4

Atelier « Circuits FPGA »

- Post-synthèse : permettant, après synthèse, de vérifier à nouveau le

fonctionnement du système ;

- Temporelle : permettant, après l’étape de routage, de valider les contraintes

temporelles associées au placement des "composants".

Ces différentes phases doivent être répétées pour l’ensemble des modules

composant l’application. La dernière étape consiste à produire le fichier de

programmation ("Generate Programming File") et à le transférer dans la mémoire

du FPGA.

III-3- Simulation

Il existe 2 niveaux de simulation :

- Comportementale (behavorial simulation) ;

- Physique (post-route simulation).

Dans la version allégée de Xilinx ISE WebPack, seule la simulation

comportementale est disponible.

Pour tester un module VHDL, il faut lui associer un module générateur de

signaux (non synthétisable) : le testbench.

Le testbench est un module VHDL spécial (disponible dans la liste des

nouveaux modules lors de l’ajout de fichier source). Il inclut le module à tester

comme un composant et lui associe des signaux. L’écriture d’un testbench est

automatisée avec Xilinx ISE.

Il reste ensuite à écrire un scénario de test animant les signaux d’entrée du

module en test. On utilisera alors la même syntaxe qu’un module classique mais

avec des instructions spécifiques.

[Ecrire le nom et prénom de chaque membre du groupe ici] 5

Atelier « Circuits FPGA »

IV- Etude et simulation du système d’affichage

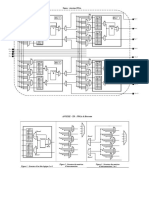

L’objectif de cet TP est celui de réaliser un système d’affichage hexadécimal

sur 4 afficheurs 7 segments fonctionnant en mode multiplexé moyennant la carte de

développement de Digilent basée essentiellement sur le FPGA SPARTAN-XL-3E.

Dans un système d’affichage, le multiplexage est un procédé qui consiste à

utiliser plusieurs voyants ou plusieurs afficheurs et à ne pas tous les allumer à la fois,

en vue d’économiser de l’énergie et de limiter le nombre de fils de câblage. Par

exemple, l’affichage de votre radio réveil numérique, de votre machine à laver ou de

votre four micro-onde est fort probablement multiplexé.

Les données à envoyer sur les afficheurs transitent par un même bus (7 fils

dans le cas d’un afficheur 7 segments) pour l’ensemble de ces afficheurs. Ainsi le

chiffre à afficher est envoyé sur tous les afficheurs en même temps. Sans une

gestion particulière de ces afficheurs, il n’est pas possible d’écrire des nombres.

C’est pourquoi, en parallèle ce ces entrées de données, il existe une entrée de

validation pour chacun des afficheurs. Ces entrées sont souvent commandées via

des transistors pour permettre un gain de courant. Le schéma ci-dessous donne le

câblage d’un tel système (3 afficheurs 7 segments dans ce cas-là).

FIGURE 3: 3 AFFICHEURS 7 SEGMENTS

Le multiplexage de l’affichage permet de limiter le nombre de connexions pour

ces 4 afficheurs. Mais son fonctionnement exige la mise en œuvre de composants

séquentiels.

[Ecrire le nom et prénom de chaque membre du groupe ici] 6

Atelier « Circuits FPGA »

Il ne faut pas oublier d’assigner les entrées/sorties du système aux broches

réelles du système. Le système final étant déjà câblé, ces contraintes sont

prédéfinies sur le tableau 1 suivant.

TABLEAU 1: ASSIGNEMENT DES ENTRÉES / SORTIES AUX BROCHES DU SYSTÈME

Pour activer un segment (cathode), on doit placer un ’0’ (zéro) sur la sortie

correspondant au segment seg. Pour activer un afficheur, il faut également placer un

’0’ sur la sortie an désirée, (en raison de la présence d’un transistor amplificateur

inverseur).

- a.…g, dp = cathodes des segments et du point décimal de tous les afficheurs ;

- an = commandes des anodes communes des afficheurs.

Afin de développer ce module de gestion d’affichage multiplexé de manière la

plus simple possible, nous allons découper cette application en plusieurs blocs

fonctionnels que nous allons par la suite décrire en VHDL séparément :

- Un décodeur décimal à 7 segments ;

- Un diviseur de fréquence ;

- Un compteur pour le balayage des afficheurs ;

- Un multiplexeur 4 vers 1 (4 x 4 bits d’entrée).

Pour pouvoir tester ce système, des registres de stockage d’entrée seront

ajoutés.

1- Module1 : Décodeur BCD / 7 segments :

On souhaite réaliser un décodeur décimal à 7 segments utilisant un seul

afficheur (une des sorties an devra être mise à 0. On demande alors de :

[Ecrire le nom et prénom de chaque membre du groupe ici] 7

Atelier « Circuits FPGA »

- Créer un fichier source VHDL nommé BCD7seg.vhd.

- Décrire ce système en utilisant uniquement des affectations conditionnelles ou

sélectives (pas de process).

2- Module 2 : Diviseur de fréquence

La fréquence de balayage des 4 afficheurs sera fixée à 100 Hz. Il sera donc

nécessaire de disposer d’une horloge à400 Hz pour le balayage. Le diviseur de

fréquence à concevoir sera actionné par l’horloge CLK1 de la carte (50 MHz). On

demande alors de :

- Créer un fichier source VHDL nommé prediv.vhd.

- Décrire ce système en VHDL, pour passer d’une fréquence de 50 MHz à 400

Hz.

- Lancer la simulation et vérifier le bon fonctionnement de ce module.

3- Module 3 : Compteur pour le balayage

Afin de pouvoir séquentiellement sélectionner un des afficheurs, nous allons à

présent nous intéresser à un compteur synchrone. On demande alors de :

- Créer un fichier source VHDL nommé cpt.vhd.

- Décrire ce système en VHDL.

- Lancer la simulation et vérifier le bon fonctionnement de ce module.

4- Module 4 : Multiplexeur d’entrée

On souhaite pouvoir affecter à l’entrée du décodeur BCD/7segments une des

4 données présentes en entrée, afin qu’elles soient séquentiellement affichées. On

demande alors de :

- Créer un fichier source VHDL nommé muxBCD.vhd.

- Décrire ce système en VHDL.

[Ecrire le nom et prénom de chaque membre du groupe ici] 8

Atelier « Circuits FPGA »

- Lancer la simulation et vérifier le bon fonctionnement de ce module.

5- Module 5 : Décodeur 2 vers 4

On souhaite réaliser un décodeur 2 vers 4 permettant à partir du module

"compteur" de sélectionner un des 4 afficheurs 7 segments. Ces afficheurs sont

actifs à l’état bas. En considérant que les données à convertir sont fournies par 4

interrupteurs :

- Créer un fichier source VHDL nommé dec2v4.vhd.

- Décrire ce système en utilisant uniquement des affectations conditionnelles ou

sélectives (pas de process).

- Lancer la simulation et vérifier le bon fonctionnement de ce module.

6- Afficheur complet

En regroupant l’ensemble des éléments précédents, il est possible d’aboutir à

un afficheur multiplexé complet tout en réalisant une fonction de « routage» de

données : sélection d’un émetteur et d’un récepteur parmi des nombreux éléments,

en utilisant un medium unique de communication (virtuel ici). On demande alors de :

- Créer un fichier source VHDL nommé aff7seg.vhd.

- Instancier les composants nécessaires au bon fonctionnement du système

dans ce fichier source.

- Réaliser alors un afficheur multiplexé présentant un message constant

(configuré dans la source, par exemple "1984").

- Lancer la simulation et vérifier le bon fonctionnement du système d’affichage

numérique étudié.

[Ecrire le nom et prénom de chaque membre du groupe ici] 9

Atelier « Circuits FPGA »

V- Prise en main de la carte de développement FPGA

On se propose ici de reprendre en main le logiciel Xilinx ISE Webpack.

Une fois que toutes les étapes de « compilation» sont réussies, un

fichier binaire *.bit est généré et peut alors être implanté dans le FPGA.

Pour cela, il est nécessaire de relier la carte sur un des ports USB de

l’ordinateur et d’allumer la carte d’étude.

L’utilitaire Adept (Digilent) sera alors utilisé pour transférer le fichier

binaire vers le FPGA.

Attention : pour les versions supérieures à 10.1 de Xilinx ISE, afin de pouvoir

générer le fichier de programmation correctement, vous devrez ajouter la ligne : NET

"clk" CLOCK_DEDICATED_ROUTE = FALSE; dans le fichier de contraintes (*.ucf).

[Ecrire le nom et prénom de chaque membre du groupe ici] 10

Vous aimerez peut-être aussi

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Presentation FpgaDocument50 pagesPresentation FpgaBen Ahmed AbdelhamidPas encore d'évaluation

- Chap2 Circuits Logiques ProgrammablesDocument22 pagesChap2 Circuits Logiques Programmablesedon umondiPas encore d'évaluation

- Compte Rendu TP Electronique NumériqueDocument16 pagesCompte Rendu TP Electronique NumériqueEL YâssirPas encore d'évaluation

- TP FpgaDocument22 pagesTP FpgakfawazPas encore d'évaluation

- TP1 - Réseaux Et Télécmmunications - UEM 122 PDFDocument26 pagesTP1 - Réseaux Et Télécmmunications - UEM 122 PDFHermosaPas encore d'évaluation

- L'Architecture Sopc Des Fpgas: Cours Fpga 02/01/2014Document7 pagesL'Architecture Sopc Des Fpgas: Cours Fpga 02/01/2014Souha BoukadidaPas encore d'évaluation

- FpgaDocument12 pagesFpgaHamza SalloumPas encore d'évaluation

- Travaux Dirigés FPGA & VHDLDocument28 pagesTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- Travaux Dirigés FPGA & VHDL - 2Document28 pagesTravaux Dirigés FPGA & VHDL - 2simohamed1993Pas encore d'évaluation

- TP Khamlich Niosii1Document9 pagesTP Khamlich Niosii1Bilal ChPas encore d'évaluation

- Fascicule de TP FpgaDocument32 pagesFascicule de TP FpgaHichem HamdiPas encore d'évaluation

- MC Codesign 2015Document20 pagesMC Codesign 2015Mohamed Ali AbdallahPas encore d'évaluation

- TP 1 Basys 2Document12 pagesTP 1 Basys 2Lena OgbiPas encore d'évaluation

- Travaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLDocument39 pagesTravaux Pratiques: Electronique Numérique Avancée: Fpga - VHDLMį Ņā ŘěťPas encore d'évaluation

- Modelsim QuartusDocument23 pagesModelsim QuartusAli AlFiguiguiPas encore d'évaluation

- 387 2 Sin Fpga Schema 2 PDFDocument23 pages387 2 Sin Fpga Schema 2 PDFGhani LamiPas encore d'évaluation

- 3cours FpgaDocument29 pages3cours Fpgabouda sofianePas encore d'évaluation

- Cours VHDLDocument45 pagesCours VHDLSouhaib LoudaPas encore d'évaluation

- Les Circuits Logiques Programmables FPGADocument29 pagesLes Circuits Logiques Programmables FPGAOUSSAMA ELHJOUJI0% (1)

- Materiel TP Processeurs de SignauxDocument10 pagesMateriel TP Processeurs de SignauxTonprince Knight AdPas encore d'évaluation

- VHDLDocument45 pagesVHDLdrissi kaitouni zinebPas encore d'évaluation

- TP VHDL 2024Document15 pagesTP VHDL 2024aminefoura6Pas encore d'évaluation

- TP1 4 Me27Document17 pagesTP1 4 Me27Mohamed NarumohPas encore d'évaluation

- E2i3 Tp1 Cod Sopc Builder 2012Document27 pagesE2i3 Tp1 Cod Sopc Builder 2012Elbahaoui Abdel100% (1)

- Ilovepdf Merged (2) MergedDocument78 pagesIlovepdf Merged (2) MergedManissa BelaliaPas encore d'évaluation

- CHAPITRE 1 Generalité FPGADocument33 pagesCHAPITRE 1 Generalité FPGARamzi Trabelsi100% (1)

- 7 Softcore CoursDocument76 pages7 Softcore CoursAyoub DjemaciPas encore d'évaluation

- Projet Sur ASIC - CopieDocument25 pagesProjet Sur ASIC - CopieMohamed Taher Jbeli100% (3)

- DE1 SoC TP1 v18Document26 pagesDE1 SoC TP1 v18Saamson StephenPas encore d'évaluation

- Codesign Etape Nios2Document8 pagesCodesign Etape Nios2rejeb wissalPas encore d'évaluation

- Compte RebdueDocument41 pagesCompte RebduelarbiPas encore d'évaluation

- Chapitre 4 SecurDocument43 pagesChapitre 4 SecurHichem GuedriPas encore d'évaluation

- TP5 - Circuits Logiques Programmables CPLDDocument8 pagesTP5 - Circuits Logiques Programmables CPLDeya arfaouiPas encore d'évaluation

- Rapport Sur L'Application Nios2Document11 pagesRapport Sur L'Application Nios2Bilal ChPas encore d'évaluation

- Compte Rendu TP1 VHDLDocument8 pagesCompte Rendu TP1 VHDLboussaoud.oualidPas encore d'évaluation

- Cour VHDL Amami 5 - 2016 PDFDocument71 pagesCour VHDL Amami 5 - 2016 PDFmedPas encore d'évaluation

- 16 FpgaDocument11 pages16 FpgaToon ManPas encore d'évaluation

- FR Cic-310-Introduction 10904Document3 pagesFR Cic-310-Introduction 10904Youness LMPas encore d'évaluation

- TPDSP SimulinkDocument7 pagesTPDSP SimulinkNEROPas encore d'évaluation

- Chapitre 3 - Soc - Mpse1Document38 pagesChapitre 3 - Soc - Mpse1Mounira TarhouniPas encore d'évaluation

- Compte RenduDocument21 pagesCompte RenduYoussef BTS SEPas encore d'évaluation

- FPGA - ArduinoDocument8 pagesFPGA - Arduinoali azilaPas encore d'évaluation

- CHAP3 CSE ExercicesDocument63 pagesCHAP3 CSE Exercicesousleti nesreenPas encore d'évaluation

- Chapitre 3 - 3Document18 pagesChapitre 3 - 3wafa wafaPas encore d'évaluation

- Chapitre 5 VHDLDocument91 pagesChapitre 5 VHDLdhdhPas encore d'évaluation

- TP N1-Prise en Main de QuartusDocument22 pagesTP N1-Prise en Main de QuartusIlham KinichPas encore d'évaluation

- Systèmes Embarqués 2 GSTR3Document84 pagesSystèmes Embarqués 2 GSTR3Mehdi El Bakkouri100% (2)

- Carte Numerique QuartusDocument26 pagesCarte Numerique QuartusAdiouma DiopPas encore d'évaluation

- Questions Module Configuration Des FPGADocument2 pagesQuestions Module Configuration Des FPGAValentin COUTEAUPas encore d'évaluation

- GlobaleDocument81 pagesGlobaleAbir ErrajaPas encore d'évaluation

- Basys 2Document26 pagesBasys 2Hichem KhamallahPas encore d'évaluation

- Cour 1Document5 pagesCour 1Ikram Ait AbdellahPas encore d'évaluation

- Embarquer Un Processeur Dans Un FpgaDocument4 pagesEmbarquer Un Processeur Dans Un FpgaFehmi BoudabousPas encore d'évaluation

- Tp1 Con-Cir Log 2iotDocument9 pagesTp1 Con-Cir Log 2iotferielPas encore d'évaluation

- Cours VHDLDocument51 pagesCours VHDLCherry CandyPas encore d'évaluation

- SED Et AWK Le Guide Pratique Pour Les Debutants Sous LinuxD'EverandSED Et AWK Le Guide Pratique Pour Les Debutants Sous LinuxPas encore d'évaluation

- 02 TD FPGA BitStream AnnexesDocument3 pages02 TD FPGA BitStream AnnexesMariem KsontiniPas encore d'évaluation

- TP1 Dsp-Fpga S2 2021Document6 pagesTP1 Dsp-Fpga S2 2021yousraPas encore d'évaluation

- Carte Numerique QuartusDocument26 pagesCarte Numerique QuartusAdiouma DiopPas encore d'évaluation

- Cours 2 FpgaDocument33 pagesCours 2 FpgaMEMMADIPas encore d'évaluation

- 19 VHDLDocument15 pages19 VHDLAmina GhardallouPas encore d'évaluation

- Exposé FpgaDocument8 pagesExposé FpgaAllegro Presto ModeratoPas encore d'évaluation

- Chap2 3 Pla Pal GalDocument17 pagesChap2 3 Pla Pal GalMENANI ZineddinePas encore d'évaluation

- Chapitre 1 Classification Des Circuits IntégrésDocument29 pagesChapitre 1 Classification Des Circuits IntégrésHichem GuedriPas encore d'évaluation

- ModélisationDocument67 pagesModélisationAbdo Ait JaPas encore d'évaluation

- Compte Rendu Counter DecounterDocument18 pagesCompte Rendu Counter DecounterGuergour WalidPas encore d'évaluation

- Synthèse D'un Module de Cryptage RSA Sur Un Circuit de Type FPGADocument69 pagesSynthèse D'un Module de Cryptage RSA Sur Un Circuit de Type FPGAzineb benizPas encore d'évaluation

- Test TP2Document1 pageTest TP2telPas encore d'évaluation

- Rapport Projet Academique VHDLDocument30 pagesRapport Projet Academique VHDLelabbadi2002Pas encore d'évaluation

- Les Systèmes EmbarquésDocument125 pagesLes Systèmes EmbarquésAziz SaijiPas encore d'évaluation

- TP 1 Atelier MCPDocument17 pagesTP 1 Atelier MCPHa NaPas encore d'évaluation

- Projet - Tutoré FinalDocument52 pagesProjet - Tutoré Finaleya.dkhilPas encore d'évaluation

- Les Microcontrôleurs de La Famille PICDocument75 pagesLes Microcontrôleurs de La Famille PICNabil DakhliPas encore d'évaluation

- Circuits Logiques Programmables-FinalDocument145 pagesCircuits Logiques Programmables-FinalHoucem B HsnPas encore d'évaluation

- Cours FPGA Et VHDLDocument66 pagesCours FPGA Et VHDLamine menadPas encore d'évaluation

- Compte RenduDocument21 pagesCompte RenduYoussef BTS SEPas encore d'évaluation

- Chap1 CSEDocument15 pagesChap1 CSEmehdi100% (1)

- TP MUX - 4vers1Document8 pagesTP MUX - 4vers1Meriem MeriemPas encore d'évaluation

- Chapitre 1 Presentation Informatique Industrielle Systemes Micro ProgrammesDocument6 pagesChapitre 1 Presentation Informatique Industrielle Systemes Micro ProgrammesMedPas encore d'évaluation

- Etude Et Realisation D'une Horloge NumeriqueDocument38 pagesEtude Et Realisation D'une Horloge NumeriqueHon Ey100% (1)

- Electronique Numerique PDFDocument110 pagesElectronique Numerique PDFKhaireddine ZaraiPas encore d'évaluation

- Layout Avancé-Chapitre2-2Document34 pagesLayout Avancé-Chapitre2-2Hossam El KhiariPas encore d'évaluation

- InitiationDocument58 pagesInitiationAli AmaraPas encore d'évaluation

- Besoin - Labo Module DSP Et FPGADocument2 pagesBesoin - Labo Module DSP Et FPGAIbrahimFaroukSolarPas encore d'évaluation

- Circuit Logique ProgrammableDocument5 pagesCircuit Logique ProgrammablechristophePas encore d'évaluation