Académique Documents

Professionnel Documents

Culture Documents

De9codage Adresse1 Prof

Transféré par

MBADJOUN DanielTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

De9codage Adresse1 Prof

Transféré par

MBADJOUN DanielDroits d'auteur :

Formats disponibles

TD : DECODAGE D’ADRESSES

DECODAGE D’ADRESSES: TD n°1

Objectif : Au cours de ce TD, nous allons voir les notions fondamentales concernant le

décodage d’adresses:

- Quel est le but du décodage d’adresse.

- Comment est-il implémenté dans une architecture à microprocesseur.

- Comment établir un plan mémoire d’un système à microprocesseur existant.

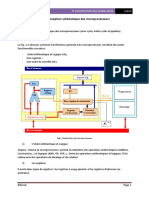

I. PRESENTATION DU SYSTEME

On considère un système à base d’un microprocesseur comprenant les divers éléments

suivants :

- Un microprocesseur 8 bits ;

- Une mémoire ROM ;

- Une mémoire RAM ;

- Un Convertisseur Analogique – Numérique (CAN) permettant de convertir

plusieurs tensions analogiques.

Le schéma simplifié du système est le suivant :

D[0..7]

A0 D0 A0 D0 A0 D0

A1 D1 A1 D1 A1 D1

A2 D2 A2 D2 A2 D2

A3 D3 A3 D3 A3 D3

A4 µP D4 A4 ROM D4 A4 RAM D4

A5 D5 A5 D5 A5 D5

A6 D6 A6 D6 A6 D6

A7 D7 A7 D7 A7 D7

A8 A8 A8

A9 A9

A10

A11

A12 CS CS

A[0..9]

A8 D0

S0

A9 D1

S1

D2

V1 D3

A10 CS_RAM

Entrées des V2 D4

A11

DECODAGE tensions V3

CAN D5

A12 CS_ROM

D’ADRESSES analogiques V4 D6

CS_CAN D7

CS

LYCEE LA FAYETTE 1/7

TD : DECODAGE D’ADRESSES

II. VOCABULAIRE ET DEFINITION

Question II.1. Calculer la capacité de la mémoire RAM en octets et en kbits.

Capacité = 29 octets = 512 octets = 4 kbits

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.2. Calculer la capacité de la mémoire ROM en ko et en kbits.

Capacité = 210 octets = 1024 octets = 1 ko = 8 kbits

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.3. Comment se nome le bus D[0..7] ?

C’est le bus de données : C’est sur ce bus que sont présentes les données lues sur les

divers circuits du système.

…………………………………………………………………………………………………

Question II.4. Comment se nome le bus A[0..7] ?

C’est le bus d’adresses : C’est sur ce bus que sont présentes les adresses permettant

d’adresser les divers circuits du système.

…………………………………………………………………………………………………

Question II.5. Que signifie le terme CS ? Sur quel état logique cette entrée est-elle valide ?

CS = Chip Select. Il permet la sélection du boîtier. Cette entrée est valide sur un état

logique bas.

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.6. Cocher la bonne réponse : Lorsque le signal CS de la RAM et de la ROM est

à l’état logique « 1 »….

Les sorties de la RAM et de la ROM sont à « 1 » ou à « 0 » suivant les

valeurs contenues dans les mémoires

Les sorties du circuit intégré sont en haute impédance « HZ »

Question II.7. Cocher la bonne réponse : Dans le cas où les signaux CS de la RAM et de la

ROM sont à l’état bas en même temps…

Il n’y a pas de conflit sur le bus de données

Il y a un conflit car les signaux D0 à D7 de ces deux composants sont

présents sur le bus de données.

LYCEE LA FAYETTE 2/7

TD : DECODAGE D’ADRESSES

Question II.8. Si on veut lire les données de la RAM, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la ROM et le CAN.

…………………………………………………………………………………………………

Question II.9. Si on veut lire les données de la ROM, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la RAM et le CAN.

…………………………………………………………………………………………………

Question II.10. Si on veut lire les données du CAN, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la RAM et la ROM.

…………………………………………………………………………………………………

Question II.11. Expliquer succinctement le rôle du décodage d’adresses dans un tel système.

Le décodage d’adresses permet de sélectionner un seul circuit parmi tous ceux présents

dans le système. Cela permet de mettre les sorties des circuits non utilisés lors de

l’adressage en haute impédance. Ainsi il n’y a pas de conflits.

…………………………………………………………………………………………………

III. FONCTIONNEMENT DU CAN

Le CAN utilisé dans ce système permet de convertir jusqu’à 4 tensions analogiques. Les

tensions analogiques à convertir sont sélectionnée à l’aide des broches S0 et S1.

La table suivante indique comment sont sélectionnées les tensions analogiques à l’entrée du

CAN :

S1 S0 Tension analogique sélectionnée

0 0 V1

0 1 V2

1 0 V3

1 1 V4

Question III.1. Compléter le tableau suivant :

A9 A8 Tensions analogique sélectionnée

0 0 V1

0 1 V2

1 0 V3

1 1 V4

LYCEE LA FAYETTE 3/7

TD : DECODAGE D’ADRESSES

IV. ETABLISSEMENT DU PLAN MEMOIRE DU SYSTEME

Afin de réaliser la fonction décodage d’adresses, on utilise un circuit 74138. Le schéma du

système est le suivant :

D[0..7]

A0 D0 A0 D0 A0 D0

A1 D1 A1 D1 A1 D1

A2 D2 A2 D2 A2 D2

A3 D3 A3 D3 A3 D3

A4 µP D4 A4 ROM D4 A4 RAM D4

A5 D5 A5 D5 A5 D5

A6 D6 A6 D6 A6 D6

A7 D7 A7 D7 A7 D7

A8 A8 A8

A9 A9

A10

A11

A12 CS CS

A[0..9]

A8 D0

S0

A9 D1

CS_ROM S1

D2

BIN/OCT V1 D3

A10 1

1 Entrées des V2 D4

A11 2

2 0

15

CS_RAM

tensions V3

CAN D5

14

A12 3 4

1

2

13 analogiques V4 D6

12

3

4

11 D7

6 & 5

10

9

6

4 EN 7

7 CS_CAN

5 CS

74LS138

DECODAGE

D’ADRESSES

La table de vérité du circuit 74138 est la suivante :

Entrées Sorties

4 2 1 0 1 2 3 4 5 6 7

0 0 0 0 1 1 1 1 1 1 1

0 0 1 1 0 1 1 1 1 1 1

0 1 0 1 1 0 1 1 1 1 1

0 1 1 1 1 1 0 1 1 1 1

1 0 0 1 1 1 1 0 1 1 1

1 0 1 1 1 1 1 1 0 1 1

1 1 0 1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 1 1 1 0

LYCEE LA FAYETTE 4/7

TD : DECODAGE D’ADRESSES

Question IV.1. Compléter le schéma structurel de la page précédente en reliant correctement

les broches 6, 4 et 5 (chacune au VCC ou à la masse) du 74138 afin de le valider.

Question IV.2. En vous aidant de la table de vérité du 74138, compléter le tableau suivant :

Adresses A[10..12] Sorties du 74138

A12 A11 A10 0 1 2 3 4 5 6 7

0 0 0 0 1 1 1 1 1 1 1

0 0 1 1 0 1 1 1 1 1 1

0 1 0 1 1 0 1 1 1 1 1

0 1 1 1 1 1 0 1 1 1 1

1 0 0 1 1 1 1 0 1 1 1

1 0 1 1 1 1 1 1 0 1 1

1 1 0 1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 1 1 1 0

Question IV.3. Quel doit être le niveau du signal CS_RAM pour sélectionner la RAM ?

Il faut CS_RAM = 0

Question IV.4. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner la RAM ?

Il faut A10=0 ; A11=0 et A12=0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.5. Quel doit être le niveau du signal CS_ROM pour sélectionner la ROM ?

Il faut CS_ROM = 0

Question IV.6. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner la ROM ?

Il faut A10 = 1 ; A11 = 0 ; A12 = 0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.7. Quel doit être le niveau du signal CS_CAN pour sélectionner le CAN ?

Il faut CS_CAN = 0.

Question IV.8. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner le CAN ?

Il faut A10 = 0 ; A11 = 1 et A12 = 0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

LYCEE LA FAYETTE 5/7

TD : DECODAGE D’ADRESSES

On rappel que le CAN permet de faire l’acquisition de 4 tensions analogiques. Les tensions

analogiques sont sélectionnées à l’aide des adresses A8 et A9.

Question IV.9. Compléter le tableau suivant décrivant les adresses hautes et basses

permettant de sélectionner les circuits RAM, ROM et CAN.

Circuit A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0 0 0 1 1 1 1 1 1 1 1 1 1

RAM

0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 1 1 1 1 1 1 1 1 1 1 1

ROM

0 0 1 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 1 1 1 1 1 1 1 1

CAN : V1

0 1 0 0 0 0 0 0 0 0 0 0 0

0 1 0 0 1 1 1 1 1 1 1 1 1

CAN : V2

0 1 0 0 1 0 0 0 0 0 0 0 0

0 1 0 1 0 1 1 1 1 1 1 1 1

CAN : V3

0 1 0 1 0 0 0 0 0 0 0 0 0

0 1 0 1 1 1 1 1 1 1 1 1 1

CAN : V4

0 1 0 1 1 0 0 0 0 0 0 0 0

Question IV.10. Déduire de la question précédente les plages d’adresses permettant la

sélection des différents circuits :

Circuit Plage d’adresses (en hexadécimal)

RAM 0000 – 03FF

ROM 0400 – 07FF

V1 0800 – 08FF

V2 0900 – 09FF

CAN

V3 0A00 – 0AFF

V4 0B00 – 0BFF

Question IV.11. Combien de ko la plage d’adresses de la ROM permet-elle d’adresser ?

0400 – 07FF = 1024 octets = 1 ko

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.12. Combien de ko la plage d’adresses de la RAM permet-elle d’adresser ?

0000 – 03FF = 1024 octets = 1 ko

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.13. En comparant la capacité de la RAM avec le nombre de ko qui peuvent être

adressés sur la RAM, donner la plage d’adresses inutilisée dans le système pour la RAM.

Adresses inutilisées par la RAM : 0200 – 03FF soit 512 octets.

…………………………………………………………………………………………………

LYCEE LA FAYETTE 6/7

TD : DECODAGE D’ADRESSES

Question IV.14. Lors du développement d’un programme permettant d’adresser les

différentes entrées analogiques du CAN, quelles adresses choisirez-vous pour adresser les

entrées V1, V2, V3 et V4 ?

V1 : 0800 V3 : 0A00

V2 : 0900 V4 : 0B00

Question IV.11. Compléter le plan mémoire ci-dessous en utilisant les adresses que vous avez

réservées pour les différentes entrées du CAN.

0BFFh

0B00h CAN : V4

0AFFh

CAN : V3 0A00h

09FFh

0900h CAN : V2

08FFh

CAN : V1 0800h

07FFh

ROM

0400h

03FFh

VIDE

0200h

01FFh

RAM

0000h

LYCEE LA FAYETTE 7/7

Vous aimerez peut-être aussi

- Adressage MemoireDocument10 pagesAdressage MemoireLibre HamataPas encore d'évaluation

- Travaux Dirigés-Microprocesseur MicrocontroleurDocument18 pagesTravaux Dirigés-Microprocesseur MicrocontroleurFatima BettayebPas encore d'évaluation

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- TD Decodage AdressesDocument10 pagesTD Decodage AdressesDhafer Mezghani100% (1)

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- TD4Document1 pageTD4Mounira Tarhouni100% (1)

- Corrigé TD 154Document3 pagesCorrigé TD 154MBADJOUN Daniel100% (1)

- Guide Moto6809Document23 pagesGuide Moto6809fatima zahra benmeriemePas encore d'évaluation

- Série 5Document3 pagesSérie 5Blidi AymenPas encore d'évaluation

- TP Moto 6809Document7 pagesTP Moto 6809gamerzxs681Pas encore d'évaluation

- TD - N°2 - EN - Systèmes À MicroprocesseurDocument7 pagesTD - N°2 - EN - Systèmes À MicroprocesseurTimble Puteur100% (2)

- TD5LAT54Document1 pageTD5LAT54Smati DjamelPas encore d'évaluation

- CorrigéExamen 2020-2021Document3 pagesCorrigéExamen 2020-2021Moujahed GassoumiPas encore d'évaluation

- Microprocesseur 6809: Présentation GénéraleDocument11 pagesMicroprocesseur 6809: Présentation GénéraleMOHAMED TAMZAITIPas encore d'évaluation

- Architecture Du Microprocesseur 6809 de MotorolaDocument14 pagesArchitecture Du Microprocesseur 6809 de MotorolaPhylipe Rodrigez100% (1)

- TD 1 Les Mémoires: 1. Partie ThéoriqueDocument2 pagesTD 1 Les Mémoires: 1. Partie ThéoriqueAla DorbozPas encore d'évaluation

- TD Les MémoireDocument4 pagesTD Les Mémoirefers100% (5)

- 1 Architecture de 8255Document10 pages1 Architecture de 8255Yogbake HansPas encore d'évaluation

- M - Microprocesseurs Et DSP-Chap2Document17 pagesM - Microprocesseurs Et DSP-Chap2MENANI ZineddinePas encore d'évaluation

- Assembleur x86Document96 pagesAssembleur x86Ibtihel MechleouiPas encore d'évaluation

- Exercices de RivisionDocument10 pagesExercices de RivisionOnsPas encore d'évaluation

- 0B4CjIMFACisHckpYZHNmY2xDTms PDFDocument4 pages0B4CjIMFACisHckpYZHNmY2xDTms PDFAbdoul Nasser Aboubacar100% (1)

- TD1 Mémoires 2021Document3 pagesTD1 Mémoires 2021Younesse El100% (2)

- TD°2: Mémoiré: Exercice 1Document2 pagesTD°2: Mémoiré: Exercice 1Mouna Ben Mohamed100% (5)

- TD1 19corrDocument5 pagesTD1 19corrSaid ReganiPas encore d'évaluation

- Série 02Document5 pagesSérie 02kal joPas encore d'évaluation

- TD3 Mémoire CorrDocument37 pagesTD3 Mémoire CorrNadia Ben NjimaPas encore d'évaluation

- TP3: Conception Schématique Des Microprocesseurs: ObjectifDocument6 pagesTP3: Conception Schématique Des Microprocesseurs: ObjectifDor SafPas encore d'évaluation

- QCM Sur Le MicroprocesseurDocument11 pagesQCM Sur Le MicroprocesseurGhislaine REMONDO100% (1)

- Correction Du td1 ArmDocument2 pagesCorrection Du td1 Armazza memmi100% (1)

- Cours Assembleur 6809Document18 pagesCours Assembleur 6809Med AmallahPas encore d'évaluation

- TD 05 CorrigeeeDocument6 pagesTD 05 CorrigeeeNadhir Mehellou100% (2)

- Ao 2 TDDocument3 pagesAo 2 TDBerbaoui KamelPas encore d'évaluation

- Les Mémoires PDFDocument11 pagesLes Mémoires PDFBazizi Wardia50% (2)

- Chapitre 5-HW SW CodesignDocument52 pagesChapitre 5-HW SW Codesignhelakaraa0% (3)

- Exercices Assembleur M1 ELT ER Serie 2 Avec CorrigéDocument5 pagesExercices Assembleur M1 ELT ER Serie 2 Avec CorrigéAmir Na DzPas encore d'évaluation

- Epreuve 1Document2 pagesEpreuve 1ChristianPas encore d'évaluation

- TD4 SLDocument5 pagesTD4 SLRomualde Nunue100% (1)

- Corrtd 1Document7 pagesCorrtd 1wafa wafaPas encore d'évaluation

- Assembleur 8086Document83 pagesAssembleur 8086Yassine Jammeli100% (1)

- Corrigé Série de TD N° 3Document5 pagesCorrigé Série de TD N° 3Alaa MessaoudPas encore d'évaluation

- Corrigé Du TD1Document3 pagesCorrigé Du TD1youssef BohaPas encore d'évaluation

- Programmation Assembleur 8086Document51 pagesProgrammation Assembleur 8086zied harchayPas encore d'évaluation

- Corrigé Devoir N°1Document3 pagesCorrigé Devoir N°1Colmain Nassiri100% (1)

- Exercice Corrigée Les Modes D'adresse (Assembleur Motorola 6809)Document3 pagesExercice Corrigée Les Modes D'adresse (Assembleur Motorola 6809)YoussefPas encore d'évaluation

- Exo Distributeur de BoissonsDocument2 pagesExo Distributeur de BoissonsMila z100% (1)

- Calcul Capacite MemoiresDocument25 pagesCalcul Capacite MemoiresAbdelmoumenAbdelmoumenPas encore d'évaluation

- TD 05 CorrigeDocument6 pagesTD 05 CorrigeAnonymous Wpl47Bwu4Pas encore d'évaluation

- Série 3 - Bis - Programmation Assembleur 8085Document3 pagesSérie 3 - Bis - Programmation Assembleur 8085Rottina RossyPas encore d'évaluation

- Simulation 6809Document5 pagesSimulation 6809Mr S.KamaliPas encore d'évaluation

- Exercices Architecture Des Processeurs Et MicroprocesseursDocument4 pagesExercices Architecture Des Processeurs Et MicroprocesseursGeorges Le Mignon Ole100% (1)

- Ecole Supérieure de Technologie de Béni Mellal Université Sultan Moulay SlimaneDocument7 pagesEcole Supérieure de Technologie de Béni Mellal Université Sultan Moulay SlimaneSimo MabrouukPas encore d'évaluation

- 15 Exercices Corrigés en Systèmes D'exploitation Et Architecture Des OrdinateursDocument11 pages15 Exercices Corrigés en Systèmes D'exploitation Et Architecture Des OrdinateursJean Baptiste SAWADOGOPas encore d'évaluation

- Rapport Fox g20Document18 pagesRapport Fox g20Omar ZemraniPas encore d'évaluation

- Chapitre I Microprocesseur 6809 GSEA12013 PDFDocument56 pagesChapitre I Microprocesseur 6809 GSEA12013 PDFRyan Hj100% (1)

- Série 01 PDFDocument4 pagesSérie 01 PDFÃčĥ ŖăfPas encore d'évaluation

- Interfaçage Du Microprocesseur 8086Document29 pagesInterfaçage Du Microprocesseur 8086Abderrazzak Riali50% (2)

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- Wa0000.Document2 pagesWa0000.Paréto BessanhPas encore d'évaluation