Académique Documents

Professionnel Documents

Culture Documents

Cours 03

Transféré par

sefeldinabdelazizTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours 03

Transféré par

sefeldinabdelazizDroits d'auteur :

Formats disponibles

Assembleur

Introduction à l’assembleur x86

Cours 03

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 2

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 3

Architecture x86 et IA-32

Architecture x86

• Les architectures x86 ont été développé par Intel de 1976 à 2003

o 8086 (8 bits) – 1e génération

o 80186 (16 bits) – 1e génération

o 80286 (16 bits) – 2e génération

o 80386 (32 bits) – 3e génération – IA-32

o 80486 (32 bits) – 4e génération – IA-32 – pipelinage et cache

o Pentium (32 bits) – 5e génération – IA-32 – Superscalaire

o Pentium Pro (32 bits) – 6e génération – IA-32 – Extension d’adresses physiques

• L’IA-32 correspond à la version 32 bits de l’architecture x86

• Intel garantit la rétrocompatibilité de ses processeurs.

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 4

Architecture x86 et IA-32

Architecture IA-32

• IA-32 pour architectures 32 bits

o Il s’agit d’une architecture abstraite

o Elle couvre les processeurs allant du 80386, jusqu’au Pentium 4…

o Elle a depuis été etendue à 64 bits: x86-64 / AMD64 (IA-64 est différent)

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 5

Architecture x86 et IA-32

Architecture IA-32

• 8 registres 32-bits directement accessibles

o eax, ebx, ecx, edx, esi, edi utilisables

o ebp souvent utilisé comme « block pointer » (variables locales)

o esp pointeur de pile (pointe sur le dernier élément empilé)

• Un registre avec les indicateurs (eflags)

o retenue, débordement, signe, etc.

• Un compteur de programme (eip; pour « instruction pointer »)

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 6

Architecture x86 et IA-32

Architecture IA-32

• 6 registres de segments (pas utilisés dans ce cours)

• Unité virgule flottante

o 8 registres de 80 bits accessibles comme une pile

o Registres de contrôle et de statut

• Unités MMX/SSE/SSE2/3D-Now …

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 7

Architecture x86 et IA-32

Architecture IA-32

• Registres « généraux » 8 bits, 16 bits et 32 bits

o EAX<31..0> eax

o AX<15..0> := EAX<31..0>

ax

o AH<7..0> := EAX<15..8>

o AL<7..0> := EAX<7..0> ah al

• Pareil pour les quatre premiers registres 31 16 15 8 7 0

o eax, ax, ah, al

o ebx, bx, bh, bl

o ecx, cx, ch, cl

o edx, dx, dh, dl

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 8

Architecture x86 et IA-32

Architecture IA-32 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

• Indicateurs (eflags) - NT IOPL OF DF IF TF SF ZF - AF - PF - CF

― CF: carry; retenue/emprunt; débordement non signé

― PF: parity; vrai si le nombre de bits à 1 est pair

― AF: auxiliary carry; pour le BCD

― ZF: zero; vrai si le résultat est zéro

― SF: sign; vrai si le résultat est négatif

― DF: direction (DF = faux → inc; DF = vrai → dec)

― OF: overflow; débordement signé

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 9

Architecture x86 et IA-32

15 0

Architecture IA-32

31 0 CS - code

EAX DS - data Registres select –

EBX SS - stack Pointeurs qui identifient un segment

dans la mémoire – non utilisés dans

ECX ES - data

EDX FS - data

ESI GS - data

EDI 31 0

EBP – block pointer EFLAGS – plusieurs flag état, un flag ctrl

ESP – stack pointer EIP – Pointeur instructions - PC

Registres usage général Registres état et contrôle

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 10

Architecture x86 et IA-32

Exercice 1:

Quelle est la différence entre x86 et IA-32?

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 11

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 12

Assembleur IA-32

Types d’instructions

Il existe trois types d’instructions

• Déplacement de données

- Registre-registre

- Registre<- mémoire

- Mémoire <- registre

• Operation arithmetiques/logiques (UAL)

- add, sub, shift, and

• Branchement

- jmp, j?, call, ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 13

Assembleur IA-32

Type de machine

IA-32 est une architecture Register-Memory

• Il est possible d’additionner un registre et une valeur en mémoire

• Il est permis de mettre le résultat de l’addition en mémoire

• Il est n’est pas permis que la source et la destination d’une addition soient en mémoire

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 14

Assembleur IA-32

Syntaxe

Il existe deux syntaxes de l’IA-32:

Intel et AT&T

Syntaxe Intel:

add eax ebx # add dst src : eax eax + ebx

Syntaxe AT&T:

add %ebx %eax # add src dst : eax eax + ebx

Dans ce cours, nous utiliserons la syntaxe AT&T pour les compilateur GNU

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 15

Assembleur IA-32

Directives pour les segments de données et instructions

# directive on est dans le segment des données

.data

val:

.word 10, -14, 30 # trois mots

# on est dans le segment des instructions)

.text

.globl main # main est publique

main:

add %ebx %eax # addition

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 16

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 17

Déclaration des données

Étiquette (label)

Étiquettes

# directive on est dans le segment données

.data

val:

.word 10, -14, 30 # trois mots

Valeurs

# on est dans le segment texte (instructions)

Type .text

.global main # main est publique

main:

add %ebx %eax # addition

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 18

Déclaration des données

Types

• Byte = 1 octet (8 bits)

• Word = 2 octets (16 bits)

• Doubleword (dword) = 4 octets (32 bits)

• Quadword (qword) = 8 octets (64 bits)

• Entiers non-signés de N bits, [0 , 2N-1]

• Entiers signées de N bits, [-2N-1 , 2N-1-1]

– En complément à 2

• Float = 4 octets (32 bits)

• Double = 8 octets (64 bits)

• Chaine de caractères

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 19

Déclaration des données

Notes sur la représentation en virgule flottante:

• Standardisé par l’IEEE: IEEE-754 r2008

• Triplet signe, exposant, mantisse: (s, e, m)

• Sauf exceptions, la valeur d’un nombre machine Xfp est donnée par la relation Xfp = (-1)s × m × 2e

• La mantisse est normalisée: 1.0 ≤ m < 2.0, i.e. m = 1.f,

• Seul f est sauvegardé

• L’exposant est signé. Le nombre signé s’obtient par un calcul de biais: e = eb - biais

• eb est sauvegardé

• eb = 0 ou eb = emax indiquent des exceptions, notamment eb = 0, f = 0 => Xfp = 0.0

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 20

Déclaration des données

Notes sur la représentation en virgule flottante: (suite)

• En simple précision: eb est web = 8 bits, f est 23 bits, biais = 127 (2web-1 - 1)

• En double précision: eb est web = 11 bits, f est 52 bits, biais = 1023 (2web-1 - 1)

• Exemples:

+2.5 est codé 0x40200000 en simple précision, 0x4004000000000000 en double précision

• Ressource en ligne:

https://gregstoll.com/~gregstoll/floattohex/

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 21

Déclaration des données

Étiquettes

• Les noms devant les « : » se nomment étiquettes

• La valeur de l’étiquette définie avec « : » est l’adresse présente

• Utilisées pour la déclaration des fonctions

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 22

Déclaration des données

Étiquettes

• Symboliques – ASCII – doivent être définies seulement une fois

.equ une_etiquette, 123 # une_etiquette = 123

• « . » est l’adresse présente

.equ une_autre, . # équivalent à « une_autre: »

• « .globl étiquette » pour la rendre publique

.globl main # main peut être appelée par l’usager

• Numériques – une chiffre entre 0 et 9

• Utilisée seulement pour référence locale

• Peuvent être redéfinies

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 23

Déclaration des données

Étiquettes

• Une étiquette est une constante

– Peut être utilisée partout où on peut entrer une valeur immédiate

– Sa valeur réelle connue à l’exécution, selon l’adresse du programme

• On ne peut pas écrire étiquette1+étiquette2, ni étiquette1*val

– étiquette1-étiquette2 est permis

– étiquette1-étiquette2 est connu à la compilation si déclarés dans le même fichier

– Il est permis d’écrire (étiquette1-étiquette2)*val

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 24

Déclaration des données

.data # espace initialisé, lisible, écrivable

# Si cet espace commence à 0x1000

unbyte: # unbyte = 0x1000

.byte 9, 8, 0b111 # M[0x1000] = 9, M[0x1001] = 8,

# M[0x1002] = 1112

unword: # unword = 0x1003

.word 1, 2, 10%3 # M16[0x1003] = 1, M16[0x1005] = 2,

# M16[0x1007] = mod(10, 3) = 1

unshort: # unshort = 0x1009

.short 0x9C, 077 # M16[0x1009] = 9C16, M16[0x100B] = 77(8)

unentier: # unentier = 0x100D

.int 52+4, unword-2 # M32[0x100D] = 56,

# M32[0x1011] = 0x1003-2 = 0x1001

.float 12.54 # M32[1015] = 12.54 en IEEE-754 sur 32-bits, soit 0x4148a3d7

.double 67.34 # M64[1019] = 67.34 en IEEE-754 sur 64-bits, soit 0x4050d5c28f5c28f6

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 25

Déclaration des données

Exercice 2:

Considérez le code suivant. En supposant que la section data débute à l’adresse

hexadécimale 0x1000, donnez le contenu des octets allant de x01000 à 0x1013.

.data # 0x1000

poly:

.qword 10, 041

mtl:

.short 1, 0xAA

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 26

Déclaration des données

Exercice 2:

Considérez le code suivant. En supposant que la section data débute à l’adresse

hexadécimale 0x1000, donnez le contenu des octets allant de x01000 à 0x1013.

.data # 0x1000

poly: 3 2 1 0

.qword 10, 041 0x1000 0x00 0x00 0x00 0x0A

mtl: 0x1004 0x00 0x00 0x00 0x00

.short 1, 0xAA

0x1008 0x00 0x00 0x00 0x21

0x100C 0x00 0x00 0x00 0x00

0x1010 0x00 0xAA 0x00 0x01

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 27

Déclaration des données

Exercice 3:

Considérez le code suivant. Donnez la valeur des étiquettes poly et mtl.

.data # 0x1000

poly:

.qword 10, 041

mtl:

.short 1, 0xAA

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 28

Déclaration des données

Exercice 3:

Considérez le code suivant. Donnez la valeur des étiquettes poly et mtl.

.data # 0x1000

poly: # 0x1000

.qword 10, 041 3 2 1 0

mtl: # 0x1010 0x1000 0x00 0x00 0x00 0x0A

.short 1, 0xAA

0x1004 0x00 0x00 0x00 0x00

0x1008 0x00 0x00 0x00 0x21

0x100C 0x00 0x00 0x00 0x00

0x1010 0x00 0xAA 0x00 0x01

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 29

Déclaration des données

Exercice 4:

Quel est le word à l’adresse a+3?

a:

.byte 0xAA, 0x22, 0x24, 0x5C, 0x6E

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 30

Déclaration des données

Exercice 4:

Quel est le word à l’adresse a+3?

a:

.byte 0xAA, 0x22, 0x24, 0x5C, 0x6E

0x6E5C

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 31

Déclaration des données

Exercice 5:

Soit le code assembleur suivant. En supposant que la section .data débute à

l’adresse hexadécimale 0x1000, donnez la valeur de taille.

.data

debut_data:

var1:

.byte 8, 9, 10, 11

var2:

.int 0x234

.word 0x5678, 256

.equ taille, fin_data – var2

fin_data:

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 32

Déclaration des données

Exercice 5:

Soit le code assembleur suivant. En supposant que la section data débute à

l’adresse hexadécimale 0x1000, donnez la valeur de taille.

3 2 1 0

.data

0x1000 0x0B 0x0A 0x09 0x08

debut_data:

var1: 0x1004 0x00 0x00 0x02 0x34

.byte 8, 9, 10, 11

0x1008 0x01 0x00 0x56 0x78

var2:

.int 0x234

.word 0x5678, 256 var1 = 0x1000,

.equ taille, fin_data – var2 var2 = 0x1004,

fin_data = 0x100C

fin_data:

taille = fin_data – var2

= 0x100C – 0x1004 = 0x8 = 8

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 33

Déclaration des données

Exercice 6:

Donnez en hexadécimal la valeur des octets aux adresses 0x1002 et 0x1006,

sachant que la section .data débute à l’adresse 0x1000.

.data # 0x1000

.float 1.5

.double 1.5

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 34

Déclaration des données

Exercice 6:

Donnez en hexadécimal la valeur des octets aux adresses 0x1002 et 0x100A,

sachant que la section .data débute à l’adresse 0x1000.

.data # 0x1000 3 2 1 0

.float 1.5 0x3FC00000

0x1000 0x3F 0xC0 0x00 0x00

.double 1.5 0x3FF8000000000000

0x1004 0x00 0x00 0x00 0x00

0x1008 0x3F 0xF8 0x00 0x00

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 35

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Boucles

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 36

Modes d’adressage

Types d’opérande

― Immédiate (constante) $12 # c = 12

― Registre %eax # R[0]

― Adressage direct 12 # M[12]

― Mémoire indexé 12(%eax, %ebx, 4) # M[12 + %eax + 4 x %ebx]

Éléments omis à 0 (k=1) 12(, %ebx, 4) # M[12 + 4 x %ebx]

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 37

Modes d’adressage

Suffixes

Les suffixes b (byte), w (word) et l (long) permettent de spécifier le type

de donnée sur lequel l’instruction agit:

addw $4, 1234 # M16[1234] M16[1234] + 4

addl $4, 1234 # M32[1234] M32[1234] + 4

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 38

Modes d’adressage

Exercice 7:

Donnez la valeur des octets aux adresses 0x1002 et 0x1006 à la fin de l’exécution

de ce programme, sachant que la section .data débute à l’adresse 0x1000.

.data # 0x1000

valeurs:

.int 0, 0, 0, 0, 0, 0, 0, 0

.text

movl $3, %eax

xorl %ebx, %ebx

movl $0x12345678, valeurs(%ebx, %eax, 2)

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 39

Modes d’adressage

Exercice 7:

Donnez la valeur des octets aux adresses 0x1002 et 0x1006 à la fin de l’exécution

de ce programme, sachant que la section .data débute à l’adresse 0x1000.

.data # 0x1000 3 2 1 0

valeurs:

0x1000 0x00 0x00 0x00 0x00

.int 0, 0, 0, 0, 0, 0, 0, 0

.text 0x1004 0x56 0x78 0x00 0x00

movl $3, %eax 0x1008 0x00 0xF8 0x12 0x34

xorl %ebx, %ebx

movl $0x12345678, valeurs(%ebx, %eax, 2)

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 40

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 41

Branchements

Types de branchement

•Sans condition: jmp quelquepart

― quelquepart est un entier/adresse/étiquette

― quelquepart peut aussi être « *opérande »

⚫ jmp *%eax # eip R[eax]

⚫ jmp *4(%eax) # eip M32[4 + R[eax]]

•Conditions: j? quelquepart

― Où ? est le nom de la condition: c, nc, z, nz, o… (voir document sur Moodle)

― Conditions sur eflags ou sur %ecx

•Appel/retour de sous-routine:

― call fonction

― ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 42

Branchements

Exemples et exercices de conditions

Comparaison: cmp y, x

― affecte eflags selon l’opération x-y

Suivant une comparaison non signée: (above/below)

jb: jump if below, CF = 1

Suivant une comparaison signée: (above/below)

jl: jump if below, SF ≠ OF

Beaucoup de redondance… Voir document en ligne.

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 43

Branchements

Structure de contrôle conditionnelle

En C: En assembleur:

if( a ) if:

b; # code pour a

else

j? partie_else

c;

# code pour b

jmp fin_du_if

partie_else:

# code pour c

fin_du_if:

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 44

Branchements

Structure de contrôle itérative

En C: En assembleur:

do{ boucle:

b; # code de b

} while(a);

# code de a

j? boucle

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 45

Branchements

Structure de contrôle itérative

En C: En assembleur:

while( a ){ jmp test_au_debut

b; boucle:

}

# code de b

test_au_debut:

# code de a

j? boucle

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 46

Branchements

Structure de contrôle itérative

En C: En assembleur:

for(a; b; c) # code de a

d; jmp test_au_debut

boucle:

Équivaut à

# code de d

a;

# code de c

while(b) {

test_au_debut:

d;

c; # code de b

} j? boucle

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 47

Plan de la séance

Architecture x86 et IA-32

Assembleur IA-32

Déclaration des données

Modes d'adressage

Branchements

Exemples et exercices

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 48

Exemples et exercices

Exemple

Exécution

Programme

.data $> ./a.out

txt: .ascii "Hello World!\n\0" Hello World!

.text

.globl main

main:

pushl $txt

call printf

addl $4, %esp

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 49

Exemples et exercices

Exemple

Programme

.data

txt: .ascii "Hello World!\n\0"

.text

Définit une chaine de caractère

.globl main

main:

pushl $txt

call printf

addl $4, %esp

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 50

Exemples et exercices

Exemple

Programme

.data

txt: .ascii "Hello World!\n\0"

.text

.globl main

main:

pushl $txt

call printf Instructions pour un appel de fonction

addl $4, %esp (voir plus loin Appels de fonctions)

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 51

Exemples et exercices

Exemple

Programme

.data

txt: .ascii "Hello World!\n\0"

.text

.globl main

main:

pushl $txt

call printf Fonction permettant d’afficher du texte à la console

addl $4, %esp

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 52

Exemples et exercices

Exemple

Programme

.data

txt: .ascii "Hello World!\n\0"

.text

.globl main

main:

pushl $txt Paramètre de la fonction:

call printf Adresse de la chaine de caractères à afficher

addl $4, %esp

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 53

Exemples et exercices

Exemple

Programme

.data

txt: .ascii "Hello World!\n\0"

.text

.globl main

main:

pushl $txt

call printf

addl $4, %esp Sert à dépiler 4 octets (voir Concept de pile)

ret Pour retirer le paramètre de la fonction de la pile

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 54

Transfert des données (petit ajout)

Instructions usuelles

mov source, destination # destination source

xchg a, b # a b : b a

lea source, destination # destination adresse de source

― « lea » pour « load effective address »

― Source doit être de type mémoire, destination de type registre 32-bits

― Donc:

lea dep(%r1,%r2,k), %rd # RTN: R[rd] dep+R[r1]+R[r2]*k

― Ex:

lea (%ebx,%ecx), %eax # RTN: R[eax] R[ebx] + R[ecx]

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 55

Transfert des données (petit ajout 2)

Instructions pour empiler et dépiler

push source # destination source

pop dest # destination source

pusha source # push tous les registres (utile pour sauvegarde de contexte)

popa dest # pop tous les registres en ordre inverse

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 56

Exemples et exercices

Exercice 8

Que fait ce programme?

.data

txt: .ascii "Hello World!\n\0"

.text

.globl main

main:

movl $3, %ebx

L1:

pushl $txt

call printf

addl $4, %esp

subl $1, %ebx

jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 57

Exemples et exercices

Exercice 8

Que fait ce programme? Exécution

.data

txt: .ascii "Hello World!\n\0"

.text

$> ./a.out

.globl main Hello World!

Hello World!

main: Hello World!

movl $3, %ebx

L1:

pushl $txt

call printf

addl $4, %esp

subl $1, %ebx

jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 58

Exemples et exercices

Exercice 9

Que fait ce programme?

.data

txt: .ascii "Hello World!\n\0"

IT : .int 3

.text

.globl main

main:

movl IT, %ebx

L1:

pushl $txt

call printf

addl $4, %esp

subl $1, %ebx

jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 59

Exemples et exercices

Exercice 9

Que fait ce programme? Exécution

.data

txt: .ascii "Hello World!\n\0"

IT : .int 3

$> ./a.out

.text Hello World!

.globl main Hello World!

main: Hello World!

movl IT, %ebx

L1:

pushl $txt

call printf

addl $4, %esp

subl $1, %ebx

jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 60

Exemples et exercices

Exercice 10

Considérez ce programme. Quel est le contenu de la mémoire à l’adresse F à la fin du programme?

.data

IT: .int 4 eax

F: .int 0, 1, 0, 0, 0, 0

.text

.globl main

main:

movl IT, %ecx ecx

movl $F, %edx

L1: IT 0x4000 4

movl (%edx), %eax

edx

F 0x4004 0

addl 4(%edx), %eax

movl %eax, 8(%edx) 0x4008 1

addl $4, %edx 0x400C 0

0x4010 0

subl $1, %ecx 0

jnz L1 0x4014

ret 0x4018 0

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 61

Exemples et exercices

Exercice 10

Considérez ce programme. Quel est le contenu de la mémoire à l’adresse F à la fin du programme?

.data

IT: .int 4

F: .int 0, 1, 0, 0, 0, 0

.text Réponse:

.globl main

main:

movl IT, %ecx

F: .int 0, 1, 1, 2, 3, 5

movl $F, %edx

L1: IT 0x4000 4

movl (%edx), %eax F 0x4004 0

addl 4(%edx), %eax

movl %eax, 8(%edx) 0x4008 1

addl $4, %edx 0x400C 1

0x4010 2

subl $1, %ecx 3

jnz L1 0x4014

ret 0x4018 5

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 62

Branchements (petit ajout 3)

Instructions spéciales: loop, loopz, loopnz

N’affectent pas les flags

loop kekpart # ecx exc – 1; if( ecx ≠ 0) eip kekpart

loopz kekpart # ecx exc – 1; if( ecx ≠ 0 ET ZF = 1 ) eip kekpart

loopnz kekpart # ecx exc – 1; if( ecx ≠ 0 ET ZF = 0 ) eip kekpart

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 63

Exemples et exercices

Exercice 11

Considérez ce programme. Récrivez-le avec l’instruction loop

.data

IT: .int 4

F: .int 0, 1, 0, 0, 0, 0

.text

.globl main

main:

movl IT, %ecx

movl $F, %edx

L1:

movl (%edx), %eax

addl 4(%edx), %eax

movl %eax, 8(%edx)

addl $4, %edx

subl $1, %ecx

jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 64

Exemples et exercices

Exercice 11

Considérez ce programme. Récrivez-le avec l’instruction loop

.data

IT: .int 4

F: .int 0, 1, 0, 0, 0, 0

.text

.globl main

main:

movl IT, %ecx

movl $F, %edx

L1:

movl (%edx), %eax

addl 4(%edx), %eax

movl %eax, 8(%edx)

addl $4, %edx

subl $1, %ecx

loop L1 jnz L1

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 65

Exemples et exercices .data

A: .int 81

B: .int 15

C: .int 0

Exercice 12 .text

.globl main

À faire à la maison. main:

movl A, %eax

Considérez le programme ci-contre. Compilez-le movl B, %edx

et tentez de comprendre ce qu’il fait. jmp Test

L1:

Que contiennent les registres %eax et %edx à la sub %edx, %eax

fin du programme? Test:

cmp %edx, %eax

Que contient l’emplacement mémoire étiqueté C

jae L1

à la fin du programme?

À quoi correspond cette valeur? movl %eax, C

movl $0, %eax

ret

Mise à jour: 2022/01/27 INF1600: Architecture des micro-ordinateurs 66

Vous aimerez peut-être aussi

- Bien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLD'EverandBien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLPas encore d'évaluation

- Cours 03Document66 pagesCours 03Rebecca Abi chahinePas encore d'évaluation

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Architecture Des Ordinateurs: Fiche de TP 1Document14 pagesArchitecture Des Ordinateurs: Fiche de TP 1buss comptePas encore d'évaluation

- TP N°1Document8 pagesTP N°1Hichem GuedriPas encore d'évaluation

- Cours Sur La Numeration-CodageDocument10 pagesCours Sur La Numeration-CodageJaouad ElPas encore d'évaluation

- Bien débuter en programmation: Formation professionnelleD'EverandBien débuter en programmation: Formation professionnellePas encore d'évaluation

- Cours 8 AssembleurDocument40 pagesCours 8 AssembleurMohammed DarouichePas encore d'évaluation

- 4.langage AssembleurDocument60 pages4.langage AssembleurAmine NafidPas encore d'évaluation

- TP 2Document9 pagesTP 2soyed mohamedPas encore d'évaluation

- Texas Instruments A Introduit Le DSP TMS32010 de Première Génération en 1982Document26 pagesTexas Instruments A Introduit Le DSP TMS32010 de Première Génération en 1982hafsaPas encore d'évaluation

- Cours 04Document53 pagesCours 04sefeldinabdelazizPas encore d'évaluation

- Solutionnaire Archi TD1Document5 pagesSolutionnaire Archi TD1Colmain Nassiri100% (1)

- Processeurs Embarques 1ppDocument66 pagesProcesseurs Embarques 1ppAhle Assenna0% (1)

- AssembleurDocument31 pagesAssembleurHajar El atmaniPas encore d'évaluation

- TD Architecture Des Ordinateurs PDFDocument17 pagesTD Architecture Des Ordinateurs PDFAhmedBoukadPas encore d'évaluation

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Architecture Des Ordinateurs: Fiche de TP 1Document15 pagesArchitecture Des Ordinateurs: Fiche de TP 1SkantPas encore d'évaluation

- Assembleur 1Document5 pagesAssembleur 1Asmaâ EL OuakiliPas encore d'évaluation

- Cours Chap2 Ci 1Document10 pagesCours Chap2 Ci 1Amir DridiPas encore d'évaluation

- 10-Architecture D'un Processeur SimpleDocument25 pages10-Architecture D'un Processeur Simplelmons saroutPas encore d'évaluation

- VHDLDocument45 pagesVHDLAmineMohamed100% (1)

- Chapitre 4 2020-2021Document64 pagesChapitre 4 2020-2021M'hamed Saadi BachirPas encore d'évaluation

- WWW - Cours Gratuit - Com Id 5447Document12 pagesWWW - Cours Gratuit - Com Id 5447Arsalan TlmPas encore d'évaluation

- Lec7 GE34Document35 pagesLec7 GE34Imane ZahiriPas encore d'évaluation

- Archi Cours5Document21 pagesArchi Cours5Hamza BadrPas encore d'évaluation

- System 1 Id 048Document8 pagesSystem 1 Id 048Kam ZegPas encore d'évaluation

- 2015 08 21 TD32 Le Microprocesseur 0708S1Document4 pages2015 08 21 TD32 Le Microprocesseur 0708S1Mēđ GouigaPas encore d'évaluation

- ArchIII Simulations SPICE 2021 2022Document45 pagesArchIII Simulations SPICE 2021 2022mehdibenkalia5Pas encore d'évaluation

- 12 Teleinformatique Notes de Cours 2Document16 pages12 Teleinformatique Notes de Cours 2Rahim Abba100% (1)

- CoursAssembleur - Chap1 Et 2Document28 pagesCoursAssembleur - Chap1 Et 2Achraf ElkhodariPas encore d'évaluation

- Lec1 ISADocument49 pagesLec1 ISAAssia BouhssiniPas encore d'évaluation

- Microprocess Eur 68000Document7 pagesMicroprocess Eur 68000N.NASRI MatlablogPas encore d'évaluation

- Conception À Microprocesseurs - ArdjaniDocument146 pagesConception À Microprocesseurs - Ardjaniamine menadPas encore d'évaluation

- 2018 2019 Exam AODocument10 pages2018 2019 Exam AOHamid ElhaouziPas encore d'évaluation

- Cours 8086 2015-1Document105 pagesCours 8086 2015-1Dilane GhomsiPas encore d'évaluation

- Step 7: Une Programmation StructuréeDocument29 pagesStep 7: Une Programmation StructuréeziedmesPas encore d'évaluation

- Chapitre 3Document49 pagesChapitre 3Hamza BeninePas encore d'évaluation

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihPas encore d'évaluation

- Architecture Des Ordinateurs - Cours IutDocument36 pagesArchitecture Des Ordinateurs - Cours Iutmass murderer63100% (5)

- 4 AssembleurDocument19 pages4 AssembleurHicham RaffakPas encore d'évaluation

- DS Archi Avancee FinalDocument4 pagesDS Archi Avancee FinalayoubPas encore d'évaluation

- Archi td2Document4 pagesArchi td2King SofPas encore d'évaluation

- Assembleur 8086Document83 pagesAssembleur 8086Yassine Jammeli100% (1)

- Chapitre 3 - 2019Document15 pagesChapitre 3 - 2019IbrahimFaroukSolarPas encore d'évaluation

- Le Microprocesseur 8086 8088Document16 pagesLe Microprocesseur 8086 8088Nassimos YalanosPas encore d'évaluation

- ADO SupportDeCours N.messaiDocument61 pagesADO SupportDeCours N.messaiSarah DerrichePas encore d'évaluation

- UntitledDocument8 pagesUntitledLamyaa MALLALPas encore d'évaluation

- Cours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Document80 pagesCours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Chapitre2 Architecture Interne PDFDocument8 pagesChapitre2 Architecture Interne PDFReda TadjeddinePas encore d'évaluation

- Cours II - AoutoulDocument90 pagesCours II - AoutoulZINEB AZPas encore d'évaluation

- Cours Pics16f877 PDFDocument113 pagesCours Pics16f877 PDFBày RémPas encore d'évaluation

- Chapitre 2Document17 pagesChapitre 2houda animationPas encore d'évaluation

- ExamenArchitectureSMI4 2018-RattrapageDocument2 pagesExamenArchitectureSMI4 2018-Rattrapagehamzaaouni79Pas encore d'évaluation

- Série Exercices TD1Document2 pagesSérie Exercices TD1Colmain Nassiri100% (2)

- Emul 8086Document24 pagesEmul 8086Lahcen SibouihPas encore d'évaluation

- Cours No 04 Etude de L'architecture Du Microprocesseur 8086Document6 pagesCours No 04 Etude de L'architecture Du Microprocesseur 8086Wassim AmamichePas encore d'évaluation

- Etude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Document6 pagesEtude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Zakaria ToualbiaPas encore d'évaluation

- v5 0615 Instructions PhotoPearls 7500 LowDocument8 pagesv5 0615 Instructions PhotoPearls 7500 LowzencubiPas encore d'évaluation

- QCM Corrig ArchOrdDocument9 pagesQCM Corrig ArchOrdramosthe05Pas encore d'évaluation

- Apprenez À Maîtriser La Commande DISKPARTDocument11 pagesApprenez À Maîtriser La Commande DISKPARTBabacarDiagoPas encore d'évaluation

- 2 Chipset BIOSDocument17 pages2 Chipset BIOSMoulay Said ErroudaniPas encore d'évaluation

- Hadil TaymaDocument10 pagesHadil Taymamabroukoussema61Pas encore d'évaluation

- ReadmeDocument28 pagesReadmeluisamarcianaPas encore d'évaluation

- Comment Réinitialiser Un Mot de Passe Administrateur Sur Windows Server 2008 R2 - Windows Password ResetDocument14 pagesComment Réinitialiser Un Mot de Passe Administrateur Sur Windows Server 2008 R2 - Windows Password ResetHenri HemlePas encore d'évaluation

- La Séquence de Démarrage D'un PCDocument12 pagesLa Séquence de Démarrage D'un PCAnge malvine Matagne tallaPas encore d'évaluation

- Le BiosDocument72 pagesLe Biosp1oniusPas encore d'évaluation

- BS DIY PricelistDocument71 pagesBS DIY PricelistHitman GroupPas encore d'évaluation

- Apostila de Montagem e Manutenção de ComputadoresDocument1 156 pagesApostila de Montagem e Manutenção de ComputadoresneubersaPas encore d'évaluation

- Aller 7 Carte MéreDocument3 pagesAller 7 Carte MéreSlimen Mohamed SadokPas encore d'évaluation

- Demarrage Dun OrdinateurDocument20 pagesDemarrage Dun OrdinateurYou Ssëf CHPas encore d'évaluation

- Réinstaller Windows 7 Proprement - Le Crabe Info - 1637965984329Document11 pagesRéinstaller Windows 7 Proprement - Le Crabe Info - 1637965984329steve memgbaPas encore d'évaluation

- Processeur IntelDocument10 pagesProcesseur IntelMili HibaPas encore d'évaluation

- EmailasdfasdfDocument15 pagesEmailasdfasdfMarcos PauloPas encore d'évaluation

- CFF2 Pamphletb PDFDocument2 pagesCFF2 Pamphletb PDFKouidriPas encore d'évaluation

- (TUTO) Installer Windows Sans Clé USB Ni DVDDocument40 pages(TUTO) Installer Windows Sans Clé USB Ni DVDtitusPas encore d'évaluation

- Tutoriel OS Sur Clé UsbDocument5 pagesTutoriel OS Sur Clé UsblelipsePas encore d'évaluation

- MicroProcesseurs Et ChipSetDocument44 pagesMicroProcesseurs Et ChipSetHachem Elyousfi0% (1)

- QCM Corrig ArchordDocument9 pagesQCM Corrig ArchordhafidciscoPas encore d'évaluation

- L'histoire de WindowsDocument4 pagesL'histoire de WindowsCedric ilungaPas encore d'évaluation

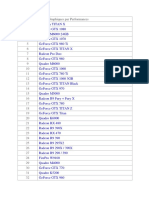

- Laptops-Dec 2020Document15 pagesLaptops-Dec 2020Nova TekPas encore d'évaluation

- Cours Sur Le Bios UefiDocument12 pagesCours Sur Le Bios UefiMohamed0% (1)

- Classement PDFDocument28 pagesClassement PDFSid Ahmed SlimanePas encore d'évaluation

- Le BIOS Et UEFIDocument12 pagesLe BIOS Et UEFIAnge malvine Matagne tallaPas encore d'évaluation

- Procedure Image de Reference MultiplateformeDocument11 pagesProcedure Image de Reference MultiplateformendarndarPas encore d'évaluation

- Comment Activer Windows 10 Avec KMSPicoDocument7 pagesComment Activer Windows 10 Avec KMSPicoYouva TristarPas encore d'évaluation

- F "Systemes PC" Niv.2Document126 pagesF "Systemes PC" Niv.2Braiek FaresPas encore d'évaluation

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Manuel de fabrication du savon: Je fabrique mes savons facilementD'EverandManuel de fabrication du savon: Je fabrique mes savons facilementÉvaluation : 5 sur 5 étoiles5/5 (4)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Gestion de projet : outils pour la vie quotidienneD'EverandGestion de projet : outils pour la vie quotidienneÉvaluation : 5 sur 5 étoiles5/5 (2)

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)

- La psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsD'EverandLa psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsPas encore d'évaluation

- Marketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxD'EverandMarketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxPas encore d'évaluation

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Le plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentD'EverandLe plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentPas encore d'évaluation