Académique Documents

Professionnel Documents

Culture Documents

Devoir Systèmes Logiques Genie Informatique2016 - 2017

Transféré par

without name0 évaluation0% ont trouvé ce document utile (0 vote)

38 vues2 pagesTitre original

Devoir Systèmes logiques genie informatique2016_2017

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

38 vues2 pagesDevoir Systèmes Logiques Genie Informatique2016 - 2017

Transféré par

without nameDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

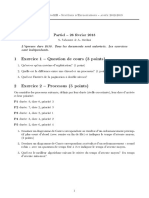

International Institute of Technology Auditoire : 1ère année GI

AU : 2016-2017 Responsable : Tarek OUNI

Devoir Systèmes logiques

Durée : 1h

Documents non autorisés

Exercice 1 : (8 pts)

1) Convertir -125 en complément à 2 sur 8 bits (1 pt)

2) Convertir 125.125 en binaire, conservez la précision. (2 pt)

3) Supposez une représentation des nombres réels utilisant 16 bits selon le format suivant

• le bit de poids fort est le bit de signe

• les 7 bits suivants représentent l’exposant, avec un biais de 63

• les 8 bits de poids faible représentent la mantisse

a) Trouvez la représentation normalisée de -25.25 (2 pt)

b) Décodez le résultat trouvé et donnez la précision. (2 pt)

c) Donnez la plus petite valeur qui puisse être codée. (1 pt)

Exercice 2 : (4 pts)

On considère le circuit logique suivant :

1) Trouver l’équation de F (A, B, C). (2 pt)

2) Simplifier l’équation de F (A, B, C). (2 pt)

3) Réaliser le circuit en utilisant uniquement des portes NAND. (2 pts)

Exercice 3 : (6 pts)

On considère le montage ci-dessous.

1) Trouver les valeurs des sorties : S0, S1, S2 et S3. (2 pts)

2) Réaliser, en utilisant un additionneur/soustracteur 4 bits (voir figure ci-dessous), un

circuit permettant, selon l’état du sélecteur, d’incrémenter ou décrémenter un nombre

non signé quelconque codé sur 3 bits (voir figure ci-dessous). Prévoir une sortie pour

le dépassement. (4 pts)

Additionneur/soustracteur 4 bits

Incrémenteur/décrémenteur qu’on souhaite réaliser

Select = 0 S = E+1

Select = 1 S = E-1

Vous aimerez peut-être aussi

- Travaux Pratiques Electronique Numérique - 2015-2016 PDFDocument16 pagesTravaux Pratiques Electronique Numérique - 2015-2016 PDFMed Tag33% (3)

- TD Systèmes Logiques PDFDocument67 pagesTD Systèmes Logiques PDFRajhiHoussem85% (13)

- TD Systèmes LogiquesDocument68 pagesTD Systèmes LogiquesRaf elaz100% (1)

- TD Systemes Logiques Circuits CombinatoiresDocument68 pagesTD Systemes Logiques Circuits CombinatoiresChouaib OujhainPas encore d'évaluation

- Correction Partiel 2013 2014Document5 pagesCorrection Partiel 2013 2014oussama bouguerra100% (1)

- Preparations Intensives Au Bts 2023: InformatiqueDocument32 pagesPreparations Intensives Au Bts 2023: InformatiqueLathifa EvinaPas encore d'évaluation

- 6 17 2015 SolutionDocument5 pages6 17 2015 SolutionFranc ZogningPas encore d'évaluation

- Examen OS 2022Document2 pagesExamen OS 2022Molka TouijinePas encore d'évaluation

- TD1 - Circuit ProgrammablebisDocument4 pagesTD1 - Circuit ProgrammablebisMouhcine Zianee100% (2)

- Examen Blanc Informatique 1Document1 pageExamen Blanc Informatique 1halim otmanePas encore d'évaluation

- Devoir Systèmes Logiques Genie Mécanique2016 - 2017corrigéDocument3 pagesDevoir Systèmes Logiques Genie Mécanique2016 - 2017corrigéwithout namePas encore d'évaluation

- Examen FinalDocument2 pagesExamen FinalKinda PrettyPas encore d'évaluation

- DSarchitectureTi2 2010Document2 pagesDSarchitectureTi2 2010imadPas encore d'évaluation

- DSarchitectureTi2 2010Document2 pagesDSarchitectureTi2 2010imadPas encore d'évaluation

- TD Systèmes Logiques-ConvertiDocument69 pagesTD Systèmes Logiques-ConvertijemaiPas encore d'évaluation

- 2012-2013 Controle Continu CorrigeDocument6 pages2012-2013 Controle Continu Corrigeaymen77Pas encore d'évaluation

- TD ElectroniqueDocument72 pagesTD ElectroniquedanielkefonPas encore d'évaluation

- CC 2010 CorrDocument3 pagesCC 2010 Corrkikikamdem0% (1)

- Serie 03Document3 pagesSerie 03hadjaissa fekharPas encore d'évaluation

- Fractionné 20231214 2147Document27 pagesFractionné 20231214 2147Black BleachPas encore d'évaluation

- TP3 Systemes LogiquesDocument2 pagesTP3 Systemes Logiquessoumaya benahmedPas encore d'évaluation

- Dokumen - Tips - TD Systemes 21Document2 pagesDokumen - Tips - TD Systemes 21Ķħ Älīl CħễħäŤäPas encore d'évaluation

- EMD0203Document11 pagesEMD0203FouadHbPas encore d'évaluation

- Correction-devoir-surveille-ASI-NOV - 2011Document4 pagesCorrection-devoir-surveille-ASI-NOV - 2011chammemPas encore d'évaluation

- 2013-2014 Cscscscsccontinu CorrigeDocument6 pages2013-2014 Cscscscsccontinu Corrigeaymen77Pas encore d'évaluation

- Emd9899 PDFDocument9 pagesEmd9899 PDFJawab 24Pas encore d'évaluation

- DS 2324 Final CorrectionDocument4 pagesDS 2324 Final Correctionghaitan00Pas encore d'évaluation

- Sujet+corrigé TEST - STRM1 - 2019 - 2020Document3 pagesSujet+corrigé TEST - STRM1 - 2019 - 2020Kaneki DZPas encore d'évaluation

- 4 5976543358565225362-1 UnlockedDocument2 pages4 5976543358565225362-1 UnlockedSegueni Oussama (سقني أسامة)Pas encore d'évaluation

- TD N°2 Systèmes LogiquesDocument2 pagesTD N°2 Systèmes LogiquesDhafer Mezghani100% (1)

- TD-3 ArchiDocument1 pageTD-3 ArchiColmain NassiriPas encore d'évaluation

- Final NFA004 2022Document2 pagesFinal NFA004 2022assaadshreim365Pas encore d'évaluation

- Circuit NumériqueDocument3 pagesCircuit NumériquePaule Evelyne Denise TjekaPas encore d'évaluation

- 1 Exercice 1 Question de Cours (4 Points) : Examen (1ère Session) 14 Avril 2014Document3 pages1 Exercice 1 Question de Cours (4 Points) : Examen (1ère Session) 14 Avril 2014BoualemDjillaliPas encore d'évaluation

- Examen Electronique 1Document3 pagesExamen Electronique 1Edouard Mvogo BileguePas encore d'évaluation

- Examen Sys Logique Iit 2016 - Principal - CorrigéDocument6 pagesExamen Sys Logique Iit 2016 - Principal - CorrigéabderrahmenPas encore d'évaluation

- Examen Session Electronique Numérique LPHE3 2022Document6 pagesExamen Session Electronique Numérique LPHE3 2022Dhafer MezghanniPas encore d'évaluation

- EFM Math 1 WWW - Forumista.tk Uploaded by Th3 Expert PDFDocument2 pagesEFM Math 1 WWW - Forumista.tk Uploaded by Th3 Expert PDFWalid MouatamidPas encore d'évaluation

- ArchitectureL1MIA2018 2019 1Document3 pagesArchitectureL1MIA2018 2019 1fetyambinintsoaPas encore d'évaluation

- Exo EnslDocument14 pagesExo EnslDhiaeddine AtiPas encore d'évaluation

- TP1 CCDocument2 pagesTP1 CCRania Ben AmmarPas encore d'évaluation

- Mat 131 TDDocument3 pagesMat 131 TDPharellePas encore d'évaluation

- CC1 en 2019Document1 pageCC1 en 2019Younesse ElPas encore d'évaluation

- TD1 Fpga 1 1 2Document6 pagesTD1 Fpga 1 1 2saviorPas encore d'évaluation

- DSP Exam 0304Document2 pagesDSP Exam 0304Norin Tchetgnia100% (1)

- Corrige 1Document15 pagesCorrige 1hatemPas encore d'évaluation

- Corrige ADODocument2 pagesCorrige ADOnadirPas encore d'évaluation

- 1 Exercice 1 Question de Cours (3 Points) : Partiel 26 Février 2013Document2 pages1 Exercice 1 Question de Cours (3 Points) : Partiel 26 Février 2013Aymen KhaledPas encore d'évaluation

- 1-Epreuve Principale Examen de Fin de Formation 2017Document5 pages1-Epreuve Principale Examen de Fin de Formation 2017Soufiane KhaliliPas encore d'évaluation

- Examen RSX101 2012 PDFDocument4 pagesExamen RSX101 2012 PDFjijiPas encore d'évaluation

- TD1 Synthèse VHDLDocument3 pagesTD1 Synthèse VHDLMohamed SdiriPas encore d'évaluation

- Vdocuments - MX - Chapitre 3 Cryptographie Symtrique ModerneDocument14 pagesVdocuments - MX - Chapitre 3 Cryptographie Symtrique ModerneSarra SamaaliPas encore d'évaluation

- Cein 2019Document3 pagesCein 2019Sergio MvomoPas encore d'évaluation

- TD 3.logique Combinatoire - BéjaiaDocument4 pagesTD 3.logique Combinatoire - BéjaiabigPas encore d'évaluation