Académique Documents

Professionnel Documents

Culture Documents

00 GL3 TD Codesign Comb Seq Avec Correction

Transféré par

Mariem KsontiniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

00 GL3 TD Codesign Comb Seq Avec Correction

Transféré par

Mariem KsontiniDroits d'auteur :

Formats disponibles

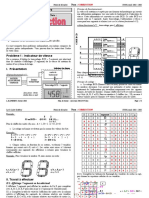

Décodeur BCD/7seg (1): Décodeur BCD/7seg (2): entity Décodeur BCD/7seg (2): architecture (cas1)

Un décodeur BCD permet d’adapter des données binaires codées sur 4 bits

architecture decarch of decbcd7seg is

(représentant les chiffres de 0 à 9) aux entrées d’un afficheur 7 segments (chaque

a begin

entrée étant connectée à un segment et permettant de l’allumer ou de l’éteindre) b

pF BCD c

WITH BCD SELECT

a

Donnée BCD

/7 d Commande segments

a e segments<=“1111110" WHEN "0000",

pF BCD b f b pf seg f “0110000" WHEN "0001",

c

g

Donnée BCD

/7 d g h

“1101101" WHEN "0010",

e c

pf seg f

“1111001" WHEN "0011",

g

e “0110011" WHEN "0100",

h d h “1011011" WHEN "0101",

Commande segments

entity decbcd7seg is “0011111" WHEN "0110",

Port ( BCD: in std_logic_vector (3 downto 0); “1110000" WHEN "0111",

Ecrire un programme VHDL permettant de modéliser le décodeur pour les deux cas: “1111111" WHEN "1000",

segments: out std_logic_vector (7 downto 0) );

• Cas1: Les segments actifs sur niveau logique haut “1110011" WHEN "1001",

end decbcd7seg;

• Cas2: Les segments actifs sur niveau logique bas “0000000" WHEN OTHERS

end decarch;

Remarque : Ne pas tenir compte du segment h

DAMERGI Emir – INSAT 2019/20 3 DAMERGI Emir – INSAT 2019/20 4 DAMERGI Emir – INSAT 2019/20 5

Décodeur BCD/7seg (3): architecture (cas 2) Encodeur de priorité (1): Encodeur de priorité (2):

architecture decarch of decbcd7seg is

begin

WITH BCD SELECT

segments<="0000001" WHEN "0000",

"1001111" WHEN "0001",

"0010010" WHEN "0010",

Un encodeur de priorité est un circuit qui donne en sortie le numéro (codé en

0 0 0 0 0 0 1 "0000110" WHEN "0011",

1 0 0 1 1 1 1 "1001100" WHEN "0100", binaire) de l’entrée active la plus prioritaire (ei étant plus prioritaire que ej pour tout i>j).

0 0 1 0 0 1 0

Question 1 : Si p=2n, déterminer le nombre de bits en sortie (la valeur de k).

"0100100" WHEN "0101",

Par exemple, si seules les entrées e5 et e8 sont à 1, la sortie (bits sk à s0) codera 8

0 0 0 0 1 1 0 "0100000" WHEN "0110",

1 0 0 1 1 0 0 "0001111" WHEN "0111", en binaire (e8 étant plus prioritaire e5).

0 1 0 0 1 0 0 "0000000" WHEN "1000", Réponse: Pour coder 2n valuers on a besoin de n bits

Question 1 : Si p=2n, déterminer le nombre de bits en sortie (la valeur de k).

1 1 0 0 0 0 0 "0000100" WHEN "1001",

p=2n k=n

0 0 0 1 1 1 1 “1111111" WHEN OTHERS Question 2 : Donner le circuit « encodeur de priorité» en VHDL pour p=8.

0 0 0 0 0 0 0 end decarch;

0 0 0 1 1 0 0

DAMERGI Emir – INSAT 2019/20 6 DAMERGI Emir – INSAT 2019/20 8 DAMERGI Emir – INSAT 2019/20 9

Encodeur de priorité (3): entity Encodeur de priorité (4): architecture -1- Encodeur de priorité (4): architecture -2-

request request Architecture encodarch of encodeur is

signal output: std_logic_vector (3 downto 0);

begin

requestnbr requestnbr

requestcode requestcode output <= ‘’1111’’ when requestnbr (7)=‘1’ else

‘’1110’’ when requestnbr (6)=‘1’ else

Question 2 : Donner le circuit « encodeur de priorité » en VHDL pour p=8.

Question 2 : Donner le circuit « encodeur de priorité » en VHDL pour p=8. ‘’1101’’ when requestnbr (5)=‘1’ else

‘’1100’’ when requestnbr (4)=‘1’ else

combinatoire signal_output <= signal1 WHEN condition1 ELSE ‘’1011’’ when requestnbr (3)=‘1’ else

entity encodeur is

signal2 WHEN condition2 ELSE ‘’1010’’ when requestnbr (2)=‘1’ else

Port (requestnbr: in std_logic_vector (7 downto 0);

Conditionnel signalN WHEN conditionN ‘’1001’’ when requestnbr (1)=‘1’ else

requestcode: out std_logic_vector (2 downto 0); ‘’1000’’ when requestnbr (0)=‘1’ else

ELSE autre_signal ; ‘’0000’’;

request : out std_logic));

Priorité request <= output(3);

end encodeur

requestcode<=output(2 downto 0);

End encodarch

request & requestcode

DAMERGI Emir – INSAT 2019/20 10 DAMERGI Emir – INSAT 2019/20 11 DAMERGI Emir – INSAT 2019/20 12

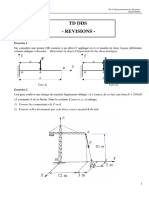

Compteur/Décompteur synchrone -1- Compteur/Décompteur synchrone -2-: entity Compteur/Décompteur synchrone -3- : architecture

• Soit le compteur/décompteur 16 bits avec commande de chargement (Figure ci-dessous). Un signal temporaire pour effectuer les ARCHITECTURE aCmpt OF Compteur IS

library ieee; traitements (peut être utilisé comme entrée SIGNAL Count: std_logic_vector(15 downto 0);

BEGIN

use ieee.std_logic_1164.all; ou sortie) contrairement au signal Counter

use ieee.std_logic_unsigned.all;

priorité Liste de sensibilité = clk, signaux asynchrones PROCESS( Clk,rst )

BEGIN

IF rst=

ENTITY Compteur IS

Ordre de traitement ( if ): ELSIF (clk'event and clk='1')

PORT (

1- Signaux Asynchrones : Rst IF load

• Les signaux Load, Inc et Dec sont synchrones. clk, rst, inc, dec , load: in std_logic; 2- Signal d’horloge (Clk)

ELSIF inc

2-x: Signaux synchrone par ordre

• Le signal de remise à zéro (Rst) est asynchrone. Load_val: in std_logic_vector (15 downto 0);

ELSIF dec

de priorité Load, inc et dec

• Tous ces signaux de contrôle sont actifs au niveau logique bas. Counter : out std_logic_vector (15 downto 0) END IF;

END IF;

Question: Donner le code VHDL pour modéliser le compteur. );

A la fin du traitement (process) la sortie Counter<=Count;

END Compteur; récupère la valeur du signal temporaire

END PROCESS;

END aCmpt;

DAMERGI Emir – INSAT 2019/20 14 DAMERGI Emir – INSAT 2019/20 15 DAMERGI Emir – INSAT 2019/20 16

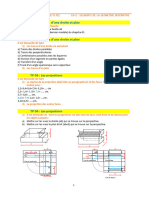

Compteur/Décompteur synchrone -4- : architecture Exercice : Registre à décalage série-parallèle Synthèse -1-

ARCHITECTURE aCmpt OF Compteur IS Il s’agit de développer un modèle structurel d’un registre N bits avec une entrée série

SIGNAL Count: std_logic_vector(15 downto 0); IF rst='0' THEN et une sortie parallèle basé sur des composants flip-flops

BEGIN Count<=(OTHERS=>'0'); - - Tous les bits à 0

PROCESS( clk,rst) ELSIF (clk'event and clk='1') then

BEGIN

IF rst= IF load = ‘0’ THEN Count <=Load_val;

ELSIF (clk'event and clk='1') ELSIF inc='0' THEN

IF load IF Count="1111" THEN

Count<="0000";

ELSIF inc Principe : à chaque front d’horloge, les bits sont décalés de la sortie d’une bascule (Q) à la suivante.

ELSE

Count <= Count + 1; La sortie de la bascule N-1 étant l’entrée du système DIN.

ELSIF dec Question : Le code VHDL utilisé vous semble-t-il être cohérent avec le

Les sorties des bascules représentant ainsi la sortie du système complet DOUT.

ELSIF dec='0' THEN fonctionnement désiré ? :

END IF;

IF Count=“0000" THEN • Entrées: Horloge CLK (1 bit), reset synchrone RST_B (1 bit) actif au niveau bas, données série DIN (1 bit). • donner le code correspondant au circuit

END IF;

Count<=“1111"; • Donner le circuit correspondant au code

Counter<=Count; ELSE • Sortie: Contenu du registre DOUT (N bits). N peut être un paramètre générique.

END PROCESS; Count <= Count - 1; Question 1 : Donner le code VHDL modélisant la bascule.

Rappel: Dans un process clocké, chaque affectation génère un flip-flop entre les parties gauche et droite de l’affectation

END aCmpt; END IF; Question 2 : Donner le code VHDL du système complet (Registre série-parallèle) en utilisant « generate »

17

DAMERGI Emir – INSAT 2019/20 DAMERGI Emir – INSAT 2019/20 DAMERGI Emir – INSAT 2019/20 21

Synthèse -2- Synthèse -3-

A

+ C

B Process(clk)

Begin

+ E If (clk’event and clk=‘1’) then

D C <=A+B;

E <=D+(A+B);

Dans un process clocké:

Chaque affectation génère un flip- End if

flop entre les parties gauche et End

droite de l’affectation

DAMERGI Emir – INSAT 2019/20 22 DAMERGI Emir – INSAT 2019/20 23

Vous aimerez peut-être aussi

- AFFICHEUR7 SEGMENTSeleveDocument5 pagesAFFICHEUR7 SEGMENTSeleveKeys ItsnamePas encore d'évaluation

- TP2 4a Afficheur SimplifieDocument5 pagesTP2 4a Afficheur Simplifiemagicien06Pas encore d'évaluation

- Schneider Electric Merlin Gerin - Catalogue - Disjoncteurs Basse Tension Antichocs Pour La Marine - Compact DB12, Codis DF12 (1977-01) - OCRDocument4 pagesSchneider Electric Merlin Gerin - Catalogue - Disjoncteurs Basse Tension Antichocs Pour La Marine - Compact DB12, Codis DF12 (1977-01) - OCRZorbanfrPas encore d'évaluation

- Convertisseurs CAN CNADocument34 pagesConvertisseurs CAN CNAAssia BouhssiniPas encore d'évaluation

- Img 0002Document2 pagesImg 0002Kouame Kouadjo SilverePas encore d'évaluation

- Dev c3Document2 pagesDev c3Rabia ZaiedPas encore d'évaluation

- Texte de L'Epreuve: 1.documents Remis Au CandidatDocument7 pagesTexte de L'Epreuve: 1.documents Remis Au Candidatgerard correa100% (1)

- TD Can CnaDocument2 pagesTD Can CnaRigelPas encore d'évaluation

- CorrectDocument8 pagesCorrectkhlifiPas encore d'évaluation

- Plan Puc 1000kva Injection HtaDocument14 pagesPlan Puc 1000kva Injection Htanabil basbousPas encore d'évaluation

- DocumentHagerReady 20240311 015257Document6 pagesDocumentHagerReady 20240311 015257Christophe BessonPas encore d'évaluation

- Exercices - DeterminantDocument2 pagesExercices - DeterminantAyoub Akouchar0% (1)

- Convertiseur Ana - NumeDocument6 pagesConvertiseur Ana - NumebouziPas encore d'évaluation

- E.222.i.101 FraDocument12 pagesE.222.i.101 FraAbdelhakszn SznPas encore d'évaluation

- 01 - Devoir de Controle N°1 - CorrectionDocument6 pages01 - Devoir de Controle N°1 - Correctionzouaghitaher76Pas encore d'évaluation

- Stabiflex FRDocument3 pagesStabiflex FRAnonymous WDTFw8EKPas encore d'évaluation

- TP 9Document2 pagesTP 9Kadri MongiPas encore d'évaluation

- Guidage en Rotation 2023-Kb-btDocument3 pagesGuidage en Rotation 2023-Kb-btsexPas encore d'évaluation

- Transistors Bipolaires en Régime DynamiqueDocument5 pagesTransistors Bipolaires en Régime DynamiqueImane lachgarPas encore d'évaluation

- DocumentHagerReady 20240311 014122Document6 pagesDocumentHagerReady 20240311 014122Christophe BessonPas encore d'évaluation

- BassDocument2 pagesBassLuis SalazarPas encore d'évaluation

- Structure ETEPDocument2 pagesStructure ETEPBassem ChebbiPas encore d'évaluation

- Ax1 Bx1 Cx1 Dx1: SKU: 337546-337557+337570-337580 (ACF) Batch NR: 2200946100Document4 pagesAx1 Bx1 Cx1 Dx1: SKU: 337546-337557+337570-337580 (ACF) Batch NR: 2200946100Mihaela NilaPas encore d'évaluation

- Codeur Decodeur MultiplexeurDocument9 pagesCodeur Decodeur MultiplexeurDame GayePas encore d'évaluation

- Poulies PDFDocument14 pagesPoulies PDFTuấn Trần100% (2)

- TD N°3Document6 pagesTD N°3nadaPas encore d'évaluation

- Les Eléments Standards PDFDocument2 pagesLes Eléments Standards PDFkhocinePas encore d'évaluation

- Qno 1Document1 pageQno 1ullas.np47Pas encore d'évaluation

- SolidsDocument4 pagesSolidskillerk5555Pas encore d'évaluation

- Exercices - VHDL Prom Pal FpgaDocument4 pagesExercices - VHDL Prom Pal FpgaMENANI ZineddinePas encore d'évaluation

- 2000 Trieuse Bouteille Corrige MecaniqueDocument8 pages2000 Trieuse Bouteille Corrige Mecaniqueadam's sermePas encore d'évaluation

- Transistors Bipolaires en Régime DynamiqueDocument13 pagesTransistors Bipolaires en Régime DynamiquemohammedPas encore d'évaluation

- DS VHDL Nov 2015 CORRDocument5 pagesDS VHDL Nov 2015 CORRHadi Ben SaïdPas encore d'évaluation

- Notice Faisceau C3 IDocument5 pagesNotice Faisceau C3 INicolas NicolasPas encore d'évaluation

- 2000 Trieuse BouteilleDocument33 pages2000 Trieuse BouteilleeliseemayombombemboPas encore d'évaluation

- DC1 3st DR 2014Document5 pagesDC1 3st DR 2014Nejib JallouliPas encore d'évaluation

- TDdds2A TDDocument12 pagesTDdds2A TDmomoPas encore d'évaluation

- Couples Coniques À Denture Droite: en Hostaform C Moulé Sous PressionDocument1 pageCouples Coniques À Denture Droite: en Hostaform C Moulé Sous Pressionfarid said errahmaniPas encore d'évaluation

- 2022-Electronique numerique-CH1Document76 pages2022-Electronique numerique-CH1Zeleph ComboPas encore d'évaluation

- Analyseur de Spectre AnalogDocument24 pagesAnalyseur de Spectre Analogelectroblida100% (1)

- CINEMATIQUE GRAPHIQUE Preparation 214 PDFDocument10 pagesCINEMATIQUE GRAPHIQUE Preparation 214 PDFYoussef RachidPas encore d'évaluation

- MIC BLANK Sample Program WriteupDocument2 pagesMIC BLANK Sample Program WriteupSarthak kadamPas encore d'évaluation

- Les Eléments StandardDocument6 pagesLes Eléments StandardMIMFS100% (1)

- dsn2 Systeme de Remplissage Correction1Document4 pagesdsn2 Systeme de Remplissage Correction1GuiliassPas encore d'évaluation

- Audio 29Document1 pageAudio 29Mária Staroňová PřevorPas encore d'évaluation

- Poster Banc Logique Combi PDFDocument1 pagePoster Banc Logique Combi PDFAllegro Presto Moderato100% (1)

- Cours Ouvrages Hydrauliques-10Document10 pagesCours Ouvrages Hydrauliques-10Issam ElmaaniPas encore d'évaluation

- Corrige Exam Theo Info 2013 Sess1Document5 pagesCorrige Exam Theo Info 2013 Sess1ziedPas encore d'évaluation

- cm4 ModesDocument42 pagescm4 ModesSalsaPas encore d'évaluation

- TP Chapt2Document4 pagesTP Chapt2Amina KhezaznaPas encore d'évaluation

- TP Chapt2Document4 pagesTP Chapt2Amina KhezaznaPas encore d'évaluation

- E.222.i.100 FraDocument12 pagesE.222.i.100 FraAbdelhakszn SznPas encore d'évaluation

- Decodeur 7 SegmentsDocument3 pagesDecodeur 7 Segmentsarnaud.michauxPas encore d'évaluation

- Rocher CanonDocument5 pagesRocher CanonTijM2Pas encore d'évaluation

- Sungha Jung - Seventh 9 (Guitar Pro)Document21 pagesSungha Jung - Seventh 9 (Guitar Pro)Vick PrzPas encore d'évaluation

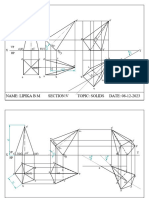

- Solids PrintDocument2 pagesSolids PrintLipika B MPas encore d'évaluation

- Page 5Document1 pagePage 5Achraf BorchaniPas encore d'évaluation

- Ch10-Les Convertisseur CAN-CNADocument13 pagesCh10-Les Convertisseur CAN-CNAAyoub ElPas encore d'évaluation

- Logique 2020Document4 pagesLogique 2020Mariem KsontiniPas encore d'évaluation

- C HéritageDocument56 pagesC Héritagemohamed bouaradaPas encore d'évaluation

- TP4 2021Document3 pagesTP4 2021Mariem KsontiniPas encore d'évaluation

- C++héritage QuizDocument12 pagesC++héritage QuizMariem KsontiniPas encore d'évaluation

- Examen ASD MPI Janvier 2020Document3 pagesExamen ASD MPI Janvier 2020Mariem KsontiniPas encore d'évaluation

- Derivation Integration Premiere PartieDocument4 pagesDerivation Integration Premiere Partieafkir hamzaPas encore d'évaluation

- Université Assane Seck de Ziguinchor UFR Sciences Et Technologies Département InformatiqueDocument3 pagesUniversité Assane Seck de Ziguinchor UFR Sciences Et Technologies Département Informatiquevy69m2rqj2Pas encore d'évaluation

- Théorie Et Codage de L Information (IF01) Exercices Paul Honeine Université de Technologie de Troyes France PDFDocument14 pagesThéorie Et Codage de L Information (IF01) Exercices Paul Honeine Université de Technologie de Troyes France PDFNanaPas encore d'évaluation

- TD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence InformatiqueDocument4 pagesTD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence Informatique4qh5xx7g6vPas encore d'évaluation

- 01 - Codage Des InformationsDocument118 pages01 - Codage Des InformationsYouness BelkhiriPas encore d'évaluation

- Id-2482Document74 pagesId-2482Rahim AbbaPas encore d'évaluation

- ESI TDG Crs 1Document61 pagesESI TDG Crs 1Safae LouahPas encore d'évaluation

- Codage CycliqueDocument29 pagesCodage CycliqueibouPas encore d'évaluation

- Compression 01 QuantificationDocument75 pagesCompression 01 QuantificationNabil SAIDANIPas encore d'évaluation

- GELE2542 Chapitre4Document28 pagesGELE2542 Chapitre4kimPas encore d'évaluation

- Chapitre-1-Les Systémes de Numérations Et CodesDocument6 pagesChapitre-1-Les Systémes de Numérations Et CodesamenmhedhbiiPas encore d'évaluation

- Analyse Syntaxique BetaDocument50 pagesAnalyse Syntaxique BetaAmine MohsniPas encore d'évaluation

- Chapitre1 IntroductionDocument16 pagesChapitre1 Introductionرضوان رضاPas encore d'évaluation

- IA1Document8 pagesIA1Fodil KhelfiPas encore d'évaluation

- MC Chapitre 2 PerceptronDocument4 pagesMC Chapitre 2 PerceptronKhalifa BakkarPas encore d'évaluation

- TP 1 PDFDocument6 pagesTP 1 PDFSarah Amk50% (2)

- La Programmation Linéaire - Cours, Exercices CorrigésDocument13 pagesLa Programmation Linéaire - Cours, Exercices CorrigésyassinePas encore d'évaluation

- Travaux Dirigés - PertDocument2 pagesTravaux Dirigés - PertYves AhlonsouPas encore d'évaluation

- Méthode D'interpolation de LagrangeDocument15 pagesMéthode D'interpolation de LagrangeNihed AttiaPas encore d'évaluation

- Exercices IaDocument4 pagesExercices IaRoufaida TradPas encore d'évaluation

- Cours3 Tris ArbresDocument57 pagesCours3 Tris ArbresDhia eddine abdelliPas encore d'évaluation

- Examen L1 Algorithme 2007 1Document2 pagesExamen L1 Algorithme 2007 1R-winPas encore d'évaluation

- 2009 2010 M43 L2 ControlesDocument45 pages2009 2010 M43 L2 ControlesBrad Jonson100% (1)

- 05 RO TG Dijkstra Ford 19 20Document19 pages05 RO TG Dijkstra Ford 19 20belfathiPas encore d'évaluation

- Série RévisionDocument9 pagesSérie RévisionMehdi SanekliPas encore d'évaluation

- Paradigme de Programare PDFDocument45 pagesParadigme de Programare PDFRada Ilie ElenaPas encore d'évaluation

- MatricesDocument4 pagesMatricesWahiba AbdounPas encore d'évaluation

- Optimisation - Chapitre 2Document10 pagesOptimisation - Chapitre 2Katia ChalalPas encore d'évaluation

- 01 Algo03 Ghazi IntroDocument13 pages01 Algo03 Ghazi IntroMillionard Junior PaulPas encore d'évaluation

- Série1 Des Travaux DirigésDocument2 pagesSérie1 Des Travaux Dirigéschihab meggPas encore d'évaluation