Académique Documents

Professionnel Documents

Culture Documents

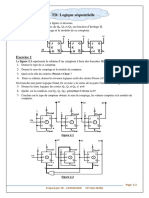

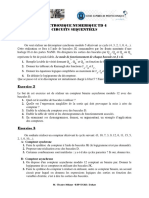

Sodapdf-Converted (1) Systemes Séquentielle

Sodapdf-Converted (1) Systemes Séquentielle

Transféré par

Mïna MaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sodapdf-Converted (1) Systemes Séquentielle

Sodapdf-Converted (1) Systemes Séquentielle

Transféré par

Mïna MaDroits d'auteur :

Formats disponibles

MINISTèRE DE L’ENSEIGNEMENT SUPÉ RIEUR

ET DE LA RECHERCHE

SCIENTIFIQUE

Institut Supérieur des Etudes

Technologiques de Nabeul

Département de Génie Electrique

Support de cours :

Systèmes Logiques (2)

Logique séquentielle

Pour les Classes de 1er année

GE

(Tronc Commun)

Elaboré par :

Ben Amara Mahmoud................................................................(Technologue)

& Gâaloul Kamel........................................................................(Technologue)

Année universitaire: 2015/2016

ISET de Nabeul Cours de Système logique (2)

TABLE DES MATIERES

Page

Chapitre1 : Logique séquentielle...........................................................................................................2

1- Objectifs.....................................................................................................................................2

2- Introduction................................................................................................................................2

3- Les Bascules asynchrones..........................................................................................................3

4- Les Bascules synchrones............................................................................................................8

Chapitre 2 : Les registres.....................................................................................................................14

1- Objectifs...................................................................................................................................14

2- Généralités................................................................................................................................14

3- Registre de mémorisation.........................................................................................................14

4- Registre à décalage...................................................................................................................15

5- Registre mixte..........................................................................................................................17

Chapitre 3 : Les Compteurs.................................................................................................................19

1- Objectifs...................................................................................................................................19

2- Introduction..............................................................................................................................19

3- Compteurs et décompteurs asynchrones..................................................................................19

4- Compteurs et décompteurs synchrones....................................................................................25

Chapitre 4 : Synthèse des compteurs..................................................................................................27

1- Objectifs...................................................................................................................................27

2- Introduction..............................................................................................................................27

3- Exemples..................................................................................................................................30

Bibliographie et Webographie.............................................................................................................39

BEN AMARA M. & GAALOUL K. Page 2 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Chapitre 1

LOGIQUE SEQUENTIELLE

1. OBJECTIFS

Traiter en détails les systèmes séquentiels.

Comprendre les bascules.

2. INTRODUCTION

2.1 Rappel sur les circuits combinatoires

Dans un système combinatoire, les sorties ne dépendent que de l’état des

entrées à un instant donné.

E1

E2 S0

Entrées E3 S1

Circuit

. S2 Sorties

combinatoire .

En . .

Sk

2.2 Les circuits séquentiels

La fonction de sortie des systèmes séquentiels dépend en plus des états des

entrées (appelées entrées primaires) des états antérieurs des sorties (appelées

entrées secondaires). On dit que le circuit séquentiel possède une fonction

mémoire.

Entrées S

E Sorties

primaires 1

Circuit

0

E .. . primaires

2 combinatoire

S

Entrées

secondaires Sorties

secondaires

Mémoire

BEN AMARA M. & GAALOUL K. Page 3 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Les systèmes séquentiels sont classes en 2 catégories :

Circuits séquentiels asynchrones

Dans les circuits séquentiels asynchrones, les sorties changent d’états dès qu’Il

y a changements des états des entrées.

Circuits séquentiels synchrones

Dans ce type de circuits les sorties changent d’états après avoir eu une

autorisation d’un signal de synchronisation appelé souvent signal « Horloge »

noté H ou CLK.

3. LES BASCULES ASYNCHRONES

La bascule est le circuit de mémorisation le plus répandu. Elle a aussi pour rôle

d’élaborer un diviseur de fréquence par deux. Elle est un système séquentiel

constitue par une ou deux entrées et deux sorties complémentaires.

E1 Q

Bascule

E2 Q

La bascule est le circuit de mémorisation le plus répandu. Elle a aussi pour rôle

d’élaborer un diviseur de fréquence par deux. Elle est un système séquentiel

constitué par une ou deux entrées et deux sorties complémentaires.

On l’appelle ainsi « bascule bistable » car elle possède deux états stables.

On distingue 4 types de bascules : RS, D, JK, et T.

3.1 Bascule RS

Symbole Explication

R Q

S Q Une impulsion sur S (set) Mise à 1 de Q

RS

(marche)

BEN AMARA M. & GAALOUL K. Page 4 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Table de vérité Equation des sorties

Entrées SortiesMode de fonctionnement Qn+1

RSQn Etat précèdent Etat

Qn+1 Qn+1 précèdent Enclenchement Maintien à 1

RS

000 0 Maintien

1 a 0 Déclenchement Interdit

Interdit Qn

001 1 0 00 01 11 10

0

010 1 0 0 1 0

1

011 1 0 1 1 0

100 0 1

101 0 1

110 - -

111 - - Qn+1=RQn+

Logigramme

A l’aide des portes NAND A l’aide des portes NOR

S

R Q

Q

R Q

S

NB : L’état R=S=1 est un état interdit puisqu’il nous donne le deux sorties

complémentaires Q et Q au même état ce qui n’est pas logique.

BEN AMARA M. & GAALOUL K. Page 5 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.2 Bascule D

Symbole Explication

D Q

D Un appui sur D Mise à 1 de Q

Q Un relâchement de D Mise à 0 de

Table de vérité Equation des sorties

Entrées Mode de fonctionnement Maintien à 0 : 0

Sorties

Qn+1

DQn Qn+1 Qn+1 Déclenchement :

Enclenchement : D

00 0 1

Qn

01 0 1 Maintien à 1 : 1 0 1

0

10 1 0 0 1

1

11 1 0 1 1

Qn+1=

Logigramme

A l’aide des portes NAND

A l’aide des portes NOR

D Q Q

Q

D

Remarque : En mettant S=D et R=D dans l’équation de la bascule RS Qon

aura Qn+1=DQn+D=D(1+Qn)=D.

BEN AMARA M. & GAALOUL K. Page 6 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Ainsi on obtient une bascule D en rajoutant un inverseur entre S et R.

D Q

RS

3.3 Bascule JK

Contrairement à la bascule RS, la condition J=K=1, ne donne pas lieu à une

condition indéterminée, mais par contre la bascule passe à l’état opposé.

Table de vérité Equation des sorties

Entrées Sorties Mode de fonctionnement

dent Etat précèdentJKQ

Maintien

nQn+1Q 0 : 0 Déclenchement : Enclenchement : Maintien à 0 : 1 Enclenchement

à n+1 Qn+1 : Déclenchemen

00001

00110 JK

01001 Qn

0 00 01 11 10

01101

1 0 0 1 1

10010

10110 1 0 0 1

11010

11101

Qn+1=JQn+KQ

J Q S Q

J

JK RS

K R

K Q Q

BEN AMARA M. & GAALOUL K. Page 7 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.4 Bascule T

La bascule T est obtenue en reliant les entrées J et K d’une bascule JK.

Table de vérité Equation des sorties

Entrées Mode de fonctionnement Maintien à 0 : 0

Sorties Qn+1

T Qn Qn+1 Qn+1 Maintien à 1 : 1 T

0 0 0 1 Enclenchement : Qn

0 1 1 0 Déclenchement : 0 0 1

1 0 1 0 1 0 1

1 1 0 1 1 0

Qn+1=TQn+TQn=TQ

Remarque : En remplaçant J et K par T dans l’équation de la bascule JK on

aura Qn+1=TQn+TQn=TQn.

T Q

Q

T

T JK

Q Q

3.5 Forçage des bascules

Certaines bascules sont équipées des entrées particulières

: Entrée de remise à 1 : PRESET (RA1),

Entrée de remise à 0 : RESET (RA0),

RA0

RA0

S

Q S Q

RS

R Q

R

Q

RA1 RA1

On applique le même résonnement pour les bascules D, T et JK.

BEN AMARA M. & GAALOUL K. Page 8 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.5.1 Table de vérité

Entrées Sorties Mode de fonctionnement

PRESETCLEAR Qn+1 Qn+1

00 Qn 0 Qn 1

01 1 0 Mémorisati

10 on Forçage

4. LES 11

BASCULES SYNCHRONES à1

Forçage à

Une bascule est synchrone quand ses sorties ne changent d’état que si un

signal supplémentaire est appliquée sur une entrée, dite entrée d’horloge

(notée H ou CLK).

H

t

4.1 Synchronisation sur niveau haut

RA0

RA0

S Q

Q S

H RSH

H

R Q

Q

R

RA1

RA1

Si H=0 : les sorties S et R sont bloquées à 1 quelques soient R et S, (les

entrées sont masquées par rapport aux sorties) la sortie garde l’état

précèdent.

Si H=1 : la bascule RS fonctionne normalement les sorties obéissent aux

entrées.

Donc la bascule RS ne fonctionne normalement que si H=1 (Niveau

Haut). Même chose pour les autres bascules.

BEN AMARA M. & GAALOUL K. Page 9 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

4.2 Synchronisation sur niveau haut

Dans le niveau bas, c’est l’inverse qui se manifeste :

Si H=1 : Q garde l’état précèdent.

Si H=0 : Fonctionnement normal de la bascule.

RA0

R

S Q

Q S

H RSH

H

R Q

Q

R

RA1

RA1

Si H=1 : les sorties S et R sont bloquées à 1 quelques soient R et S, (les

entrées sont masquées par rapport aux sorties) la sortie garde l’état

précèdent.

Si H=0 : la bascule fonctionne normalement les sorties obéissent aux

entrées.

Donc la bascule RS ne fonctionne normalement que si H=0 (Niveau

bas). La bascule synchrone est identique à celle asynchrone.

Même chose pour les autres bascules.

Remarque :

Ce type de synchronisation (sur niveau) a beaucoup d’inconvénients : la

bascule est sensible aux entrées pendant toute la durée de l’état de l’horloge

pour niveau haut (ou 0 pour le niveau bas). Si, pendant que H =1 (ou H=0), des

parasites apparaissent sur les entrées S et R, ils peuvent entrainer des

changements d’état imprévus sur la sortie Q.

Afin de minimiser au maximum la durée de cet état sensible, on s’arrange pour

que la bascule reste dans son état mémoire sauf pendant un bref instant, juste

au moment où l’entrée passe de 0 à 1 (ou de 1 à 0).

La bascule est dite synchronisée sur front.

BEN AMARA M. & GAALOUL K. Page 10 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

4.3 Synchronisation sur front

Une variable logique S peut avoir deux niveaux : le niveau haut (Vrai) ou le

niveau logique bas (Faux). Quand elle passe du niveau bas vers le niveau haut,

elle définit le front montant. Dans le cas contraire, elle définit le front

descendant.

1 1

S S

0 0

t t

Front montant Front descendant

Symbole :

Front montant Front descendant

H Q 1 H Q

1

H Q H Q

0 t 0 t

4.4 Principe de fonctionnement d’une bascule JK synchronisée sur front montant

Table de fonctionnement Symbole

Entrées Sorties Mode de fonctionnement

H J K Qn+1 Qn+1

0 x x xx0x xQn

0 Qn Qn Qn

Etat précèdent Etat précèdent Etat précèdent Etat précèdent Déclenchement : Enclenchement :

1 0 1 JHK Q

changement d’état

1 0 JK

1 1 Qn Qn Q

Qn 0 Qn 1

1 0

Qn Qn

BEN AMARA M. & GAALOUL K. Page 11 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Chronogramme :

H

1

0

t

J

1

0

t

K

1

0

t

Q

1

0

t

4.5 Bascule JK maitre esclave

4.5.1 Synchronisation sur Front montant

Preset

Qm Je Qe

Jm

H

Km JKm Qm Ke JKe Qe

Clear

Les deux bascules fonctionnent normalement si PRESET=CLEAR=1 et si H=1

la première bascule fonctionne normalement alors que la deuxième est bloquée

et quand H=0 la première bascule est bloquée alors que la deuxième fonctionne

normalement et le deux bascules ne fonctionnent ensemble qu’au moment de

passage de H de 1 à 0 c’est-à-dire au moment du front descendant ().

BEN AMARA M. & GAALOUL K. Page 12 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Donc toute bascule maitre esclave dont la maitre travaille sur le niveau haut et

l’esclave travaille sur le niveau bas est une bascule synchronisée sur front

descendant. P

J Q

H JK

K Q

C

4.5.2 Synchronisation sur Front montant

Preset

Qm Je Qe

Jm

H

Km JKm Qm Ke JKe Qe

Clear

Les deux bascules fonctionnent normalement si PRESET=CLEAR=1 et si H=0

la première bascule fonctionne normalement alors que la deuxième est bloquée

et quand H=1 la première bascule est bloquée alors que la deuxième

fonctionne normalement et le deux bascules ne fonctionnent ensemble qu’au

moment de passage de H de 0 à 1 c’est-à-dire au moment du front montant ().

Donc toute bascule maitre esclave dont la maitre travaille sur le niveau bas et

l’esclave travaille sur le niveau haut est une bascule synchronisée sur front

montant.

P

J Q

H JK

K Q

BEN AMARA M. & GAALOUL K. Page 13 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

4.5.3 Exercice

Soit le montage suivant :

P

D Q

D

H

Q

C

Compléter le chronogramme de D et Q. en déduire la fonction ainsi réalisée.

H

1

0

t

D

1

0 t

Q

1 t

4.6 Résumé

0

Synchronisation sur niveau

Synchronisation

haut sur niveau

Synchronisation

Bas sur front montant

Synchronisation sur front descendan

P P P P

J Q J Q JHK Q JHK Q

HK JK HK JK JK JK

Q Q Q Q

C C C C

BEN AMARA M. & GAALOUL K. Page 14 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Chapitre 2

LES REGISTRES

1. OBJECTIFS

Etudier les différents types de registre

Connaitre le principe de fonctionnement de chaque type.

2. GENERALITES

Un registre est un ensemble de cellules mémoire de base.

Les données peuvent être écrites/lues en même temps (parallèle) ou une

après l’autre (série).

Le nombre de bits du registre correspond au nombre de cellules mémoire

(nombre de bascule D ou JK) du registre.

On note que toutes les entrées d’horloge (H) des cellules sont reliées (ligne

d’écriture).

Les registres sont classées par :

Le nombre de bits.

Le mode de fonctionnement (unique ou multiple).

La classification des modes de fonctionnement est la suivante :

Des registres à entrées parallèles et sorties parallèles : PIPO (Parallel IN-

Parallel OUT).

Des registres à entrées parallèles et sorties séries : PISO (Parallel IN-Serial

OUT).

Des registres à entrées séries et sorties parallèles : SIPO (Serial IN- Parallel

OUT).

Des registres à entrées séries et sorties séries : SISO (Serial IN- Serial

OUT).

3. REGISTRE DE MEMORISATION (Registre parallèle)

Un registre de mémorisation (ou registre de données) est un registre dans

lequel les différents étages sont indépendants les uns des autres, cependant

certains signaux agissent sur l’ensemble des étages ; tel que remise à 0 et

remise à 1.

BEN AMARA M. & GAALOUL K. Page 15 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.1 Registre de mémorisation 4 bits

D D D D

P

D D D D

Q Q Q Q

Q Q Q Q

H C

Q0 Q1 Q2 Q3

Dans l’exemple ci-dessous, les 4 bascules sont chargées en parallèle et lues en

parallèle en synchrone avec le signal d’écriture H. Ce type de registre est

appelé aussi registre PIPO.

3.2 Schéma fonctionnel d’un registre PIPO.

E0 E1 E2 En-1

…

H

PIPO

Clear

…

S0 S1 S2 Sn

4. REGISTRE A DECALAGE (Registre série)

Ce type de registre est principalement utilisé comme mémoire d’information

dynamique ; la fonction de décalage consiste de faire glisser l’information de

chaque cellule élémentaire dans une autre cellule élémentaire adjacente.

Ce type de registre est appelé aussi registre SISO.

BEN AMARA M. & GAALOUL K. Page 16 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

4.1 Schéma fonctionnel

E

H SISO

Clear

S

4.2 Décalage a droite

La bascule du rang i doit recopier la sortie de la bascule du rang (i-1) ainsi son

D0Q0 D1Q1 D2Q2 D3Q3

entrée doit être connectée à la sortie (i-1).

D D D D

E Q

Q Q Q Q

H C

4.3 Décalage à gauche S

L’entrée de la bascule du rang i doit recopier la sortie de la bascule du rang

(i+1).

E

S

D0Q0 D1Q1 D2Q2 D3Q3

D D D D

Q0Q1Q2Q3

4.4 Décalage réversible

Il existe des registres à décalage réversibles, c’est à dire des registres ou le

décalage s’effectue vers la droite et vers la gauche en fonction du niveau

logique applique à l’entrée S : « sens de décalage ».

BEN AMARA M. & GAALOUL K. Page 17 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Q0 I0

Mux D0Q0 Mux D1Q1 Mux D2Q2 Mux D3Q3

D D D DQ3

Q Q Q Q

C

H

S

En fonction de la valeur de l’entrée S, on a l’opération suivante :

S Opération

0

1 Décalage à gauche

Décalage à droite

5. REGISTRE MIXTE

On peut trouver des registres mixtes, donc on peut écrire en parallèle et

lire en série (PISO), ou vice versa (PISO), ou qui offrent les deux

possibilités « au choix ».

5.1 Registre PISO E0 E1 E2 En-1

…

H

PISO

Clear

S

5.1.1 Logigramme en utilisant des bascules D

BEN AMARA M. & GAALOUL K. Page 18 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

I0 I1 I2 I3

Q3

D0Q0D1Q1D2Q2 D3Q3

DDD D

Q0 Q1 Q2 Q3

C

H S

BEN AMARA M. & GAALOUL K. Page 19 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

5.2 Registre SIPO

E

H SIPO

Clear

…

S0 S1 S2 Sn-1

Logigramme en utilisant des bascules D

E=D0

D0Q0 D1Q1 D2Q2 D3Q3

D D D D

Q0 Q1 Q2 Q3

C

H

Q Q Q Q3

5.3 Exemple d’application

Deux types de registres (PISO et SIPO) sont utilisés dans les liaisons séries ;

ils forment la base des modems. Par exemple, si on veut transmettre une

information entre deux ordinateurs distants de quelques dizaines de mètres.

Transmettre l’information en parallèle nécessite beaucoup de fils et très

couteux. La solution est alors d’utiliser un registre PISO pour envoyer les bits

sur une seule ligne. Au bout de laquelle, un registre SIPO reçoit ces bits et

reconstitue des octets qui sont transmis à l’ordinateur de destination.

BEN AMARA M. & GAALOUL K. Page 20 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Chapitre 3

LES COMPTEURS

1. OBJECTIFS

Etudier les différents types de compteurs.

Comprendre le principe de fonctionnement de chaque type.

Maitriser les étapes de synthèse d’un compteur.

2. INTRODUCTION

Dans des nombreuses applications on est amené à faire de comptage :

comptage d’impulsions dans un temps donné pour la mesure de fréquence par

exemple. Dans un cas il est nécessaire de compter dans d’autre il faut

décompter à partir de zéro ou d’un autre nombre donné. Un compteur, au sens

large de terme, sera susceptible de fonctionner en compteur proprement dit

(up counter) ou encore en décompteur (down counter) et dans lequel on

pourra introduire un nombre de départ quelconque c’est-à-dire que l’on peut

initialiser ou charger (load).

On peut classer les compteurs selon leur principe comme suit :

Compteurs-décompteurs asynchrones.

Compteurs-décompteurs synchrones.

L’élément de base des compteurs est une bascule à entrée d’horloge (bascule

synchrone), soit de type D, T ou JK.

3. COMPTEURS ET DECOMPTEURS ASYNCHRONES :

Le terme asynchrone signifie que les évènements ne possèdent aucune relation

temporelle entre eux. Les bascules formant un compteur asynchrone ne changent

pas d’état en même temps, car elles ne sont pas reliées au même signal d’horloge,

le déclanchement périodique uniquement sur la première bascule du compteur. Le

déclanchement des bascules suivantes se fait de proche en proche de sorte que la

sortie Qn ou Qn sera appliquée à l’horloge Hn+1 selon que l’on travaille sur front

montant ou front descendant et selon que l’on veut obtenir un compteur ou

décompteur.

Ce type de compteur étant généralement d’une réalisation simple et présente

l’inconvénient de générer des aléas de fonctionnement (retard de propagation).

BEN AMARA M. & GAALOUL K. Page 21 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.1 Les compteurs asynchrones

20 21 22 23

1 J0Q0 1 J1 Q1 1 J2Q2 1 J3Q3

H0 H1 H2 H3

1 K0 Q0 1 K1 Q1 1 K2 Q2 1 K3 Q3

Q0

1

0 t

Q1

1

0 t

Q2

1

0 t

Q3

1

0 t

0000000100100011010001010110011110001001101010111100

0123456789101112

On obtient donc un Compteur asynchrone modulo 16.

On peut réaliser le même compteur en utilisant des bascules synchronisées

sur front montant dont l’horloge Hi sera reliée à la sortie Qi-1.

BEN AMARA M. & GAALOUL K. Page 22 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.2 Les décompteurs asynchrones

20 21 22 23

1 J0Q0 1 J1 Q1 1 J2Q2 1 J3Q3

H0 H1 H2 H3

1 K0 Q0 1 K1 Q1 1 K2 Q2 1 K3 Q3

Q0

1

0

t

Q1

1

0 t

Q2

1

0 t

Q3

1

0 t

0000111111101101110010111010100110000111011001010100

0151413121110987654

On obtient donc un Décompteur asynchrone modulo 16.

On peut réaliser le même compteur en utilisant des bascules synchronisées

sur front montant dont l’horloge Hi sera reliée à la sortie Qi-1.

BEN AMARA M. & GAALOUL K. Page 23 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.3 Séquence tronquée :

Le modulo est le nombre d’état distincts occupés par un compteur avant son

recyclage à l’état initial. Le nombre maximal d’états possibles, ou modulo

maximal, d’un compteur est égal à 2n, ou n représente le nombre des bascules

dans le compteur.

On peut construire des compteurs pour obtenir une séquence dont le nombre

d’états est inférieur au 2n. La séquence est alors appelée une séquence

tronquée.

Pour obtenir une séquence tronquée, il faut forcer le recyclage du compteur

avant que ce dernier n’ait occupe tous les états. On doit disposer des bascules

munies des entrées de prédisposition remise à 0 RA0 (connu aussi RESET).

Exemple d’un compteur modulo 10 (compteur à décade)

2 2 2 2

1 1 1 1

J0 Q0 J1 Q1 J2Q2 H2 J3Q3

1 1 1 1

H0 K0 H1 H3

Q0 K1 Q1 K2 Q2 K3 Q3

C C C C

3.4 Utilisation d’autres bascules :

On peut utiliser d’autres types de bascules pour réaliser les compteurs/décompteurs

asynchrones :

3.4.1 Bascule T : 1 T Q

H Q

BEN AMARA M. & GAALOUL K. Page 24 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Ce type des bascules changent d’états à chaque Qn+1

impulsion d’horloge, si l’entrée T=1 donc on peut T

construire des compteurs/décompteurs asynchrones Qn

0 0 1

à base des bascules T en utilisant le montage ci- 1 0 1

dessous. 1 0

2 2 2 23

T0 Q0 T1Q1 T2Q2 T3Q3

1 1 1 1

H0Q0 H1Q1 H2Q2 H3Q3

C C C C

3.4.2 Bascule D :

1 DQ

H Q

Ce type des bascules changent d’états à chaque Qn+1

impulsion d’horloge. L’enclenchement est réalisé si D

D=1 et le déclenchement est réalisé si l’entrée D=0 Qn

0 0 1

donc si on relie D à Q, on obtient un changement 1 0 1

d’état à chaque impulsion d’horloge. On peut 0 1

construire des compteurs/décompteurs asynchrones

à base des bascules D en utilisant le montage ci-

dessous :

BEN AMARA M. & GAALOUL K. Page 25 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

2 2 2 23

D0 Q0 D1 Q1 D2 Q2 D3 Q3

1 1 1 1

H0Q0 H1Q1 H2Q2 H3Q3

C C C C

3.5 Compteur intégré 7493 :

Le circuit intégré 74LS93 est un exemple de compteur asynchrone. Il est

constitué d’une bascule et d’un compteur asynchrone 3 bits. Il comporte des

entrées de remise à zéro branchées à une porte NAND, désignées R0(1) et

R0(2). Quand ces deux entrées sont au niveau HAUT, le compteur est initialisé à

0000.

3.5.1 Diagramme logique :

(12) Q0 (9) Q1 (8) Q2 (11) Q3

Clock A (1)

J0 Q0 J1 Q1 J2 Q2 J3 Q3

Clock B

(14) H0 H1 H2 H3

K0 Q0 K1 Q1 K2 Q2 K3 Q3

R0(1)

(2) RAZ RAZ RAZ RAZ

(3)

R0(2)

3.5.2 Exemples d’utilisation du compteur 74LS93 :

Clock A Clock B Clock A Clock B

) )

74LS93 74LS93

R0(1) R0(1)

Compteur modulo 16 Compteur à décade

R0(2 R0(2

Q0 Q1 Q2 Q3 Q0 Q1 Q2 Q3

BEN AMARA M. & GAALOUL K. Page 26 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.6 Retard de propagation :

Les compteurs asynchrones sont souvent appelés compteurs à propagation

parce que l’effet de l’impulsion d’horloge n’est d’abord ressenti que par la

première bascule. Cet effet ne peut atteindre la bascule suivante immédiatement

à cause du retard de propagation de la première bascule. Cet effet est cumulatif

de telle sorte qu’une impulsion du signal d’horloge se propage à travers le

compteur durant un certain temps avant d’atteindre la dernière bascule, à cause

de retard de propagation.

Le retard de propagation associé aux compteurs asynchrones s est un des

désavantages majeur pour ce type des compteurs car il limite la fréquence

d’utilisation. Le retard de propagation pour une bascule est de l’ordre de 5 ns

c’est pour cela qu’il faut utiliser des fréquences inferieures à 200 MHz.

4. COMPTEURS ET DECOMPTEURS SYNCHRONES :

Le terme synchrone fait référence à des évènements qui possèdent une relation

temporelle fixe l’un par rapport à l’autre. En termes de fonctionnement d’un

compteur, le mot synchrone désigne que toutes les bascules du compteur sont

synchronisées sur le même signal d’horloge. Le problème de retard de

propagation est ainsi résolu.

Les bascules sont associées entre elles, de telle manière pour la bascule du

rang i on applique toutes les sorties des bascules qui la précède aux entrées J

et K.

4.1 Les compteurs synchrones

2 2 2 23

J0Q0 J1Q1 J2Q2 J3Q3

1

H0 H1 H2 K2 Q2 H3

1 K0 Q0 K1 Q1 K3 Q3

BEN AMARA M. & GAALOUL K. Page 27 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Q0

1

0 t

Q1

1

0 t

Q2

1

0 t

Q3

1

0 t

0000000100100011010001010110011110001001101010111100

0123456789101112

On obtient donc un Compteur synchrone modulo 16.

On peut réaliser le même compteur en utilisant des bascules synchronisées

sur front montant et les sorties Qi à la place de Qi.

4.2 Les décompteurs synchrones

20 21 22 23

1 J0Q0 J1Q1 J2Q2 J3Q3

H0 H1 H2 K2 Q2 H3

1 K0 Q0 K1 Q1 K3 Q3

BEN AMARA M. & GAALOUL K. Page 28 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Q0

1

0

t

Q1

1

0 t

Q2

1

0 t

Q3

1

0 t

0000111111101101110010111010100110000111011001010100

0151413121110987654

On obtient donc un Décompteur synchrone modulo 16.

On peut réaliser le même décompteur en utilisant des bascules

synchronisées sur front montant et les sorties Qi à la place de Qi.

BEN AMARA M. & GAALOUL K. Page 29 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Chapitre 4

SYNTHESE DES COMPTEURS SYNCHRONES

1. OBJECTIFS.

Comprendre la synthèse des compteurs synchrones.

Comprendre la synthèse des décompteurs synchrones.

2. INTRODUCTION

A chaque impulsion d’horloge, cette dernière subit une transition. Il existe quatre

transitions possibles qui peuvent être respectées par une table de transitions ou

par un graphe des états.

Sorties

Transition Description Notation

Qn Qn+1 0

0 0 0

Maintien à 0 Enclenchement Déclenchement Maintien à 1

1 0 1

1 0

2 1

3 1 1

Table des transitions

1

0 0 1

Graphe des états

Le tableau ci-dessous donne une récapitulation des transitions pour les

différentes bascules :

Bascule JKBascule RS Bascule DBascule T DT

Transition Notation 00

J K S R

0 0 11

0

0 1 1 01

0

D’après le 1tableau ci-dessus

on peut

1 conclure

0 que si on

10 veut utiliser :

1

2 0 0

1

3

BEN AMARA M. & GAALOUL K. Page 30 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Des bascules JK

On regroupe obligatoirement les enclenchements () et

facultativement les déclanchements () et les maintiens à 1 (1)

pour les équations des J.

On regroupe obligatoirement les déclenchements () et

facultativement les enclenchements () et les maintiens à 0 (0)

pour les équations des K.

Des bascules RS

On regroupe obligatoirement les

enclenchements () et

facultativement les maintiens à 1 (1) pour les équations des S.

On regroupe obligatoirement les

déclenchements () et

facultativement les maintiens à 0 (0) pour les équations des R.

Des bascules D

On regroupe obligatoirement les enclenchements () et les

maintiens à1 (1) pour les équations des D.

Des bascules T

On regroupe obligatoirement les enclenchements () et les

déclanchements () pour les équations des T.

3. EXEMPLES

3.1 Exemple 1 : compteur modulo 12

On veut réaliser un compteur modulo 12 en utilisant des bascules JK, RS et T

Solution

Pour concevoir ce compteur, il faut déterminer le nombre des bascules puis les

équations pour chaque entrée.

Avec 3 bascules on peut réaliser 23=8 combinaisons et avec 4 bascules on peut

réaliser 24=16 combinaisons et un compteur modulo 12 nécessite donc

4 bascules puisque le nombre 2n qui est le premier plus grand ou égal à 12 est

16.

BEN AMARA M. & GAALOUL K. Page 31 A.U. 2015/2016

0 0 0 1 0 0 1 0

0 0 1 0 0 0 1 1

0 0 1 1 0 1 0 0

ISET de Nabeul 0 1 0 0 0 1 0 Cours1 de Système logique (2)

0 1 0 1 0 1 1 0

0 1 1 0 0 1 1 1

0 1 1 1 1 0 0 0

Table de vérité 1 0 0 0 1 0 0 1

1 0 0 1 1 0 1 0

1 0 1 0 1 0 1 1

1 0 1 1 0 0 0 0

0 0 0 0 0 0 0 1

0

1

On peut la présenter aussi par le tableau de KARNAUGH ci-dessous :

2

3

4

5

6Séquences Bascule Q0

Q3 Q2 Q1 Q0 7 Q3 Q2 Q1 Q0

Q1Q000 Q1QQ 001 1Q0 11

Q3Q2 8 Q3Q201Q3Q211Q3Q210 3Q2Q

00 Q3Q201Q3Q211Q3Q210

Q1Q010

Q1Q0000001 9 01011001

Q1Q0010010 1 01101010

0 10000000

Q1Q0 110100 1 01111011

Q1Q0100011

Bascule JK J0=K0=1

Bascule RS R0=Q0; S0=Q0

Bascule T T0=1

BEN AMARA M. & GAALOUL K. Page 32 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Bascule Q1

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

00 11

1Q 0 Q 3Q201Q3Q211Q3Q210

Q1Q010

0 00 Bascule JK : J1=K1=Q0

Bascule RS : R1=Q1Q0 ; S1=Q1Q0

1 11 Bascule T : T1=Q0

Bascule Q2

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11

Q3Q201Q3Q211Q3Q210

Q1Q010

0 10 Bascule JK : J2= Q3Q1Q0 ; K2=Q1Q0

0 10

0 Bascule RS : R2=Q3Q2Q1Q0 ;

0 10 S2=Q1Q0

Bascule T : T2= Q3Q1Q0

Bascule Q3

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001 00

3Q2Q 1Q0 11

Q3Q201Q3Q211Q3Q210 Bascule JK : J3= Q2Q1Q0

Q1Q010

0 01 K3=Q1Q0

0 01

0 Bascule RS : R3=Q2Q1Q0

0 01 S3=Q3Q1Q0

Bascule T : T3= Q1Q0(Q3+Q2)

BEN AMARA M. & GAALOUL K. Page 33 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Réalisation à l’aide des bascules T

2 2 2 23

T0 Q0 T1Q1 T2Q2 T3Q3

1

H0Q0 H1Q1 H2Q2 H3Q3

Remarque :

Après la synthèse du compteur synchrone, il faut vérifier si ce compteur est

autocorrectif ou non c’est-à-dire que si par accident quelconque on se trouve

dans une combinaison des sorties qui est hors cycle il faut vérifier que ce

compteur peut revenir au cycle après quelques impulsions.

Par exemple pour le compteur précèdent :

1011 0000 1100

1010 0001 1101

1001 0010 1110

1000 0011 1111

0111 0100

Séquence hors

0110 0101 cycle

Cycle normal du compteur

Du compteur modulo 12

BEN AMARA M. & GAALOUL K. Page 34 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

3.2 Exemple 2 : compteur décompteur modulo 16

On veut réaliser un compteur/décompteur modulo 16 en utilisant des bascules

JK. Le changement du mode de fonctionnement est assure à l’aide d’une

entrée de commande A (si A=0 : mode comptage ; si A=1 : mode décomptage)

Solution

Pour concevoir ce compteur, il faut 4 bascules on peut réaliser 24=16

combinaisons. On va utiliser le théorème d’expansion de CHANNON pour

n’utiliser que 4 variables

Table de vérité du comptage (A=0)

Etat précèdent Etat suivant

Transition

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

0 0 0 0 0 0 0 0 1

1 0 0 0 1 0 0 1 0

2 0 0 1 0 0 0 1 1

3 0 0 1 1 0 1 0 0

4 0 1 0 0 0 1 0 1

5 0 1 0 1 0 1 1 0

6 0 1 1 0 0 1 1 1

7 0 1 1 1 1 0 0 0

8 1 0 0 0 1 0 0 1

9 1 0 0 1 1 0 1 0

10 1 0 1 0 1 0 1 1

11 1 0 1 1 1 1 0 0

12 1 1 0 0 1 1 0 1

13 1 1 0 1 1 1 1 0

14 1 1 1 0 1 1 1 1

15 1 1 1 1 0 0 0 0

BEN AMARA M. & GAALOUL K. Page 35 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

On peut la présenter aussi par le tableau de KARNAUGH ci-dessous

Séquences Bascule Q0

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11

Q3Q201Q3Q211Q3Q210 Q1Q000 Q1QQ

001

3Q2Q

001Q0 11

Q3Q201Q3Q211Q3Q210

Q1Q010 Q1Q010

0001 010111011001

0010 011011101010

0100 100000001100

0011 011111111011

Bascule 0 :J0=K0=1

Bascule Q1

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11 Q3Q201Q3Q211Q3Q210

Q1Q010

0 000

Bascule 1 : J =K =Q

1 1 0

1 111

Bascule Q2

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11

Q3Q201Q3Q211Q3Q210

Q1Q010

0 110

0 110 Bascule 2 : J2=Q1Q0 ;

0 110 K2=Q1Q0

BEN AMARA M. & GAALOUL K. Page 36 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Bascule Q3

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11

Q3Q201Q3Q211Q3Q210

Q1Q010

0 011 Bascule 3 : J = Q Q Q

3 2 1 0

0 011

K=Q QQ

0 1 3 2 1 0

0 011

Table de vérité du décomptage (A=1)

Etat précèdent Etat suivant

Transition

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

0 0 0 0 0 1 1 1 1

1 0 0 0 1 1 1 1 0

2 0 0 1 0 1 1 0 1

3 0 0 1 1 1 1 0 0

4 0 1 0 0 1 0 1 1

5 0 1 0 1 1 0 1 0

6 0 1 1 0 1 0 0 1

7 0 1 1 1 1 0 0 0

8 1 0 0 0 0 1 1 1

9 1 0 0 1 0 1 1 0

10 1 0 1 0 0 1 0 1

11 1 0 1 1 0 1 0 0

12 1 1 0 0 0 0 1 1

13 1 1 0 1 0 0 1 0

14 1 1 1 0 0 0 0 1

15 1 1 1 1 0 0 0 0

BEN AMARA M. & GAALOUL K. Page 37 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

On peut la présenter aussi par le tableau de KARNAUGH ci-dessous

Séquences Bascule Q0

Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001 00

3Q2Q 1Q0 11

Q3Q201Q3Q211Q3Q210 Q1Q000 Q1QQ

001 00

3Q2Q 1Q0 11

Q3Q201Q3Q211Q3Q210

Q1Q010 Q1Q010

1111 001110110111

0000 010011001000

0010 011011101010

0001 010111011001

Bascule 0 :J0=K0=1

Bascule Q1

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11 Q3Q201Q3Q211Q3Q210

Q1Q010

Bascule 1 : J1=K1=Q0

0 000

1 111

Bascule Q2

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001

3Q2Q

001Q0 11 Q3Q201Q3Q211Q3Q210

Q1Q010

Bascule 2 : J2=Q1Q0 ;

0 110

K2=Q1Q0

0 110

0 110

BEN AMARA M. & GAALOUL K. Page 38 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Bascule Q3

Q3 Q2 Q1 Q0

Q1Q000 Q1QQ

001 00

3Q2Q 1Q0 11 Q3Q201Q3Q211Q3Q210

Q1Q010

01 Bascule 3 : J3= Q2Q1Q0

0 011

0 011 K3= Q2Q1Q0

0 011

Equations finales

Bascule 0 : J0=K0=A.1+A.1=1

Bascule 1 : J1=K1=AQ0+AQ0

Bascule 2 : J2=K2=AQ1Q0+AQ1Q0

Bascule 3 : J2=K2=AQ2Q1Q0+A Q2Q1Q0

2 2 2 23

J0 Q0 J1Q1 H1 J2Q2 H2 J3 Q3

1

H0 K1 K2 H3

K0 K3

1 Q1

Q0 Q2 Q3

BEN AMARA M. & GAALOUL K. Page 39 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

BIBLIOGRAPHIE et WEBOGRAPHIE

Bibliographie:

❶ Titre : Circuits Numériques Théorie et Applications.

Auteur : Ronald J.Tocci.

Editeur : Reynald Goulet inc.

Année : 1996.

ISBN : 2-89377-108-4.

❷ Titre : Cours et Problèmes d’Electronique Numérique.

Auteur : Jean-Claude Laffont, Jean-Paul Vabre.

Editeur : Edition Marketing.

Année : 1986.

ISBN : 2-7298-8650-8.

❸ Titre : Logique Combinatoire et Technologie.

Auteurs : Marcel Gindre, Denis Roux.

Editeur : BELIN.

Année : 1984.

ISBN : 2-7011-0857-8.

❹ Titre : Systèmes Numériques.

Auteurs : Jaccob Millman, Arvin Grabel .

Editeur : McGRAW-HILL.

Année : 1989.

ISBN : 2-7042-1182-5.

❺ Titre : Electronique Numérique.

Auteurs : Rached Tourki .

Editeur : Centre de publication Universitaire.

Année : 2005.

ISBN : 9973-37-019-8.

❻ Titre : Support de cours de Systèmes Logiques.

Auteurs : Mohamed Habib BOUJMIL.

Année : 2004/2005.

❼ Titre : Support Pédagogique de Systèmes Logiques.

Auteurs : Fedia DOUIRI.

Année : 2011/2012.

BEN AMARA M. & GAALOUL K. Page 40 A.U. 2015/2016

ISET de Nabeul Cours de Système logique (2)

Sites Web :

http://didier.villers.free.fr/STI-2D/tronc-commun-activites.htm

http://pageperso.lif.univ-mrs.fr/~severine.fratani/enseignement/lib/exe/fetch.php?media=archi:td4-

seq.pdf

http://users.polytech.unice.fr/~fmuller/doc/ens/Peip2-SujetTP.pdf

http://ensa-mecatronique.e-monsite.com/medias/files/compteurs-cor.pdf

http://sebastien.bernard.free.fr/cours-tp-td-exo/TD-E-Logique-sequentielle-Fonction-Comptage.pdf

http://ressource.electron.free.fr/cours/Exercice_de_logique_sequentielle.pdf

BEN AMARA M. & GAALOUL K. Page 41 A.U. 2015/2016

Vous aimerez peut-être aussi

- PLD Proteus PDFDocument19 pagesPLD Proteus PDFSalah DAHOUATHIPas encore d'évaluation

- TP1 MatLabDocument4 pagesTP1 MatLabSidahmed LarbaouiPas encore d'évaluation

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabD'EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabPas encore d'évaluation

- Devoir 2 Palier 1 Infor 1term 1ere College - 2Document2 pagesDevoir 2 Palier 1 Infor 1term 1ere College - 2Ismail MaghPas encore d'évaluation

- Chap 4 Les Circuits SequentielsDocument17 pagesChap 4 Les Circuits SequentielsKycelle Mbouzeko100% (1)

- Cours TransformationZDocument12 pagesCours TransformationZbetaga100% (1)

- INF3500NotesDeCoursv2 5 PDFDocument188 pagesINF3500NotesDeCoursv2 5 PDFREDA SAADALLAHPas encore d'évaluation

- Book 1Document15 pagesBook 1Hossam EddinPas encore d'évaluation

- Traitement Du Signal S5: Décomposition en Série de Fourier Des Signaux PériodiquesDocument51 pagesTraitement Du Signal S5: Décomposition en Série de Fourier Des Signaux PériodiquesMohamed Aly SowPas encore d'évaluation

- Reponse Des Systemes Numeriques Freddy MudryDocument35 pagesReponse Des Systemes Numeriques Freddy MudryHerve DerouleauxPas encore d'évaluation

- Tp4 Transformation Fourier Echantillonage Signaux AnalogiquesDocument7 pagesTp4 Transformation Fourier Echantillonage Signaux AnalogiquesHamza BadrPas encore d'évaluation

- Cours Electronique Numerique 1Document41 pagesCours Electronique Numerique 1Bertrand Tueno YangwaPas encore d'évaluation

- Chapitre 4 SLDocument12 pagesChapitre 4 SLHENSCHEL ShadracPas encore d'évaluation

- M19 - Logique CombinatoireDocument136 pagesM19 - Logique CombinatoireCoolmanPas encore d'évaluation

- TD Bascules CompteursDocument3 pagesTD Bascules Compteursسكينة مريم100% (1)

- Td1+solution PDFDocument10 pagesTd1+solution PDFIslam BenanibaPas encore d'évaluation

- Logique Combinatoire Unité ATC 1STE Bouchaib MAHBABDocument35 pagesLogique Combinatoire Unité ATC 1STE Bouchaib MAHBABAymen Hssaini100% (3)

- hcs12 PDFDocument65 pageshcs12 PDFachraf_djyPas encore d'évaluation

- Circuit IntegresDocument7 pagesCircuit IntegresAbd OUPas encore d'évaluation

- A2-2 UalDocument3 pagesA2-2 UalLabossef LabossefchedlyPas encore d'évaluation

- Algobox Initiation PDFDocument5 pagesAlgobox Initiation PDFChokriSadek100% (1)

- AlgebrebooleDocument79 pagesAlgebrebooleEl Amrani LailaPas encore d'évaluation

- Maths Ind 1Document2 pagesMaths Ind 1Stessy Loko100% (1)

- Exercice Corrigé Transformation de Fourier PDFDocument24 pagesExercice Corrigé Transformation de Fourier PDFArsène KekpenaPas encore d'évaluation

- Chapitre 3 Filtrage Signaux Deterministes Temps ContinuDocument7 pagesChapitre 3 Filtrage Signaux Deterministes Temps Continuarbaoui11Pas encore d'évaluation

- Poly Electronik EeaDocument90 pagesPoly Electronik Eeaelmehdy elwardyPas encore d'évaluation

- Correction TD Electronique NumériqueDocument65 pagesCorrection TD Electronique NumériqueOussama Eljaafari100% (1)

- Cours E Simulation D Un Pic Sous ProteusDocument4 pagesCours E Simulation D Un Pic Sous ProteusHerve DerouleauxPas encore d'évaluation

- TP 3Document5 pagesTP 3Hajar TouilPas encore d'évaluation

- Partie-2-Microprocesseur + MemoireDocument14 pagesPartie-2-Microprocesseur + MemoireyaoPas encore d'évaluation

- Simplification Des Fonctions Logique A L BisDocument8 pagesSimplification Des Fonctions Logique A L BishamzaPas encore d'évaluation

- EdeB TD4 1 2020Document2 pagesEdeB TD4 1 2020Arsene SohPas encore d'évaluation

- Tous Au Niveau3Document203 pagesTous Au Niveau3tonye joel100% (1)

- TD 4Document4 pagesTD 4Mohammed BabaPas encore d'évaluation

- Epreuve BTS SE 2007Document13 pagesEpreuve BTS SE 2007Riham abPas encore d'évaluation

- ElectroniqueNumerique PDFDocument90 pagesElectroniqueNumerique PDFfekielyesPas encore d'évaluation

- Cours FPGA Et VHDLDocument66 pagesCours FPGA Et VHDLamine menadPas encore d'évaluation

- TD4 Electronique Numérique DIC1Document3 pagesTD4 Electronique Numérique DIC1Jacques GregoirePas encore d'évaluation

- Codage Et Information-Prof (Version Finale)Document143 pagesCodage Et Information-Prof (Version Finale)scar lightPas encore d'évaluation

- 5BTC Hyper Part2 09Document60 pages5BTC Hyper Part2 09Yàs SîñéPas encore d'évaluation

- Architecture Des Systèmes À ProcesseursDocument63 pagesArchitecture Des Systèmes À Processeurstarik marrakech100% (1)

- Filtres Du Second OrdreDocument4 pagesFiltres Du Second OrdreEmmanuel AkedPas encore d'évaluation

- Cours Electronique Numerique-3Document76 pagesCours Electronique Numerique-3koukihamedPas encore d'évaluation

- Automatique Lineaire Asservissement Regulation PDFDocument55 pagesAutomatique Lineaire Asservissement Regulation PDFMohamed Benrahal100% (1)

- Chapitre 5 Etude Des Signaux Deterministe Temps DiscretDocument17 pagesChapitre 5 Etude Des Signaux Deterministe Temps Discretarbaoui11100% (1)

- TD-Exceptionnel (Corrigé)Document7 pagesTD-Exceptionnel (Corrigé)Dr. Chekir AmiraPas encore d'évaluation

- TD Corrigé ARCHI 1Document8 pagesTD Corrigé ARCHI 1Dhafer MezghaniPas encore d'évaluation

- TD EP Redresseurs MonophasãsDocument10 pagesTD EP Redresseurs MonophasãsAyman AlharabiPas encore d'évaluation

- Chapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1Document12 pagesChapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1mohamed ben slimanePas encore d'évaluation

- Methode de Compression Codage SourceDocument29 pagesMethode de Compression Codage SourceJuba HamichePas encore d'évaluation

- Ele119 Eprm Cours TP PDFDocument368 pagesEle119 Eprm Cours TP PDFIbrahim IbrahimPas encore d'évaluation

- Traitement Du SignalDocument120 pagesTraitement Du SignalMonji Zaidi0% (1)

- Transformée en Z PDFDocument9 pagesTransformée en Z PDFAchraf BoutalPas encore d'évaluation

- Introduction Circuits Logiques Programmables - Presentation 2010Document38 pagesIntroduction Circuits Logiques Programmables - Presentation 2010fieea100% (2)

- TD LogiqueDocument22 pagesTD LogiqueLabelle AmmounaPas encore d'évaluation

- Apprendre et enseigner sur le Web: quelle ingénierie pédagogique?D'EverandApprendre et enseigner sur le Web: quelle ingénierie pédagogique?Pas encore d'évaluation

- MAITRISER Python : De l'Apprentissage aux Projets ProfessionnelsD'EverandMAITRISER Python : De l'Apprentissage aux Projets ProfessionnelsPas encore d'évaluation

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesD'EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesPas encore d'évaluation

- Notice TSMS4314873 AADocument2 pagesNotice TSMS4314873 AAxaloxaloPas encore d'évaluation

- TX-SR603 FrEs 0426Document184 pagesTX-SR603 FrEs 0426Jorge MartinPas encore d'évaluation

- Cours Résumé Sur Les Timers Du PIC (PIC18F252 Et Autres)Document9 pagesCours Résumé Sur Les Timers Du PIC (PIC18F252 Et Autres)barbarePas encore d'évaluation

- PDF LogicseqDocument25 pagesPDF LogicseqYassine FalahPas encore d'évaluation

- Semaines Du Commerce Local - Octobre 2018 - LiègeDocument40 pagesSemaines Du Commerce Local - Octobre 2018 - Liègesam_pirotonPas encore d'évaluation

- 100 French Words and Phrases For Making Phone Calls in FrenchDocument4 pages100 French Words and Phrases For Making Phone Calls in FrenchVravinski TeresaPas encore d'évaluation

- Type 4 Type 3Document4 pagesType 4 Type 3ABELWALIDPas encore d'évaluation

- A.I.L. - Corrige - Quelques Exercices Ampli OpérationnelsDocument4 pagesA.I.L. - Corrige - Quelques Exercices Ampli OpérationnelsFranco FrancoPas encore d'évaluation

- Aide Memoire CssDocument1 pageAide Memoire CssModeste AkaffouPas encore d'évaluation

- Insertion de Documents Déjà Finalisés Dans E-SidocDocument5 pagesInsertion de Documents Déjà Finalisés Dans E-SidocpmommessinPas encore d'évaluation

- TPAutomatiqueDocument15 pagesTPAutomatiqueIsmail ElouargaPas encore d'évaluation

- Đề thi thử DELF B2Document9 pagesĐề thi thử DELF B2diemthanhvuPas encore d'évaluation

- Dossier Devoir TelephoneDocument5 pagesDossier Devoir Telephonecaro34400Pas encore d'évaluation

- 7619 3elev Dossierressourcesshark 1 PDFDocument9 pages7619 3elev Dossierressourcesshark 1 PDFmabroukPas encore d'évaluation

- Efm M9 Techniques de Programmation StructureeDocument2 pagesEfm M9 Techniques de Programmation Structureeapi-26420184100% (4)

- TD1Document2 pagesTD1minzo9479Pas encore d'évaluation

- Hack Et Astuce Pour Top Eleven TAfA lAfA ChargeurDocument2 pagesHack Et Astuce Pour Top Eleven TAfA lAfA Chargeurglamorousicon2111Pas encore d'évaluation

- Wa0040Document4 pagesWa0040Master Sherif100% (1)

- OFDM RapportDocument23 pagesOFDM RapportAyoub Hammouga100% (1)

- Masquè Dè SaisièDocument1 pageMasquè Dè SaisièKael LasriPas encore d'évaluation

- Bo Et BFDocument4 pagesBo Et BFAbdallah BelabbesPas encore d'évaluation

- CompteurDocument2 pagesCompteurBrahamChaoucheFethallahYacinePas encore d'évaluation

- Grandjeu MissionagentsecretDocument22 pagesGrandjeu MissionagentsecretdupontPas encore d'évaluation

- Télécom Examen 2018 2Document1 pageTélécom Examen 2018 2zakiPas encore d'évaluation

- Exercices Sur La Modulation D'amplitudeDocument4 pagesExercices Sur La Modulation D'amplitudeZH Hamza100% (4)

- Cours 3A Modulation AMDocument54 pagesCours 3A Modulation AMDON DEVATTI67% (3)

- Notice Installation Recepteur Lumiere Io On-OffDocument20 pagesNotice Installation Recepteur Lumiere Io On-OffsudicePas encore d'évaluation

- DVB TDocument18 pagesDVB TCàmilià MounichPas encore d'évaluation