Académique Documents

Professionnel Documents

Culture Documents

TD Micropro Islape 2023

Transféré par

Fotcha EricTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD Micropro Islape 2023

Transféré par

Fotcha EricDroits d'auteur :

Formats disponibles

DEPARTEMENT DE GENIE ELECTRIQUE

FILIERE : GENIE ELECTRIQUE

Filière/Niveau : IIA/2 ANNEE ACADEMIQUE 2023-2024

TD2: MICROPROCESSEURS ET DOMOTIQUE2

Exercice 1:

Exercice 2:

Exercice 3:

Reprendre les questions de l’exercice 2 pour les feux tricolores

Enseignant : Eric Fotcha 1

PROLEME1 : COMMANDE PAR MICROPROCESSEUR

On désire commander le processus décrit dans cet automatisme par un système bâti autour du

microprocesseur 6809 de MOTOROLA.

La figure 2 représente un système à microprocesseur 8 bits dont les plages d’adresse sont données ainsi

qu’il suit :

Pour La ROM : 4000 à 5FFFH Pour la RAM2 : 6000H à 7FFFH

Pour la RAM1 : 0000H à 1FFFH Pour le PIA : E000H à E003H

1 Quelle est en Ko la capacité maximale d’adressage du système ? (2 pts)

2 Donner en Ko les capacités de stockage des mémoires ROM, RAM1, RAM2 et le nombre de

registre du PIA. (4 pts)

Après l’analyse des plages d’adresses, on désire apporter des précisions sur la nature du décodeur

d’adresses.

3 Déterminer le nombre de bits d’entrée du décodeur et les bits d’adresses concernées (2 pts)

4 Dresser la table de vérité en précisant les boitiers sélectionnés. (2 pts)

5 Sachant que la ROM est constituée des modules mémoires 4K × 4 nécessaires pour former la

ROM

On désire installer un boitier supplémentaire RAM3 de capacité 4Ko pour augmenter la capacité mémoire

du système. Sachant que l’adresse de la 1ère case de la RAM3 est 8000H

5-1 Déterminer l’adresse de la dernière case mémoire de la RAM3 (2 pts)

5-2 Déterminer la sortie du décodeur qui permet de sélectionner la RAM3 (0,5 pts)

6 Le grafcet point de vue commande (figure 1) ci-dessous décrit le fonctionnement d’un autre système

automatisé dont on voudrait réaliser la programmation par un système à microprocesseur conçu autour du

microprocesseur 6809 et le PIA 6821.

6-1) proposer une affectation des entrées du PIA 6821 nécessaire à la programmation de ce

grafcet (figure 1) 1,5pts

6-2) proposer un organigramme de ce système (2 pts)

6-3) en déduire un programme de commande de ce processus (figure 1) en langage assembleur

(4pts)

Enseignant : Eric Fotcha 2

Figure 1 : grafcet

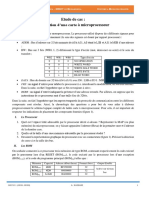

µP Bus d’adresses: 16 bits (A0 à A15)

ROM RAM RAM PIA

Décodeur

D’adresses

1 2

CS CS CS CS

Bus de données : 8 bits (D0 à D7)

Figure.2 : Système à µP

Enseignant : Eric Fotcha 3

PROLEME2 :COMMANDE PAR MICROPROCESSEUR

On envisage à présent piloter ce systeme de tri de pièces par couleur grâce à un système à

microprocesseur constitué de :

- Un microprocesseur 6809 (16 adresses)

- D’un décodeur 1 parmi 8

- Des puces mémoires (RAM et ROM)

- Un circuit d’interface 6821

1) Que signifie l’expression microprocesseur 32 bits ? 1pt

2) Déterminer est la capacité d’adressage de ce microprocesseur(en Kilos octets) sachant que le bus

de données est de 8 bits ? (2 pts)

3) A partir des portes ‘’ET‘’ et des portes inverseuses, on veut réaliser un décodeur 1 parmi 8 utiliser

pour sélectionner les différents circuits intégrés mémoire de ce système à microprocesseur.

a) Déterminer le nombre d’entrées et le nombre de circuits intégré mémoires que ce décodeur

peut sélectionner ? justifier votre réponse. (2 pts)

b) Dresser la table de vérité ainsi que le schéma de câblage de ce décodeur (3 pts)

c) Sachant que trois fils sont soustraits du bus d’adresse pour piloter le décodeur, quel sera le

nombre maximal d’adresse d’un circuit intégré mémoire ? (2 pts)

d) Indiquer l’adresse de début définie en hexadécimal de chaque puce mémoires

(3 pts)

4) Le grafcet point de vue commande (figure 1) ci-dessous décrit le fonctionnement d’un autre

système automatisé dont on voudrait réaliser la programmation par un système à microprocesseur

conçu autour du microprocesseur 6809 et le PIA 6821.

4-1) proposer une affectation des entrées du PIA 6821 nécessaire à la programmation de ce

grafcet (figure 1) 1,5pts

4-2) proposer un organigramme de ce système (2 pts)

4-3) en déduire un programme de commande de ce processus (figure 1) en langage assembleur

(3,5pts)

Enseignant : Eric Fotcha 4

Figure 1 : grafcet

PROBLEME 3 : CALCUL D’UNE MEMOIRE (11 points)

Pour les besoins d’une application vous devez construire une mémoire stockant des mots

de seize bits. On dispose à cet effet de boitiers:

- De mémoire vive RAM0 à RAM8 dotées chacune de dix entrées d’adresse, huit

sorties de données, une entrée de sélection active au niveau bas.

- De mémoire morte ROM1 et ROM2 ayant chacune douze entrées d’adresses, huit

sorties de données et une entrée de sélection active au niveau haut.

- De mémoire morte ROM4 à ROM6 équipées chacune de douze entrées d’adresses,

quatre sorties de données et une entrée de sélection active au niveau haut.

1- Déterminer la capacité de la mémoire vive disponible en kilobits. (0.75 pt)

2- Déterminer la capacité de la mémoire morte disponible en mot mémoire. (0.75 pt)

3- Préciser l’organisation de la mémoire. On supposera la zone ROM aux adresses

basses. (1.5 pts)

4- Exprimer la capacité totale de la mémoire construite:

a) En giga-octet. (0.75 pt)

b) En kilo mot-mémoire. (0.75 pt)

5- Sachant le mode sélection par décodage, préciser les adresses basse et haute associées

à chacun des boîtiers. (2 pts)

6- Donner la localisation puis l’adresse du 1050e mot mémoire en RAM. (1.5 pts)

7- Dresser le schéma de câblage de cette mémoire. (3 pts)

Enseignant : Eric Fotcha 5

Vous aimerez peut-être aussi

- Contrôle ContinuDocument3 pagesContrôle Continuarnaud tchouaniPas encore d'évaluation

- TD 1Document1 pageTD 1Mariem SelmiPas encore d'évaluation

- Test QCMDocument5 pagesTest QCMFabrice Bernard100% (1)

- Chapitre 5 LE TMS320C6701 DSP PDFDocument9 pagesChapitre 5 LE TMS320C6701 DSP PDFSmart ClassePas encore d'évaluation

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- TD Architecture Des CalculateursDocument5 pagesTD Architecture Des CalculateursIbrahim BadamassiPas encore d'évaluation

- AO L2 Série1Document4 pagesAO L2 Série1Smail Smart100% (1)

- FICHE TD InformatiqueDocument5 pagesFICHE TD InformatiquebertrandPas encore d'évaluation

- TD2-Architecture Des Ordinateurs GIT 2020-2021Document2 pagesTD2-Architecture Des Ordinateurs GIT 2020-2021Cheick Sidi Mohamed SakhoPas encore d'évaluation

- Base Des Microcontrôleur2021Document62 pagesBase Des Microcontrôleur2021Ayman LamzouriPas encore d'évaluation

- Adressage MemoireDocument10 pagesAdressage MemoireLibre HamataPas encore d'évaluation

- TD CH 3 Architecture Des Ordinateurs 2Document1 pageTD CH 3 Architecture Des Ordinateurs 2Pape Moussa DiopPas encore d'évaluation

- Toaz - Info QCM Assembleur 68000 PR - PDFDocument3 pagesToaz - Info QCM Assembleur 68000 PR - PDFNaciri HananePas encore d'évaluation

- TD 1 MicrocontroleurDocument5 pagesTD 1 MicrocontroleursilonePas encore d'évaluation

- Examen Corrigé Informatique Industriel - Univ M'Sila, 2019Document3 pagesExamen Corrigé Informatique Industriel - Univ M'Sila, 2019AYOUB RIADPas encore d'évaluation

- TD5LAT54Document1 pageTD5LAT54Smati DjamelPas encore d'évaluation

- Examen IP Essentials - VF - CorrectionDocument5 pagesExamen IP Essentials - VF - CorrectionRania khadraouiPas encore d'évaluation

- Test de base-ATO-Mars 2023Document1 pageTest de base-ATO-Mars 2023Germain ANANOUPas encore d'évaluation

- Devoir LibreDocument3 pagesDevoir LibreAbdessadek Elbachiri100% (1)

- Cours-mcAVRN (Mode de Compatibilité)Document181 pagesCours-mcAVRN (Mode de Compatibilité)larbi33% (3)

- TD Serie N2-2022Document4 pagesTD Serie N2-2022yoannaffantodji750Pas encore d'évaluation

- Moto 6809Document46 pagesMoto 6809Kawtar FelkiPas encore d'évaluation

- Série Exercices TD1Document2 pagesSérie Exercices TD1Colmain Nassiri100% (2)

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Traitement de L'information PDFDocument6 pagesTraitement de L'information PDFFarid AfifiPas encore d'évaluation

- TD 2Document7 pagesTD 2paroles dela6T100% (3)

- Support de TDDocument4 pagesSupport de TDazza memmiPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 51Document18 pagesCours Microcontrôleur Microprocesseur 51NasriMohsenPas encore d'évaluation

- Descriptif Des Ressources TechniquesDocument5 pagesDescriptif Des Ressources TechniquesLedoux NgabaPas encore d'évaluation

- Un - Syst - Me - Microprocesseur - PDF Filename - UTF-8''Un Système À MicroprocesseurDocument11 pagesUn - Syst - Me - Microprocesseur - PDF Filename - UTF-8''Un Système À MicroprocesseurLynda MOKRANIPas encore d'évaluation

- Chapitre 3 - 090738Document11 pagesChapitre 3 - 090738Rãmï RøÿãlPas encore d'évaluation

- TD IpDocument3 pagesTD IpSouissi IchrakPas encore d'évaluation

- Chapitre 3 Le Microcontroleur Pic 16f84Document29 pagesChapitre 3 Le Microcontroleur Pic 16f84Samen LempirePas encore d'évaluation

- Corrige TD Microcontroleur Pic 16f84Document11 pagesCorrige TD Microcontroleur Pic 16f84HamdiHa92% (109)

- TP 1Document5 pagesTP 1hiwiraPas encore d'évaluation

- 1 Cours Microcontrôleur PIC 16F84Document23 pages1 Cours Microcontrôleur PIC 16F84shileykoss100% (2)

- Interro Mi3 Ato 14novDocument1 pageInterro Mi3 Ato 14novHaleem OlawalePas encore d'évaluation

- PIC16F84Document22 pagesPIC16F84Rida bellarranePas encore d'évaluation

- Travaux DIRIGES TLECDocument4 pagesTravaux DIRIGES TLECnantesPas encore d'évaluation

- TD 2 Mémoires-1Document3 pagesTD 2 Mémoires-1القرآن الكريمPas encore d'évaluation

- TD 3 DSP RT 2020 1Document3 pagesTD 3 DSP RT 2020 1Amira HachemiPas encore d'évaluation

- Ccna IpDocument4 pagesCcna IpAy SarPas encore d'évaluation

- Traiter 2 SteDocument50 pagesTraiter 2 SteFadwa GHANIPas encore d'évaluation

- TD VHDLPPDocument23 pagesTD VHDLPPMël DjäPas encore d'évaluation

- ExercicesSMI P1Document15 pagesExercicesSMI P1IbrahimFaroukSolarPas encore d'évaluation

- Cours Trames EleveDocument3 pagesCours Trames EleveTsukyPas encore d'évaluation

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- TP1 - Static PDFDocument2 pagesTP1 - Static PDFSoufiane GoPas encore d'évaluation

- Architectures RISC Et ExemplesDocument6 pagesArchitectures RISC Et ExemplesjuniorPas encore d'évaluation

- TD1 ArmDocument4 pagesTD1 Armazza memmiPas encore d'évaluation

- TD 4Document4 pagesTD 4salma ben hssinPas encore d'évaluation

- Achitecture Ordi 3iemeDocument3 pagesAchitecture Ordi 3iemeIvan FotsoPas encore d'évaluation

- TD ArchiDocument2 pagesTD Archinznnznz sghshPas encore d'évaluation

- TD de MicroP Et MicroC - Master IEADocument2 pagesTD de MicroP Et MicroC - Master IEAAymard MougouPas encore d'évaluation

- TD2 SMP Mcil2Document1 pageTD2 SMP Mcil2Sabrina BenabdessalemPas encore d'évaluation

- Profil de couleur: Explorer la perception et l'analyse visuelles en vision par ordinateurD'EverandProfil de couleur: Explorer la perception et l'analyse visuelles en vision par ordinateurPas encore d'évaluation

- Machines de Jeux: Architecture des Consoles de Jeux VidéoD'EverandMachines de Jeux: Architecture des Consoles de Jeux VidéoÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Les macros avec OpenOffice CALC: La programmation BASIC pour tousD'EverandLes macros avec OpenOffice CALC: La programmation BASIC pour tousPas encore d'évaluation

- TPN 4: Détection Infrarouge Et Étude Du Détecteur Photoélectrique - RéflexDocument8 pagesTPN 4: Détection Infrarouge Et Étude Du Détecteur Photoélectrique - RéflexFotcha EricPas encore d'évaluation

- Fiche de TD N01 Transmission Analogique ASR3Document4 pagesFiche de TD N01 Transmission Analogique ASR3Fotcha EricPas encore d'évaluation

- TP N01&2Document6 pagesTP N01&2Fotcha EricPas encore d'évaluation

- Cours de Capteur Industriel Et Chaine de Mesure: Departement D'Electrotchnique: Niveau: 3 (Semestre 6)Document7 pagesCours de Capteur Industriel Et Chaine de Mesure: Departement D'Electrotchnique: Niveau: 3 (Semestre 6)Fotcha EricPas encore d'évaluation

- CHAPITRE 2 Synthese Des Correcteurs PIDDocument23 pagesCHAPITRE 2 Synthese Des Correcteurs PIDFotcha EricPas encore d'évaluation

- Contrôle Continu de Transmission Numérique - 2024Document2 pagesContrôle Continu de Transmission Numérique - 2024Fotcha EricPas encore d'évaluation

- CC DE Techniques de Transmissions AnalogiquesDocument2 pagesCC DE Techniques de Transmissions AnalogiquesFotcha EricPas encore d'évaluation

- TD3 de CapteursDocument4 pagesTD3 de CapteursFotcha EricPas encore d'évaluation

- Fiche de TD N02 Transmission Analogique ASR3Document6 pagesFiche de TD N02 Transmission Analogique ASR3Fotcha EricPas encore d'évaluation

- CC D'antenne Et Telecom Spacial TC1 - 2022Document8 pagesCC D'antenne Et Telecom Spacial TC1 - 2022Fotcha EricPas encore d'évaluation

- CC D'antenne Et Telecom Spacial TC1 - 2021Document2 pagesCC D'antenne Et Telecom Spacial TC1 - 2021Fotcha EricPas encore d'évaluation

- A1 - Antenne YagiDocument10 pagesA1 - Antenne YagiFotcha EricPas encore d'évaluation

- Programme Transmissions AnalogiquesDocument1 pageProgramme Transmissions AnalogiquesFotcha EricPas encore d'évaluation

- Schéma Bloc D'un Modulateur.: Radiotechnique Modulation de Fréquence Chapitre 3Document8 pagesSchéma Bloc D'un Modulateur.: Radiotechnique Modulation de Fréquence Chapitre 3Fotcha EricPas encore d'évaluation

- TD2 de CapteursDocument3 pagesTD2 de CapteursFotcha Eric100% (2)

- TD1 de CapteursDocument6 pagesTD1 de CapteursFotcha EricPas encore d'évaluation

- I U G É T: TPN 1: Synthèse Des Capteurs ArduinoDocument7 pagesI U G É T: TPN 1: Synthèse Des Capteurs ArduinoFotcha EricPas encore d'évaluation

- CC - Commande de PuissanceDocument1 pageCC - Commande de PuissanceFotcha EricPas encore d'évaluation

- Structure Des Circuits de Commande Et de PuissanceDocument10 pagesStructure Des Circuits de Commande Et de PuissanceFotcha EricPas encore d'évaluation

- CC 2020 IugetDocument2 pagesCC 2020 IugetFotcha EricPas encore d'évaluation

- Les Procedes de FreinageDocument12 pagesLes Procedes de FreinageFotcha EricPas encore d'évaluation

- GradateurDocument8 pagesGradateurFotcha EricPas encore d'évaluation

- OnduleurDocument10 pagesOnduleurFotcha EricPas encore d'évaluation

- Variateurs de Vitesse - MAS2Document10 pagesVariateurs de Vitesse - MAS2Fotcha EricPas encore d'évaluation

- Les Procedes de DemarrageDocument23 pagesLes Procedes de DemarrageFotcha Eric100% (1)

- VDP msx1Document57 pagesVDP msx1neslouPas encore d'évaluation

- Solution SecuriteDocument45 pagesSolution SecuriteKarim KhrifechPas encore d'évaluation

- Exercice IptableDocument2 pagesExercice IptableEl Amrani NadyaPas encore d'évaluation

- Sage BDC 128082 Changement Nom ServeurDocument3 pagesSage BDC 128082 Changement Nom ServeurYassine MOUHADDIRPas encore d'évaluation

- Solution TD N°2: Mr. BENTAALLAH Mohamed AmineDocument14 pagesSolution TD N°2: Mr. BENTAALLAH Mohamed AmineYobaraPas encore d'évaluation

- Cours Projet Electronique 1Document17 pagesCours Projet Electronique 1ryadhPas encore d'évaluation

- Nmap Options PDFDocument2 pagesNmap Options PDFhafidciscoPas encore d'évaluation

- Efm EsaDocument3 pagesEfm EsaYacine BELGHARDPas encore d'évaluation

- ITE7 Chp1Document45 pagesITE7 Chp1Ibrahima sory Bah100% (1)

- Fonction ComptageDocument9 pagesFonction ComptagedukenukembabiesPas encore d'évaluation

- Expose en ArchitectureDocument6 pagesExpose en ArchitectureMAMADOU BAHPas encore d'évaluation

- DRBLDocument18 pagesDRBLNaseeb RamlakhanPas encore d'évaluation

- Composants de L'ordinateurDocument3 pagesComposants de L'ordinateurnguessan lassiePas encore d'évaluation

- Usermanual Pclab2000ltDocument40 pagesUsermanual Pclab2000ltGabriela260667Pas encore d'évaluation

- Projet WifiDocument56 pagesProjet Wifikhalid100% (3)

- Premiers Pas Avec D RatsDocument16 pagesPremiers Pas Avec D RatsNoureddineLahouelPas encore d'évaluation

- TD 12 - FiliusDocument8 pagesTD 12 - FiliusconfuciuslesangPas encore d'évaluation

- Guide Utilisateur CV Remarquable 1ultimatumDocument1 pageGuide Utilisateur CV Remarquable 1ultimatumGermain DanzabéPas encore d'évaluation

- Cluster Apache Haute Disponibilité Avec Pacemaker (Centos 7)Document9 pagesCluster Apache Haute Disponibilité Avec Pacemaker (Centos 7)elies_jabri7874Pas encore d'évaluation

- CucmDocument33 pagesCucmBryan AdamsPas encore d'évaluation

- Initiation AssembleurDocument113 pagesInitiation Assembleurwafa wafaPas encore d'évaluation

- ScaNv6 instructorPPT Chapter8Document67 pagesScaNv6 instructorPPT Chapter8blaisePas encore d'évaluation

- RakotoarisoaLazaZ ESPA LIC 2017Document79 pagesRakotoarisoaLazaZ ESPA LIC 2017Texe taxePas encore d'évaluation

- Configuration D'un Routeur PDFDocument9 pagesConfiguration D'un Routeur PDFOthmane MansouriPas encore d'évaluation

- TP 2 SuiteDocument2 pagesTP 2 Suiteyann chebuPas encore d'évaluation

- Les Types de Profils Des UtilisateursDocument2 pagesLes Types de Profils Des Utilisateursyassin El YatimPas encore d'évaluation

- ACL Bon CoursDocument16 pagesACL Bon CoursElvÏs ElvÏsPas encore d'évaluation

- Voip Packet Tracer Tuto BasiqueDocument7 pagesVoip Packet Tracer Tuto BasiqueUsPas encore d'évaluation

- CloneZilla Partie 2 Restaurer Une Image SystemeDocument17 pagesCloneZilla Partie 2 Restaurer Une Image SystemetitusPas encore d'évaluation

- TD N - 1-2014 - 2015Document3 pagesTD N - 1-2014 - 2015Ingenieur Ensa0% (1)