Académique Documents

Professionnel Documents

Culture Documents

TD Serie N2-2022

Transféré par

yoannaffantodji750Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD Serie N2-2022

Transféré par

yoannaffantodji750Droits d'auteur :

Formats disponibles

2022-2023

ARCHITECTURE DES ORDINATEURS – Licence 1 TWIN

Fiche De Travaux Dirigés- série n°2

IMPORTANT : Cette série de TD comporte huit (9) exercices à préparer à la maison (i.e. à faire

obligatoirement par chaque étudiant) ; un contrôle, suivi de sanctions pour tous ceux qui ne les auront pas faits,

sera systématiquement effectué à chacune des séances. Aucune excuse ne sera ni acceptée, ni tolérée.

Exercice 1 : mémoire et bus

Soit un ordinateur dont les mots mémoires sont composés de 32 bits. Cet ordinateur dispose de 4Mo de

mémoire.

1. Un entier étant codé sur un mot, combien de mot cet ordinateur peut-il mémoriser simultanément ?

2. Combien fils, le bus d’adresse devra-t-il comporter pour adresser toutes les cases mémoires ?

Exercice 2 : capacité d’une mémoire

Soit la mémoire suivante dans laquelle chaque caractère s’écrit suivant la largeur (de la mémoire).

1- Quel est le format des données ?

2- En déduire la capacité en Mo et en Go de la mémoire

?

Soit la phrase suivante : Le professeur d’architecture

d’ordinateur est rentré en classe.

3- Combien de lettres et caractères contient cette

phrase ?

4- Combien de cellules mémoires faut-il pour

enregistrer cette phrase ?

5- Quelle taille mémoire en ko qu’occupe cette phrase

dans la mémoire ?

Exercice 3 : performance de bus

Le bus de données (ou bus processeur – FSB) du processeur Intel 8086, fonctionnant à une fréquence de 10

MHz, nécessite 4 cycles d’horloge pour lire un mot mémoire.

1) Est-ce un bus synchrone ou asynchrone ? justifiez votre réponse.

2) Déterminer en million d’instruction par seconde, la capacité de ce bus

3) La taille d'un mot mémoire étant de 16 bits, calculer la bande passante de ce bus en bits/s et en octets/s.

Exercice 4 : Performance d’un microprocesseur

Pour mesurer les performances des µPRO on définit le CPI et le MIPS.

1- Donner la signification et la définition des sigles suivants CPI et de MIPS.

2- Donner la formule reliant les deux paramètres.

3- Donner la fréquence d’un processeur dont le MIPS = 500 et le CPI = 5.

4- Proposer deux solutions pour améliorer la performance des ordinateurs.

Exercice 5 : la carte mère

TD_Architecture des ordinateurs Page 1

Sur la carte mère d’un certain ordinateur, on trouve :

o Un processeur 8 bits, ce qui implique que la mémoire est adressée octet par octet, et que le processeur

peut lire et écrire des mots de 8 bits en mémoire centrale ;

o Un bus système, dont le bus d’adresses est d’une largeur de 24 bits ;

o Un certain nombre de circuits mémoire 8 bits, chacun d’une capacité de 512Ko.

1) Quelle est la largeur, en nombre de bits, du bus de données ?

2) En supposant que le bus d’adresses ne sert à adresser que la mémoire centrale de l’ordinateur, combien

de circuits mémoire sont présents sur la carte mère ?

Exercice 6 : bande passante

On souhaite lire un film se trouvant sur un disque dur, connecté à l’ordinateur via un bus USB1.1. Le film est

non-compressé, et constitué d’une succession d’images de 1024 *768 pixels en 256 couleurs. On suppose que

le défilement des images se fait en 24 images par seconde. Une liaison USB1.1 permet le transfert de données

bit par bit à la fréquence de 12 MHz.

1. Quelle est la taille en octets d’une image du film ?

2. Quel est le débit (en Mo/s) requis pour le transfert du film du disque dur à la mémoire vidéo ?

3. Quelle est la bande passante en Mo/s du bus USB1.1 envisagé pour la lecture du film ?

Exercice 7 : jeu d’instruction

On se place sur un processeur hypothétique, qui accède à une mémoire centrale dans laquelle la taille d’une

Case mémoire est de 2 octets. Ce processeur dispose des registres suivants :

o IR, le registre d’instruction ;

o PC, le compteur de programme ;

o A (comme accumulateur), un registre temporaire pour le stockage du résultat des opérations.

Les instructions sont codées sur 2 octets comme suit :

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Opcode Adresse

On détaille les instructions suivantes :

Mnémonique Opcode Opération réalisée

LOAD (0001)2 (1)H Charger le mot dont l’adresse est donnée dans A

STORE (0010)2 (2)H Stocker le mot contenu dans A à l’adresse donnée

ADD (0101)2 (5)H Ajouter l’entier naturel à l’adresse donnée à A.

On rappelle que le jeu d’instruction est le nombre d’instructions (mnémoniques) pouvant être utilisées pour

programmer un microprocesseur.

1) Quel est en bits le format des instructions ?

2) Sur combien de bits est codé le code opératoire ainsi que le champ opérande ?

3) Combien d’instructions, suivant le codage indiqué ci-dessus, peut compter le jeu d’instruction ?

4) Quel est le nombre maximal d’adresses auxquelles une telle instruction peut faire référence ?

5) On considère le morceau de programme suivant, écrit en « langage d’assemblage » :

LOAD (130) H

ADD (131) H

STORE (133) H

a) Expliquer chaque ligne du programme

b) Que fait- il ?

TD_Architecture des ordinateurs Page 2

EXERCICE 8 : traitement d’une instruction en mémoire (5 pts)

La mémoire centrale (RAM) d’une machine contient 64 mots mémoire et peut exécuter 13 opérations

(arithmétiques et logiques).

1. Le traitement d’une instruction peut être décomposé en trois phases. Expliquer la phase de recherche

de l’instruction à traiter.

2. Donner la taille (en bit) du compteur ordinal (CO)

Une instruction est codée comme suit :

Instruction

Code opération Adresse1, adresse2, adresse3

3. Que représente le code opération ? donner sa taille (en bit)

4. En déduire la taille minimale (en bits) du registre instruction (RI)

Si la taille de cette RAM est de 192 octets,

5. Donner la taille réelle (en octet) du registre instruction (RI).

EXERCICE 8 : Architecture pipeline de DAVID PATTERSON

Définition : Un pipeline (chaîne de traitement), dans la microarchitecture d'un processeur, est l'élément

dans lequel l'exécution des instructions est découpée en étages. Avec un pipeline, le processeur peut

commencer à exécuter une nouvelle instruction sans attendre que la précédente soit terminée. Chacune de ces

étapes est réalisée dans un circuit séparé des autres. Le circuit qui permet d'effectuer une étape s’appelle un

étage de pipeline. Le nombre total d'étapes nécessaires pour effectuer une instruction (et donc le nombre

d'étages du pipeline) est appelé la profondeur du pipeline.

Plan d'un pipeline générique à trois étapes ou séquençage des instructions

Il existe plusieurs types de pipeline dont le plus utilisé est celui de DAVID PATTERSON, inventeur des

processeurs RISC et du concept de pipeline. Avec ce pipeline, 5 étapes sont nécessaires pour accomplir une

instruction :

1. IF (Instruction Fetch) charge l'instruction à exécuter dans le pipeline.

2. ID (Instruction Decode) décode l'instruction et adresse les registres.

3. EX (Execute) exécute l'instruction (par la ou les unités arithmétiques et logiques).

4. MEM (Memory), dénote un transfert depuis un registre vers la mémoire dans le cas d'une instruction du

type STORE (accès en écriture) et de la mémoire vers un registre dans le cas d'un LOAD (accès en lecture).

5. WB (Write Back) stocke le résultat dans un registre.

La source peut être la mémoire ou bien un registre

(Source WIKIPEDIA)

Problème : nous voulons traiter 3 instructions en supposant que chaque étape met 1 cycle d'horloge pour

s’exécuter.

Questions

TD_Architecture des ordinateurs Page 3

1- Quelle est la profondeur du pipeline de DAVID PATTERSON ?

2- Donner le séquençage des instructions dans une architecture sans pipeline ? En déduire le nombre de

coups d’horloge pour exécuter ces 3 instructions.

3- Donner le plan d'un pipeline de DAVID PATTERSON pour ces 3 instructions ? En déduire le nombre

de coups d’horloge pour exécuter ces 3 instructions.

4- A partir de quel instant tous les étages du pipeline de DAVID PATTERSON sont utilisés ?

Généraliser à un pipeline de DAVID PATTERSON de profondeur n ayant un grand nombre

d’instructions à exécuter. Nombre d’instructions supérieur à la profondeur.

5- Conclure

TD_Architecture des ordinateurs Page 4

Vous aimerez peut-être aussi

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Série Exercices TD1Document2 pagesSérie Exercices TD1Colmain Nassiri100% (2)

- SystemeDocument1 pageSystemeNaquis Tepiele100% (1)

- TD Architecture Des CalculateursDocument5 pagesTD Architecture Des CalculateursIbrahim BadamassiPas encore d'évaluation

- AO L2 Série1Document4 pagesAO L2 Série1Smail Smart100% (1)

- 2020-2021 Examen AoDocument5 pages2020-2021 Examen AoZaki ZakiPas encore d'évaluation

- CoursAssembleur - Chap1 Et 2Document28 pagesCoursAssembleur - Chap1 Et 2Achraf ElkhodariPas encore d'évaluation

- Solutionnaire Archi TD1Document5 pagesSolutionnaire Archi TD1Colmain Nassiri100% (1)

- Corrigé Série de TD N° 3Document5 pagesCorrigé Série de TD N° 3Alaa MessaoudPas encore d'évaluation

- Série de TD N° 3: Nommez Les Composants D'ordinateur SuivantsDocument4 pagesSérie de TD N° 3: Nommez Les Composants D'ordinateur SuivantsAlaa MessaoudPas encore d'évaluation

- Serie ExercicesDocument4 pagesSerie Exerciceskamel benkouider sahraouiPas encore d'évaluation

- Cours Calculateurs L2 InfoDocument85 pagesCours Calculateurs L2 InfoBajikila AmandPas encore d'évaluation

- TDs ArchitectureDocument5 pagesTDs Architectureben houria yassine100% (1)

- Exercice 1:: Série 1Document2 pagesExercice 1:: Série 1CAMPUS TIZI OUZOUPas encore d'évaluation

- TD2-Architecture Des Ordinateurs GIT 2020-2021Document2 pagesTD2-Architecture Des Ordinateurs GIT 2020-2021Cheick Sidi Mohamed SakhoPas encore d'évaluation

- SN - Architecture - 2063 CorDocument3 pagesSN - Architecture - 2063 CorMarc AzemkouPas encore d'évaluation

- Support de TDDocument4 pagesSupport de TDazza memmiPas encore d'évaluation

- QCM Sur Le MicroprocesseurDocument11 pagesQCM Sur Le MicroprocesseurGhislaine REMONDO100% (1)

- TD Architecture Des Ordinateurs PDFDocument17 pagesTD Architecture Des Ordinateurs PDFAhmedBoukadPas encore d'évaluation

- 0B4CjIMFACisHckpYZHNmY2xDTms PDFDocument4 pages0B4CjIMFACisHckpYZHNmY2xDTms PDFAbdoul Nasser Aboubacar100% (1)

- Cours Micro Pro - WafaDocument79 pagesCours Micro Pro - WafaLaribi TakwaPas encore d'évaluation

- TD Informatique Droit 1Document8 pagesTD Informatique Droit 1yann chebuPas encore d'évaluation

- TD 1 MicrocontroleurDocument5 pagesTD 1 MicrocontroleursilonePas encore d'évaluation

- FICHE TD InformatiqueDocument5 pagesFICHE TD InformatiquebertrandPas encore d'évaluation

- Test QCMDocument5 pagesTest QCMFabrice Bernard100% (1)

- Examen Microsoft Word: Architecture de L'ordinateurDocument4 pagesExamen Microsoft Word: Architecture de L'ordinateurHiba ChafikPas encore d'évaluation

- QCM Sur La Carte MèreDocument18 pagesQCM Sur La Carte MèreGhislaine REMONDO100% (1)

- Chapitre 2 Lat 54Document3 pagesChapitre 2 Lat 54Smati DjamelPas encore d'évaluation

- Examen1+Solution Architecture Des OrdinateursDocument7 pagesExamen1+Solution Architecture Des Ordinateursihadjkaddour7Pas encore d'évaluation

- TP 1Document5 pagesTP 1hiwiraPas encore d'évaluation

- MCU - 2 - Principes Généraux Des MicrocontrôleursDocument11 pagesMCU - 2 - Principes Généraux Des MicrocontrôleursrlekcirPas encore d'évaluation

- CHAPITRE 1 - GéneralitésDocument9 pagesCHAPITRE 1 - GéneralitésZERARKA Mohamed FawziPas encore d'évaluation

- TD1 ArmDocument4 pagesTD1 Armazza memmiPas encore d'évaluation

- Exercices TDDocument6 pagesExercices TDArthur CouteauPas encore d'évaluation

- System 1 Id 048Document8 pagesSystem 1 Id 048Kam ZegPas encore d'évaluation

- TD ArchiDocument2 pagesTD Archinznnznz sghshPas encore d'évaluation

- Slide Animation1 Atmega16bisDocument25 pagesSlide Animation1 Atmega16bisNadhir BndPas encore d'évaluation

- Presentation MicroprocesseurDocument340 pagesPresentation Microprocesseurpapinou sarrPas encore d'évaluation

- Chapitre 2-1Document11 pagesChapitre 2-1bouchenebPas encore d'évaluation

- Chap4 CPU PDFDocument18 pagesChap4 CPU PDFGhassen OuniPas encore d'évaluation

- Correction Examen AO 2021 2022Document4 pagesCorrection Examen AO 2021 2022ghostninja745Pas encore d'évaluation

- Partie-2-Microprocesseur + MemoireDocument14 pagesPartie-2-Microprocesseur + MemoireyaoPas encore d'évaluation

- Chapitre1 Architecture - Ordinateurs - 2019 - 2020Document13 pagesChapitre1 Architecture - Ordinateurs - 2019 - 2020Bessem BessemPas encore d'évaluation

- CII3 ADocument8 pagesCII3 Abenamirasihem745Pas encore d'évaluation

- Cours 2Document8 pagesCours 2Achraf HouilaPas encore d'évaluation

- Microproc Enstb2001Document124 pagesMicroproc Enstb2001Mohamed EnnajiPas encore d'évaluation

- sérieTD2 2021Document3 pagessérieTD2 2021Møu AtezPas encore d'évaluation

- Moto 6809Document46 pagesMoto 6809Kawtar FelkiPas encore d'évaluation

- Solutionnaire Exo - 1-2-3-4Document2 pagesSolutionnaire Exo - 1-2-3-4Colmain NassiriPas encore d'évaluation

- Cours 20 SocDocument3 pagesCours 20 SocKarim AmmaniPas encore d'évaluation

- Examen3 Electronique Et Composants Des SystèmesDocument3 pagesExamen3 Electronique Et Composants Des Systèmesfouzikr22Pas encore d'évaluation

- Ao 2 TDDocument3 pagesAo 2 TDBerbaoui KamelPas encore d'évaluation

- Synthèse TMSIR V1 PDFDocument8 pagesSynthèse TMSIR V1 PDFSolo TetouaniPas encore d'évaluation

- Cours 1 Microprocesseurs - BoukhobzaDocument13 pagesCours 1 Microprocesseurs - BoukhobzaMohamed LMPas encore d'évaluation

- Interro Mi3 Ato 14novDocument1 pageInterro Mi3 Ato 14novHaleem OlawalePas encore d'évaluation

- COURS ImsetDocument17 pagesCOURS ImsetSkander Ben OthmenPas encore d'évaluation

- Architecture Du ProcesseurDocument5 pagesArchitecture Du ProcesseurLinda GachaPas encore d'évaluation

- Chapitre 3 - 090738Document11 pagesChapitre 3 - 090738Rãmï RøÿãlPas encore d'évaluation

- Ex Temps ReelDocument2 pagesEx Temps ReelChristian HaddadPas encore d'évaluation

- Cours Upge s11Document7 pagesCours Upge s11ufkfkf17Pas encore d'évaluation

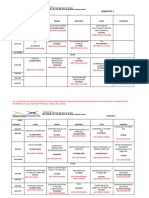

- Emploi Du Temps Ispa Du s2 2023-2024 ActualiséDocument17 pagesEmploi Du Temps Ispa Du s2 2023-2024 Actualiséyoannaffantodji750Pas encore d'évaluation

- Bureau ProvisoireDocument2 pagesBureau Provisoireyoannaffantodji750Pas encore d'évaluation

- Eco Generale Licence I IspaDocument29 pagesEco Generale Licence I Ispayoannaffantodji750Pas encore d'évaluation

- TD1 Transmission 2BTS RIT 2023 24Document3 pagesTD1 Transmission 2BTS RIT 2023 24yoannaffantodji750Pas encore d'évaluation

- SupportdecousInformatique2S3 S4LMDSTDocument77 pagesSupportdecousInformatique2S3 S4LMDSTseriannyPas encore d'évaluation

- Cours Stat ChapI Edited Edited EditedDocument13 pagesCours Stat ChapI Edited Edited Editedyoannaffantodji750Pas encore d'évaluation

- Cours Stat ChapI Edited Edited EditedDocument13 pagesCours Stat ChapI Edited Edited Editedyoannaffantodji750Pas encore d'évaluation

- GENERALITES (Réparé)Document33 pagesGENERALITES (Réparé)ahoumanPas encore d'évaluation

- Cours Electricité Chap1 ESIIT1-IsPA 2023-24Document12 pagesCours Electricité Chap1 ESIIT1-IsPA 2023-24yoannaffantodji750Pas encore d'évaluation

- Cours Trans Chap4 ESIIT1 2023 24Document14 pagesCours Trans Chap4 ESIIT1 2023 24yoannaffantodji750Pas encore d'évaluation

- Cours Licence 1Document66 pagesCours Licence 1yoannaffantodji750Pas encore d'évaluation

- Cours Electricité Chap1 ESIIT1-IsPA 2023-24Document12 pagesCours Electricité Chap1 ESIIT1-IsPA 2023-24yoannaffantodji750Pas encore d'évaluation

- Cours Maths Gle ESIIT1 2023 24Document58 pagesCours Maths Gle ESIIT1 2023 24yoannaffantodji750Pas encore d'évaluation

- Maths Fin Chap1&2 1BTS FC 2021 22Document29 pagesMaths Fin Chap1&2 1BTS FC 2021 22yoannaffantodji750Pas encore d'évaluation

- TD Serie N°1 TWIN1 2022Document2 pagesTD Serie N°1 TWIN1 2022yoannaffantodji750Pas encore d'évaluation

- Cours de Merise 1ère Année ISPADocument58 pagesCours de Merise 1ère Année ISPAyoannaffantodji750Pas encore d'évaluation

- Emploi Du Temps Ispa Du s2 2023-2024 ActualiséDocument17 pagesEmploi Du Temps Ispa Du s2 2023-2024 Actualiséyoannaffantodji750Pas encore d'évaluation

- Cours Licence 1Document66 pagesCours Licence 1yoannaffantodji750Pas encore d'évaluation

- Note D'information - Qitaa 5Document1 pageNote D'information - Qitaa 5yoannaffantodji750Pas encore d'évaluation

- Club944 - Net - Injection Bosch L-JetronicDocument8 pagesClub944 - Net - Injection Bosch L-JetronicYann DaynatPas encore d'évaluation

- Rapport de StageDocument15 pagesRapport de StageAgossa BénédictePas encore d'évaluation

- BF492 mgt16041Document139 pagesBF492 mgt16041Michel BMPas encore d'évaluation

- Exo 18 Partitifs en LigneDocument1 pageExo 18 Partitifs en LigneMaria SousaPas encore d'évaluation

- Video RO1Document39 pagesVideo RO1lovebooksPas encore d'évaluation

- Cahier de Poutres Bloc Administration 1Document8 pagesCahier de Poutres Bloc Administration 1Ourajim issamPas encore d'évaluation

- Avp Loi 67.15 FRDocument9 pagesAvp Loi 67.15 FRSerge KohemunPas encore d'évaluation

- OEIL ROUGE ConstantineDocument45 pagesOEIL ROUGE Constantinemidou113Pas encore d'évaluation

- Coefficient K, Devis Estimatif, Quantitatif Et PlanificationDocument21 pagesCoefficient K, Devis Estimatif, Quantitatif Et PlanificationMarco JoyPas encore d'évaluation

- Brand PriceDocument6 pagesBrand PriceBonnesAffairesConstantine100% (1)

- Chapitre-Les Systèmes de ClimatisationDocument13 pagesChapitre-Les Systèmes de ClimatisationInsaf Bouazza ʚîɞ100% (2)

- Centre Universitaire Nour Bachir, El-Bayadh Institut Des Sciences 2ème Année Licence Génie Civil Exposé Écrit Pour Évaluation SemestrielleDocument8 pagesCentre Universitaire Nour Bachir, El-Bayadh Institut Des Sciences 2ème Année Licence Génie Civil Exposé Écrit Pour Évaluation SemestrielleMelek LakelPas encore d'évaluation

- 15 May 2013Document343 pages15 May 2013Download_Scribd_stufPas encore d'évaluation

- Attachement Du ChantierDocument10 pagesAttachement Du ChantierOussamaBahloul100% (1)

- Pf4 DessinDocument5 pagesPf4 Dessinfareltanda841Pas encore d'évaluation

- Cours de Absorption Des NutrimentsDocument67 pagesCours de Absorption Des NutrimentsHamidPas encore d'évaluation

- Dégradations de ChausséeDocument13 pagesDégradations de Chaussée'Tarik Louati50% (2)

- Chapitre 3 IRMPartie 3Document42 pagesChapitre 3 IRMPartie 3Khadhra LassouedPas encore d'évaluation

- Examen Pruebas de Acceso A La Universidad FRANCES 2021 2022Document13 pagesExamen Pruebas de Acceso A La Universidad FRANCES 2021 2022Andres HerreraPas encore d'évaluation

- Corbin 1458816683Document1 pageCorbin 1458816683rodrigomichellPas encore d'évaluation

- Chapitre 4Document12 pagesChapitre 4zakariamaazouztradingPas encore d'évaluation

- Rapport RFIDDocument29 pagesRapport RFIDed-fer666Pas encore d'évaluation

- Philosophie Subtile ParacelseDocument16 pagesPhilosophie Subtile Paracelseredvelvetmask2343Pas encore d'évaluation

- Parler de La Nourriture Mars 2021 FinaleDocument19 pagesParler de La Nourriture Mars 2021 FinalepeterPas encore d'évaluation

- Nouveau Microsoft Word DocumentDocument3 pagesNouveau Microsoft Word DocumentIlyas BoutouahanPas encore d'évaluation

- Revenu 1357Document28 pagesRevenu 1357concombre2607Pas encore d'évaluation

- CinematiqueDocument22 pagesCinematiquepaul_fredric3173Pas encore d'évaluation

- Première Année de Médecine Dentaire Module de Biophysique Chapitre 3 Prof Karim MANSOUR 2022Document26 pagesPremière Année de Médecine Dentaire Module de Biophysique Chapitre 3 Prof Karim MANSOUR 2022wiamePas encore d'évaluation

- Med 5an Cas Clinique1 GynecoDocument7 pagesMed 5an Cas Clinique1 GynecoIbtissem TissamPas encore d'évaluation

- Mouvements Plans Cours 1 2Document8 pagesMouvements Plans Cours 1 2kenza.elkansouriPas encore d'évaluation

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Apprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationD'EverandApprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationPas encore d'évaluation

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Conception & Modélisation CAO: Le guide ultime du débutantD'EverandConception & Modélisation CAO: Le guide ultime du débutantPas encore d'évaluation

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)

- Manuel de fabrication du savon: Je fabrique mes savons facilementD'EverandManuel de fabrication du savon: Je fabrique mes savons facilementÉvaluation : 5 sur 5 étoiles5/5 (4)

- Le guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandLe guide du hacker : le guide simplifié du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 5 sur 5 étoiles5/5 (2)

- Le trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsD'EverandLe trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Forex Trading facile à apprendre: Le guide d'introduction au marché des changes et aux stratégies de négociation les plus efficaces dans l'industrie des devises.D'EverandForex Trading facile à apprendre: Le guide d'introduction au marché des changes et aux stratégies de négociation les plus efficaces dans l'industrie des devises.Évaluation : 4 sur 5 étoiles4/5 (1)