Académique Documents

Professionnel Documents

Culture Documents

Gestion Des Interruptions

Gestion Des Interruptions

Transféré par

Dhafer MezghaniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Gestion Des Interruptions

Gestion Des Interruptions

Transféré par

Dhafer MezghaniDroits d'auteur :

Formats disponibles

Cortex-M3: Déroulement des Cortex-M3: Déroulement des

Interruptions Interruptions

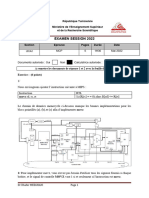

Pour répondre à une interruption, le Cortex M3:

• Sauvgarde automatique de l’état du processeur dans la

pile.

• Charge l’adresse de la routine d’interruption à partir de la

table des vecteurs.

• Exécute la routine d’interruption.

• Restitue automatique de l’état précédent de la machine

pour revenir au programme de départ.

31 32

Cortex-M3: Déroulement des Cortex-M3: Déroulement des

Interruptions Interruptions

Temps de réponse d’une interruption Cortex-M3 Tail Chaining: Recherche des Interruptions en attente

IRQ1 •ARM7

IRQ Highest

IRQ2

42 CYCLES

PUSH ISR POP ARM7 PUSH 1 ISR 1 POP 1 PUSH 2 ISR 2 POP 2

Interrupt handling in

assembler code 26 16 26 16

12 12

cycles cycles Tail-chaining

Save Registers Cortex-M3 PUSH ISR 1 ISR 2 POP

(Hardware) R0-R3 ; R12 Restore Registers Interrupt handling in HW

12 6 12

R15 (Program Counter) (Hardware) 6 CYCLES

R14 (Link register adresse de retour) Cortex-M3

PSR (Registre d’état) •ARM7

• 26 cycles pour déclencher l’exécution de ISR1 •12 cycles pour déclencher l’exécution de ISR1

Pour L’architecture du ARM7 l’opérations PUSH nécessite • 42 cycles pour passer de ISR1à ISR2 • 6 cycles pour passer de ISR1à ISR2

• 16 cycles pour retourner au prog principal • 12 cycles pour retourner au prog principal

26 cycles et le POP nécessite 16 cycles d’horloges.

33 34

Cortex-M3: Déroulement des

Cortex-M3: Interrupt Handling

Interruptions

Preemption: priorité Late Arrival: Arrivé en retard de l’interruption de priorité

Inférieur à12 cycle

IRQ1

Highest IRQ1

IRQ2 Highest

IRQ2

42 CYCLES

ARM7 PUSH 1 PUSH 2 ISR 1 POP 2 ISR 2 POP 1

ARM7 PUSH 1 ISR 1 POP1 PUSH 2 ISR 2 POP2

26 26 16 16

16 26 16

26

Cortex-M3 PUSH ISR 1 ISR 2 POP

Cortex-M3 PUSH ISR 1 POP ISR 2 POP 6 12

Tail-

1- 6 12 Chaining

ARM7 12 7-18 CYCLES ARM7

• Il sauvgarde le contexte du Prog (PUSH1) Cortex-M3 • Sauvgarde le contexte du Prog(PUSH1) Cortex-M3

• 26 cycles pour déclencher l’exécution de ISR1 •Pendant la récupération (POP) si une interruption •Sauvgarde de ISR 2 (PUSH2)

• Récupérer le contexte (prog princi) (POP1) se présente •52 cycles pour déclencher l’éxecution de ISR 1 • Sauvgarde le contexte du Prog (PUSH)

• Pendant la récupération si une interruption se présente • il abandonne le pop • Récupérer le contenue des registres de ISR 2 • 12cycles pour déclencher l’éxecution de ISR 1

le pop termine sa tâche. • Il Iance le tail chaining puis il déclenche •16 cycles pour passer de ISR 1 à ISR 2 • 6cycles pour passer de ISR1 à ISR 2

•42 cycles pour passer de ISR1 à ISR2 l’exécution de ISR2

•7 à 18 cycles pour passer de ISR1 à ISR2 35 36

Cortex-M3: Interrupt Handling

Sup à 12 cycle

Inf à 12

Highest

cycle

Exemple

NMI

IRQ1

IRQ2

IRQ3

PUSH1 PUSH2 NMI ISR 1 POP2 ISR 2 ISR 3 POP1

Debut PUSH de

ISR 2 Cortex-M3

de ISR 2

6 cycles pour passer de NMI à ISR1

12 cycles pour passer de ISR1 à ISR2

6 cycles pour passer de ISR2 à ISR3

37

Vous aimerez peut-être aussi

- TD Electrocinetique Serie1Document2 pagesTD Electrocinetique Serie1All AhmeDciaPas encore d'évaluation

- French-UPS Modulaire 230vac - 7kVA1Document316 pagesFrench-UPS Modulaire 230vac - 7kVA1Omar L. FernandezPas encore d'évaluation

- CC1-Microprocesseur 8086-2020-2021-7 Janvier 2021Document3 pagesCC1-Microprocesseur 8086-2020-2021-7 Janvier 2021gffPas encore d'évaluation

- Chapitre I Microprocesseur 6809 GSEA12013 PDFDocument56 pagesChapitre I Microprocesseur 6809 GSEA12013 PDFRyan Hj100% (1)

- Chapitre I Microprocesseur 6809 GSEA12013Document56 pagesChapitre I Microprocesseur 6809 GSEA12013xanafahd78% (9)

- Cours Synthèses Convertisseurs StatiquesDocument4 pagesCours Synthèses Convertisseurs StatiquesMouncef El MarghichiPas encore d'évaluation

- Model Cours - CopieDocument9 pagesModel Cours - Copieabid alyaniPas encore d'évaluation

- Command HandlingDocument15 pagesCommand HandlingMoctar MoumouniPas encore d'évaluation

- Microcontrolleur: Traiter 1Document32 pagesMicrocontrolleur: Traiter 1farrouj abdelhamidPas encore d'évaluation

- Cours LST PIC 16F84 2019-2020Document116 pagesCours LST PIC 16F84 2019-2020Mouad Thf0% (1)

- DSASW00343875Document18 pagesDSASW00343875Rgt Rogert MikingaPas encore d'évaluation

- Etude Du Microcontrleur Pic16f84 160919133655Document72 pagesEtude Du Microcontrleur Pic16f84 160919133655فدوى غانيPas encore d'évaluation

- Cours PIC-1Document136 pagesCours PIC-1dbmariem8Pas encore d'évaluation

- UniversitÉ Pierre Et Marie CurieDocument44 pagesUniversitÉ Pierre Et Marie Curieribose06100% (1)

- Microcontrôleur Famille PIC 16oDocument10 pagesMicrocontrôleur Famille PIC 16oAbdellah Faqdani100% (1)

- Cours Electronique NumeriqueDocument44 pagesCours Electronique NumeriqueYoussef El AjraouiPas encore d'évaluation

- Archi2 Chap4 PIC8259ADocument58 pagesArchi2 Chap4 PIC8259AAyoub AbdellaouiPas encore d'évaluation

- MCIL3 - C - Chapitre 2 - IIDocument8 pagesMCIL3 - C - Chapitre 2 - IITurbo NSXPas encore d'évaluation

- CH 2 RESET Et Système Dhorloge RCCDocument52 pagesCH 2 RESET Et Système Dhorloge RCCCode Codeur100% (1)

- Archi CM09Document21 pagesArchi CM09Àźwű ŠāģhřűPas encore d'évaluation

- CH1 - architectureARMDocument16 pagesCH1 - architectureARMazza memmiPas encore d'évaluation

- Micro Control Eur 1Document73 pagesMicro Control Eur 1Marcelin SoukroumdePas encore d'évaluation

- S32K DSDocument100 pagesS32K DSNguyễn Mỹ KiênPas encore d'évaluation

- Interruptions PDFDocument16 pagesInterruptions PDFmodou BADIANEPas encore d'évaluation

- 01Document53 pages01Liza Linda DakarPas encore d'évaluation

- Examen 2013 (ACAD)Document4 pagesExamen 2013 (ACAD)zakiPas encore d'évaluation

- PTR 3 MaterielDocument15 pagesPTR 3 MaterielsystemeinfolicencePas encore d'évaluation

- TP ArchiDocument8 pagesTP ArchimalikouallaPas encore d'évaluation

- Chapitre III Microprocesseur 6809 GSEA1Document36 pagesChapitre III Microprocesseur 6809 GSEA1kaoutarPas encore d'évaluation

- Chapitre 2: Le Microcontrôleur Pic 18F45K22.: 1 PrésentationDocument11 pagesChapitre 2: Le Microcontrôleur Pic 18F45K22.: 1 PrésentationAbderrahman Amelougou100% (1)

- Chapitre 2 Microcontroleur Pic 16f877Document8 pagesChapitre 2 Microcontroleur Pic 16f877Redouane Amian100% (1)

- Le Fonctionnement en InterruptionDocument2 pagesLe Fonctionnement en Interruptiondriss chakdaliPas encore d'évaluation

- Le Fonctionnement en Interruption 1Document2 pagesLe Fonctionnement en Interruption 1maoukil ayoubPas encore d'évaluation

- Traiter 2 SteDocument50 pagesTraiter 2 SteFadwa GHANIPas encore d'évaluation

- CH1 Architecture ARMDocument22 pagesCH1 Architecture ARMMarwen SellamiPas encore d'évaluation

- Introduction Aux MC STM32 PDFDocument9 pagesIntroduction Aux MC STM32 PDFZied HouanebPas encore d'évaluation

- Systèmes Chap 12 Et 3Document10 pagesSystèmes Chap 12 Et 3Antoine LemlinPas encore d'évaluation

- Le Pic 16f84 Partie 1 CoursDocument6 pagesLe Pic 16f84 Partie 1 CoursKamologne UlrichPas encore d'évaluation

- Systèmes D'exploitation EmbarquéDocument109 pagesSystèmes D'exploitation EmbarquéABDELHAK MAHFOUDPas encore d'évaluation

- Microproc Enstb2001Document124 pagesMicroproc Enstb2001Mohamed EnnajiPas encore d'évaluation

- Chapitre 5 MicrocontroleursDocument28 pagesChapitre 5 Microcontroleursbenachour ismailPas encore d'évaluation

- STM32F4 TutorialDocument52 pagesSTM32F4 Tutorialamri100% (8)

- Chapitre2 SE ARCHITECTURE DES MICROCONTROLLEURSDocument24 pagesChapitre2 SE ARCHITECTURE DES MICROCONTROLLEURSKarima ChakerPas encore d'évaluation

- Cours Système Embarqué-LpDocument99 pagesCours Système Embarqué-Lpmoumnimeryem2002Pas encore d'évaluation

- Les InterruptionsDocument19 pagesLes InterruptionsloirdighiPas encore d'évaluation

- LE PIC 16F876/877: Famille Mid-Range de MicrochipDocument80 pagesLE PIC 16F876/877: Famille Mid-Range de MicrochipKam ZegPas encore d'évaluation

- 2G CommandesDocument2 pages2G CommandesMoctar MoumouniPas encore d'évaluation

- Intro LFADocument6 pagesIntro LFAsofianne418Pas encore d'évaluation

- Item 1 2 3 4 - SL7000 - Présentation Compteur SL7000 CepelDocument37 pagesItem 1 2 3 4 - SL7000 - Présentation Compteur SL7000 CepelSALVADORPas encore d'évaluation

- Conception VHDL Pour FpgaDocument70 pagesConception VHDL Pour Fpgalahcenkhalifa12Pas encore d'évaluation

- Pic 16F876-77Document73 pagesPic 16F876-77Ayman Brs100% (1)

- Chapitre MicroprocesseurDocument9 pagesChapitre MicroprocesseurMahdi Ben AbdallahPas encore d'évaluation

- CFR - MANUEL-SIMPLIFIE - IR33REF - IR33 DN33 PB00 MD33 IREV PBEV - FR - Rel2.3Document11 pagesCFR - MANUEL-SIMPLIFIE - IR33REF - IR33 DN33 PB00 MD33 IREV PBEV - FR - Rel2.3Pascal NicolletPas encore d'évaluation

- Presentation Du Pic 16f877 PDFDocument22 pagesPresentation Du Pic 16f877 PDFhamzalabbou83% (6)

- L2 Etude de CasDocument49 pagesL2 Etude de CasÇhøčø LãtãPas encore d'évaluation

- Cours 3Document45 pagesCours 3fotsoarolePas encore d'évaluation

- Upload - Résumé Du Cours-Microcontroleurs - 2016-2017Document7 pagesUpload - Résumé Du Cours-Microcontroleurs - 2016-2017Habib Ben AmmarPas encore d'évaluation

- Programmation en Langage D'Assemblage: Cours N°1: Présentation Du CORTEX M3Document32 pagesProgrammation en Langage D'Assemblage: Cours N°1: Présentation Du CORTEX M3Claudia MenendezPas encore d'évaluation

- DS MCP 2023Document4 pagesDS MCP 2023Dhafer MezghaniPas encore d'évaluation

- Correction Production ÉcriteDocument3 pagesCorrection Production ÉcriteDhafer Mezghani100% (2)

- Correction Exercice PIPELINEDocument12 pagesCorrection Exercice PIPELINEDhafer MezghaniPas encore d'évaluation

- Chapitre 4 Cicruicts CombinatoiresDocument3 pagesChapitre 4 Cicruicts CombinatoiresDhafer MezghaniPas encore d'évaluation

- Correction DS MCP 2022Document5 pagesCorrection DS MCP 2022Dhafer MezghaniPas encore d'évaluation

- Fiche Son KDocument1 pageFiche Son KDhafer MezghaniPas encore d'évaluation

- Révision Langue Trimestre 3Document4 pagesRévision Langue Trimestre 3Dhafer MezghaniPas encore d'évaluation

- Correction Pipeline Avec DépendanceDocument6 pagesCorrection Pipeline Avec DépendanceDhafer MezghaniPas encore d'évaluation

- Correction Examen MCP Juin 2021 LEEA2Document4 pagesCorrection Examen MCP Juin 2021 LEEA2Dhafer MezghaniPas encore d'évaluation

- Correction Examen 2022 MCPDocument5 pagesCorrection Examen 2022 MCPDhafer MezghaniPas encore d'évaluation

- TD3 ArchitectureDocument9 pagesTD3 ArchitectureDhafer MezghaniPas encore d'évaluation

- TD 2 Complémentaire SoC MulticyckeDocument10 pagesTD 2 Complémentaire SoC MulticyckeDhafer MezghaniPas encore d'évaluation

- TD1 PeDocument2 pagesTD1 PeDhafer MezghaniPas encore d'évaluation

- TD 3 MCCDocument2 pagesTD 3 MCCDhafer MezghaniPas encore d'évaluation

- Template Fiche Module Pour Cycle Ingénieur Electronique EmbarquéeDocument2 pagesTemplate Fiche Module Pour Cycle Ingénieur Electronique EmbarquéeDhafer MezghaniPas encore d'évaluation

- TD Decodage AdressesDocument10 pagesTD Decodage AdressesDhafer Mezghani100% (1)

- TD ÉlectrocinétiqueDocument3 pagesTD ÉlectrocinétiqueDhafer MezghaniPas encore d'évaluation

- Capteurs de MesureDocument9 pagesCapteurs de MesureDhafer MezghaniPas encore d'évaluation

- TD 1 - ProcDocument1 pageTD 1 - ProcDhafer MezghaniPas encore d'évaluation

- TD Corrigé ARCHI 1Document8 pagesTD Corrigé ARCHI 1Dhafer MezghaniPas encore d'évaluation

- TD 1 AoDocument1 pageTD 1 AoDhafer MezghaniPas encore d'évaluation

- CHAPITRE 4CN (Étudiant)Document8 pagesCHAPITRE 4CN (Étudiant)Dhafer MezghaniPas encore d'évaluation

- Chapitre 1CNDocument10 pagesChapitre 1CNDhafer MezghaniPas encore d'évaluation

- TD N°4 Circuits ArithmétiquesDocument2 pagesTD N°4 Circuits ArithmétiquesDhafer MezghaniPas encore d'évaluation

- CHAPITRE 3CN (Etudiant)Document3 pagesCHAPITRE 3CN (Etudiant)Dhafer MezghaniPas encore d'évaluation

- TD N°2 Systèmes LogiquesDocument2 pagesTD N°2 Systèmes LogiquesDhafer Mezghani100% (1)

- Examen TP1Document2 pagesExamen TP1Dhafer MezghaniPas encore d'évaluation

- Correction Exercices PIPELINE Avec AléasDocument17 pagesCorrection Exercices PIPELINE Avec AléasDhafer Mezghani100% (1)

- Feuille de Présence MPI1BDocument3 pagesFeuille de Présence MPI1BDhafer MezghaniPas encore d'évaluation

- Les Circuits À DiodesDocument11 pagesLes Circuits À DiodesDhafer MezghaniPas encore d'évaluation

- BaseboardDocument2 pagesBaseboardnarcis_hapauPas encore d'évaluation

- These Zaamouche FaresDocument115 pagesThese Zaamouche FaresabfstbmsodPas encore d'évaluation

- Devoir - de - Synthese - N1-1ere - Annee Secondaire-Technologie - Pilote BourghuibaDocument5 pagesDevoir - de - Synthese - N1-1ere - Annee Secondaire-Technologie - Pilote BourghuibaHamami AymenPas encore d'évaluation

- Microscopie À Force ÉlectrostatiqueDocument7 pagesMicroscopie À Force ÉlectrostatiquecairePas encore d'évaluation

- AsservissementsDocument9 pagesAsservissementsRiadh KhenferPas encore d'évaluation

- TP Mas A Distance - MasterDocument5 pagesTP Mas A Distance - MasterSoumaya EL GHAZIPas encore d'évaluation

- TD Mup 8085 Fezari 2018Document35 pagesTD Mup 8085 Fezari 2018koyabePas encore d'évaluation

- Harmony Relais Électromécaniques - RXM4AB2GDDocument7 pagesHarmony Relais Électromécaniques - RXM4AB2GDDumontPas encore d'évaluation

- 03 Java Socket PDFDocument46 pages03 Java Socket PDFFreudeGuilmeraPas encore d'évaluation

- GI2Document5 pagesGI2Omar TriguiPas encore d'évaluation

- DADAMOUSSA Makhloufi PDFDocument79 pagesDADAMOUSSA Makhloufi PDFHortence SiuPas encore d'évaluation

- GHX 308 A 616Document109 pagesGHX 308 A 616Syrine Garneh100% (1)

- Protections Des Installations de Production Raccordées Au Réseau Public de DistributionDocument64 pagesProtections Des Installations de Production Raccordées Au Réseau Public de DistributionBillel SotiPas encore d'évaluation

- Annuaire Photonique & RF Nouvelle Aquitaine 2021Document187 pagesAnnuaire Photonique & RF Nouvelle Aquitaine 2021Paul aloisPas encore d'évaluation

- Ed 07 (FR)Document34 pagesEd 07 (FR)Johnny Diaz VargasPas encore d'évaluation

- Dimensionnement D'une Installation Électrique BT - AALDocument96 pagesDimensionnement D'une Installation Électrique BT - AALDjebien Ahmed Abu AbderrahimPas encore d'évaluation

- Architecture D'emetteur Pour Systèmes de RadiocommunicationDocument127 pagesArchitecture D'emetteur Pour Systèmes de RadiocommunicationandrytahiryPas encore d'évaluation

- CV Ingenieur D EtatDocument1 pageCV Ingenieur D EtatSaadElHafidiPas encore d'évaluation

- Chapitre 6 Transistor Bipolaire en Regime VariableDocument23 pagesChapitre 6 Transistor Bipolaire en Regime VariableWahidBenzPas encore d'évaluation

- 4 Cours MOS RulesDocument4 pages4 Cours MOS RulesWeld MedninePas encore d'évaluation

- Quels Sont Les Différents Types de Moteurs Électriques - ConcepTECDocument4 pagesQuels Sont Les Différents Types de Moteurs Électriques - ConcepTECelkajjalPas encore d'évaluation

- Livre Blanc LiFiDocument18 pagesLivre Blanc LiFiarunPas encore d'évaluation

- IUT GMP BORDEAUX UNC Decoupe Laser Groupe 1-2 2012 2013Document10 pagesIUT GMP BORDEAUX UNC Decoupe Laser Groupe 1-2 2012 2013Valerie MartyPas encore d'évaluation

- Etude Et Réalisation de Rectenna en Utilisant Les Ondes Électromagnétiques Du Réseau Mobile Boussahoua e 0 PDFDocument96 pagesEtude Et Réalisation de Rectenna en Utilisant Les Ondes Électromagnétiques Du Réseau Mobile Boussahoua e 0 PDFissam HadjhamdiPas encore d'évaluation

- CH 5Document84 pagesCH 5Mouhsin RPas encore d'évaluation

- Module Application Retscreen Au PVDocument44 pagesModule Application Retscreen Au PVlhabsPas encore d'évaluation

- Guide - Installation Décodeur TV NumericDocument28 pagesGuide - Installation Décodeur TV NumericGéry LacheryPas encore d'évaluation