Académique Documents

Professionnel Documents

Culture Documents

Cours Microprocesseur PDF

Transféré par

ferradibrTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours Microprocesseur PDF

Transféré par

ferradibrDroits d'auteur :

Formats disponibles

Architecture des systmes

microprocesseurs

Maryam Siadat & Camille Diou

I Introduction

Larchitecture dun ordinateur constitue lensemble des sous-systmes ralisant dif-

frentes fonctionnalits, la manire de les relier et de les faire communiquer.

Au premier sens du terme, une architecture informatique est dnie par des para-

mtres tels que les instructions du microprocesseur, les jeux de registres, la mthodologie

de gestion de la mmoire, et dautres fonctions ...

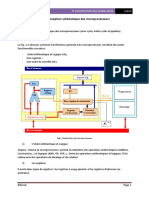

I.1 Larchitecture dun ordinateur simple

Un simple ordinateur est compos de :

mmoire (RAM/ROM) ;

un CPU;

quelques circuits dentre/sortie.

Les trois parties sont connectes par les trois bus (adresse, donnes, contrle) crs

par le CPU. Le CPU est le matre unique dans les ordinateurs simples, et cest lui qui

contrle tout le systme.

La squence des instructions (ou programme) est stocke en mmoire des empla-

cements successifs et en code binaire.

Le rle du CPU se dcompose en quatre tapes :

1. aller chercher linstruction suivante en mmoire cycle de chargement ;

2. la dcoder pour dterminer laction quil doit effectuer ;

3. lexcuter cycle dexcution ;

4. revenir ltape 1.

CPU RAM

ROM

Unit de commande

UAL, registres

Circuits dE/S

PIO, PIA, PPI

ACIA, UART, USART, SIO

timer, CNA, CAN

Mmoire

FIG. I.1: Schma synoptique dun ordinateur simple

1) Lunit centrale : (UC, CPU, MP)

Elle se compose essentiellement de lunit de commande, de lUAL et dun ensemble

de registres. LUC est organise le long dun bus (bus interne du microprocesseur, cf

gure I.2).

Remarque : les registres de lUC nont pas tous la mme taille.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 3

I.1. Larchitecture dun ordinateur simple

Registres

gnraux programme

Pointeur de Registre

dinstruction

Registre

tampon

Registre

dadresse du temps

Controle

UAL

^

Bus interne de lUC

FIG. I.2: Schma synoptique dune unit centrale

1.a) LUAL

Elle permet deffectuer les additions et soustractions binaires, OR, AND, XOR...

Exemple de circuit : 74LS181, UAL 4 bits (cf gure I.3).

A0

A1

A2

A3

B0

B1

B2

B3

CN

M

F0

F1

F2

F3

P

CN

A=B

S3 S2 S1 S0

FIG. I.3: Schma dun 74LS181

Ce circuit ralise des fonctions arithmtiques et logiques sur A et B, avec le rsultat

dans F. Lopration est dtermine par M et par les entres de slection S0, S1, S2, et

S3 :

M=1 16 fonctions logiques ;

m=0 16 fonctions arithmtiques.

Lintrt dune UAL cest quelle peut tre programme avec des instructions bi-

naires : cest un circuit programmable. LUAL est la partie la plus importante dun pro-

cesseur, donc dun ordinateur.

Ralisation dune UAL :

elles sont souvent ralises laide des rseaux logiques programmables (PLA) ;

avec larrive des circuits LSI et VLSI, des ralisations trs structures ont t

possibles laide de MUX (slecteurs de donnes).

Exemple : additionneur complet de 1 bit laide de 2 MUX 3 entres de slection (cf

gure I.4).

Remarques :

1. pour raliser une UAL traitant des mots de n bits, il suft de brancher en cascade

n paires de slecteurs de donnes (exemple additionneur 4 bits) ;

2. pour raliser une autre opration, il suft de changer les entres des MUX.

4 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

D0

D1

D2

D3

D4

D5

D6

D7 a0 a1 a2

D0

D1

D2

D3

D4

D5

D6

D7 a2 a1 a0

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

S Rout

A B Rin

FIG. I.4: Additionneur complet

1.b) Lunit de commande

Son rle est :

denvoyer des signaux de contrle pour connecter les registres au bus ;

de superviser le fonctionnement de lUAL;

de donner des signaux dhorloge lensemble de lordinateur.

Toutes les actions de lunit de commande concernent les cycles de chargement et

dexcution des instructions. Par exemple, il y a besoin de signaux de contrle pour

relier les registres au bus, pour superviser le fonctionnement de lUAL, et pour donner

des signaux dhorloge lensemble de lordinateur. La plupart de ces signaux provient

de la section de contrle de lUC (voir la ralisation des squenceurs).

Cycle de chargement (cf gure I.5) :

Les instructions sont lues une par une, puis dcodes et excutes.

Pour aller chercher une instruction en mmoire, il faut excuter les oprations sui-

vantes :

1. charger le contenu du pointeur de programme dans le registre dadresse mmoire

qui est reli au bus ;

2. demander la mmoire de lire la donne, et de la placer sur le bus (signal read

memory) ;

3. ranger la valeur lue sur le bus de donnes, dans le buffer de lUC;

4. transfrer le buffer dans le registre dinstruction ;

5. incrmenter le pointeur de programme dune unit pour aller chercher linstruction

suivante.

Pour effectuer ces oprations, il faut envoyer un certain nombre de signaux de

contrle aux divers registres de lUC et la mmoire. Par exemple, pour la premire

opration, le systme de contrle doit fermer toutes les sorties de registres en direction

du bus interne, ouvrir la sortie du pointeur de programme en direction du bus, et charger

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 5

I.1. Larchitecture dun ordinateur simple

Pointeur de

programme

Registre

dinstruction

Registres

gnraux

dadresse

mmoire

Registre

UAL

Buffer MMOIRE

Bus dadresse

Bus de donnes

UC

FIG. I.5: Unit de commande

le contenu du bus dans le registre dadresse mmoire. Il faut videmment envoyer tous

ces signaux dans un ordre correct et avec un dcalage temporel correct entre eux.

Cycle dexcution :

Lensemble des oprations prcdentes se rpte chaque cycle de chargement.

Mais, selon larchitecture et la teneur de chaque instruction, la faon dont le cycle dex-

cution se droule est trs variable.

Prenons comme exemple laddition de laccumulateur et dun autre registre avec le

rsultat dans laccumulateur.

Puisque les registres sont dans lUC, la squence dexcution est :

1. transfert du contenu de laccumulateur dans lUAL;

2. transfert du contenu du registre adress vers lautre entre de lUAL;

3. dclenchement de laddition (en envoyant les signaux ncessaires dans lUAL) ;

4. retour du rsultat dans laccumulateur.

Remarque : si une instruction fait appel la mmoire le cycle est plus long.

6 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

1.c) La micro-programmation

On peut raliser le systme de commande laide des techniques classiques portant

sur la logique squentielle (squenceur cbl). Mais il est de plus en plus frquent dop-

rer laide de la micro-programmation (squenceur micro-programm), cest--dire que

lensemble des oprations dcrites prcdemment (cycles de chargement et dexcution)

peuvent tre considres comme un programme qui tourne sur un processeur trs simple.

En programmant ce niveau, on demande que les instructions soient excutes dans un

ordre correct et que chaque instruction donne la combinaison correcte des signaux de

contrle. En fait la section de commande est micro-microprocesseur .

I.2 Les processeurs spcialiss

1) Micro-contrleurs

Ils contiennent un CPU, de la RAM, de la ROM, quelques ports dE/S parallles, des

ports sries, des compteurs programmables (timers), des CAN/CNA, des interfaces pour

rseaux de terrain ...

Ils sont en gnral utiliss pour contrler des simples machines (appareils lectro-

mnagers, lecteurs de carte puce...)

Exemple de circuits :

80C186XX (80186, 16 bits, Intel)

68HC11, 68HC12 (6809, 8 bits, Motorola)

68HC16 (68000, 16 bits, Mototrola)

C167XX (Inneon, ex Siemens)

2) Digital Signal Processor (sorties)

Ce sont des processeurs ddis aux traitements des signaux numriques. Une archi-

tecture particulire leur permet un traitement efcace des fonctions complexes telles que

FFT, convolution, ltrage numrique ...

Exemples :

TMS320 (Texas Instrument)

2100 et 21000 (Analog Device)

56000 (Motorola)

3) Processeurs de traitement dimage

4) Processeurs spcialiss dentres/sorties

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 7

I.2. Les processeurs spcialiss

8 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

II Les diffrentes architectures

II.1 Architecture uniprocesseur

1) Architecture Von Neumann (1946)

Architecture conventionnelle, la plus utilise dans le domaine des ordinateurs. Elle

repose sur quatre entits principales (cf gure II.1) :

UAL Unit dE/S Mmoire Unit de commande

UC

FIG. II.1: Architecture de Von Neumann

Un seul processeur (unit centrale) travaille de manire squentielle sur des infor-

mations en mmoire qui constituent la fois les donnes et les programmes : une seule

unit de commande traitant une seule squence dinstruction (Single Instruction Stream)

et une seule unit dexcution (UAL) traitant une unique squence de donnes (Single

Data Stream). Cette architecture est donc appele SISD (Single Instruction Single Data).

Un bus unique relie les diffrents modules.

Cette architecture commande unique constitue un frein au traitement parallle.

2) Architecture de Harvard (1940, la premire employe pour les ordina-

teurs)

Mmoire de programme Mmoire de donnes

Unit dE/S Unit de commande UAL

UC

FIG. II.2: Architecture de Harvard

Elle est caractrise par la sparation des donnes et programmes en mmoire. Lac-

cs chacun seffectue par un bus spar, diffrent et indpendant. Donc un accs si-

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 9

II.2. Architectures parallles

multan aux instruction et aux donnes est possible, ce qui implique une excution plus

rapide.

Cette architecture est abandonne sur les ordinateurs universels en raison de sa com-

plexit matrielle, mais elle est avantageuse pour les systmes de traitement numrique

de s signaux. Le 4004 (premier processeur Intel) relve de cette architecture, de mme

que la plupart des processeurs DSP.

3) Temps partag ou multitche

Cest lexcution simultane de plusieurs programmes (par exemple compiler un

programme pendant quon travaille sur un manuscrit sous traitement de texte).

Cette possibilit repose sur une technique de commutation rapide entre les diffrents

programmes. Le temps du processeur est alors partag en petits incrments (par exemple

20 ms). Les tches sont excutes les unes aprs les autres, chacune pendant ce temps.

Ce fonctionnement peut tre ralis par un logiciel (par exemple Linux), mais cest plus

efcace lorsque cela est directement gr par lunit centrale.

Inconvnients :

si le processeur ne marche pas, toutes les tches sont en attente ;

il y a saturation si le nombre dutilisateurs ou de tches augmente.

II.2 Architectures parallles

1) Architectures avec cadencement des donnes

UAL UAL UAL

Unit de commande

Mmoire centrale

UC

FIG. II.3: Architecture avec cadencement de donnes

Cette architecture ot de donnes soppose une architecture traditionnelle dite

ot dinstructions. Cette conguration est appele SIMD (Single Instruction Multiple

Data) et ce type de processeur processeur vectoriel .

On peut classer dans cette catgorie les processeurs vectoriels disposant des

instructions vectorielles (exemple dapplication : addition de deux vecteurs en virgule

10 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

ottante). Lunit de commande envoie une instruction toutes les UAL qui excutent

linstruction pas pas sur des donnes locales. Le rseau dinterconnexions permet aux

rsultats dtre envoys vers une autre UAL qui pourra les utiliser comme oprande dans

une instruction suivante. Les processeurs DSP utilisent cette architecture.

2) Architecture multiprocesseurs (MIMD)

Processeur 2 Processeur 1 Processeur n

Mmoire centrale

FIG. II.4: Architecture MIMD

Plusieurs processeurs partagent la mme mmoire.

Chaque unit centrale (processeur) dispose de son propre programme indpendant.

Plusieurs distributions architecturales sont possibles :

architecture centralise (cf gure II.5) :

Microprocesseur

central

Micro 1

Micro 2

Mmoire

centrale

Micro 3

FIG. II.5: Architecture centralise

architecture horizontale (cf gure II.6) :

Micro 1 Micro 2 Micro n

Bus

FIG. II.6: Architecture horizontale

chaque microprocesseur est soit un processeur central, soit un processeur spcia-

lis (E/S par exemple).

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 11

II.2. Architectures parallles

Chaque processeur constitue une ressource pour le systme.

structure hybride (cf gure II.7) :

Micro 1 Micro 2

Mmoire

locale

Mmoire

locale

Mmoire

locale

Micro n

Bus

Mmoire

centrale

FIG. II.7: Architecture hybride

Dans les structures prcdentes la charge du bus (transfert de donnes, communi-

cation entre les processeurs) freine lefcacit de larchitecture multiprocesseurs.

Lintroduction de mmoire locale associe chaque processeur permet dliminer

les accs la mmoire centrale

hirarchie de bus (cf gure II.8) :

Micro 0 Micro 1 Mm. 1 Micro 2 Mm. 2

Bus dE/S

Bus intermodule

FIG. II.8: Hirarchie de bus

Une autre mthode de dcharger le bus consiste raliser une hirarchie de bus.

Celle-ci peut tre tendue aux E/S.

3) Processeur multi-units de traitement

Cette architecture na de sens que si le temps de chargement et de dcodage est faible

par rapport la dure de son excution.

4) Processeur pipeline

Lide est inspire de lorganisation du travail la chane : cette technique permet

deffectuer davantage de travail par unit de temps.

chaque tape de lexcution de linstruction (chargement, dcodage, recherche des

donnes) se fait dans une unit spare :

12 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

Unit de commande

additionneur multiplieur diviseur comparateur

Calcul

logique

Calcul

flottant

Registre

dcalage

Mmoire

centrale

Analyse des instructions

FIG. II.9: Processeur multi-units de traitement

Recherche de linstruction

Analyse de linstruction

Unit de calcul dadresse

Unit de recherche de donnes

Excution de linstruction

Mmoire

centrale

UC

FIG. II.10: Processeur pieline

la premire est charge dans la premire unit ;

la deuxime unit commence dcoder linstruction pendant que la premire tra-

vaille charger la deuxime instruction ;

un peu plus tard, la troisime unit travaille sur le calcul dadresse pendant que

la deuxime unit dcode la deuxime instruction, et que la premire unit charge

linstruction suivante (exemple : IBM 360/195, CDC STAR).

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 13

II.3. Architecture RISC (Reduced Instruction Set Computer

II.3 Architecture RISC (Reduced Instruction Set Computer

Architecture dans la quelle les instructions sont en nombre rduit (chargement, bran-

chement, appel sous-programme) et elle sont frquemment utilises. Le but est dli-

miner les instructions rarement employes et de consacrer les ressources matrielles

excuter les instructions relativement simples en un cycle dhorloge et muler les

autres instructions laide des squences bases sur les instructions lmentaires. On

trouve donc une meilleure performance une vitesse donne (le gain en performance

envisageable est important mais dpend de la qualit du compilateur).

Caractristiques des machines RISC :

1. un cycle dhorloge au maximum pour lexcution dune instruction ;

2. une dpendance pus forte par rapport aux compilateurs ;

3. toutes les instructions ont la mme longueur ;

4. une utilisation systmatique des registres (gnralement plus nombreux que sur

les processeurs CISC) ;

5. squenceur cbl plutt que programm ;

6. une limitation des accs mmoire aux deux oprations LOAD et STORE.

Stations de travail quipes de processeurs architecture RISC : SUN, HP, IBM.

Processeurs RISC : Alpha (DEC), PowerRISC (IBM), SPARC (SUN), PA-RISC (HP).

II.4 Architecture CISC (Complex Instruction Set Computer)

Cest une architecture avec un grand nombre dinstructions. Le processeur doit ex-

cuter des tches complexes par instruction unique. Donc, pour une tche donne, une ma-

chine CISC excute un petit nombre dinstructions mais chacun ncessite un pus grand

nombre de cycles dhorloge (Pentium et PowerPC). Actuellement les deux technologies

convergent : les processeurs CISC (Pentium par exemple) utilisent des instruction de

plus en plus simples et excutent parfois plusieurs instructions en un cycle dhorloge.

14 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

III Les mmoires semi-conducteur

La mmoire contient le progrmme (sous forme dinstructions codes en binaire) et

les donnes (informations utilisables au cours de lexcution).

On trouve la mmoire soit dans un CI soit dans une partie du microprocesseur.

La mmoire est un ensemble de cellules de mme taille (en gnral 8 bits). Chaque

cellule est atteignable par une adresse unique qui lui est propre. On dit alors que la

mmoire est accs alatoire.

lintrieur de chaque circuit mmoire un dcodeur active le mot slectionn, une

logique de contrle dnit le sens des changes. Cette adresse permet tous les sous-

systmes de lordinateur daccder linformation qui y et stocke.

La structure de base (cf gure III.1) :

Mmoire

CS W R

Bus de donnes

Bus dadresse

FIG. III.1: Structure de base dune mmoire

Deux oprations sont possibles : lecture ou criture.

Les caractristiques de choix :

Taille physique, vitesse (environ quelques dizaines de ns), consommation et niveaux

logiques (caractristiques idales : faible prix, vitesse leve).

III.1 Classication des mmoires

1) Mmoires vives : RAM

Elles sont souvent qualies de RAM (Random Access Memory), mais les mmoires

mortes sont galement accs alatoire, donc de type RAM.

Elle ncessite une nergie pour stocker et garder les donnes. Il existe deux types de

mmoires vives : statiques et dynamiques.

1.a) RAM Statique (SRAM)

La ralisation interne est essentiellement faite par une matrice de bascules :

m bascule sde large, o m est la taille du mot ;

2

n

bascules de long, o 2

n

est la capacit en mots de la mmoire.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 15

III.1. Classication des mmoires

Entre Sortie Entre Sortie Entre Sortie Entre Sortie

Mot 0

Mot 1

Mot 2

Mot 2

n

bit 0 bit 1 bit 2 bit m

FIG. III.2: Matrice organise en mots avec slection linaire : 2

n

mots 2

n

lignes, m bits m

colonnes.

Cette ralisation est simple mais elle ncessite un dcodeur interne 2

n

sorties, donc

une surface de boitier importante. Elle a cependant un accs rapide.

Remarque : il existe aussi la mthode de dcodage deux niveaux (two level decoding).

1.b) RAM dynamique (DRAM)

Les 1 et les 0 sont stocks comme une charge lectrique dans un condensateur. Pour

maintenir linformation il faut la rcrire rgulirement (rafrachissement environ toutes

les 2 ms), car le condensateur se dcharge dans les rsistances de fuite.

Une opration de lecture rafrachit une ligne de la mmoire, pa consquent toute la

mmoire est rafrchie en 2

n

lectures.

On peut utiliser des composants tels que des dRAM refresh controller, mais depuis

lutilisation de technologie VLSI, la plupart des DRAM ont leur propre circuit de rafra-

chissement.

Les DRAM sont constitues selon une matrice (2

n

lignes et 2

n

colonnes) dont

ladressage des cellules se fait en deux temps : adressage des lignes puis adressage des

colonnes.

Lavantage des DRAM par rapport aux SRAM est que leur surface est environ quatre

fois plus petite capacit identique.

Exemple de boitier : Intel 2118, 163841 bits, 16 kbits (cf gure III.3).

Remarques :

les DRAM sont des boitiers de x1 bits.

SRAM : il existe des botiers de 64 Mbits congurables en 8, 16 ou 32 bits ;

DRAM : bientt des 16 Mbits.

16 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

A0

A1

A2

A3

A4

A5

A6

5V

0V

Dout

Din

CAS RAS WE

FIG. III.3: Boitier Intel 2118

Actuellement les SRAM sont surtout utilises pour lantmoire et les DRAM pour la

mmoire principale. Il existe :

DRAM FPM (fast page mode asynchrone jusqu 25 ou 33 MHz ;

une certaine priode, la mmoire FPMtait la forme la plus courante de DRAMdans les

ordinateurs. Elle tait si frquente que lon parlait simplement de DRAM , en oubliant

FPM . La technologie de mmoire FPM offrait un avantage sur les prcdentes car

elle permettait un accs plus rapide aux donnes situes sur une mme range.[RAM]

EDO DRAM (extended data out) jusqu 66 MHz ;

Apparue en 1995, la mmoire EDOreprsentait une nouvelle innovation dans ce domaine.

Similaire la FPM, elle comportait pourtant une lgre modication, autorisant des accs

mmoire conscutifs bien plus rapides. Le contrleur de mmoire gagnait du temps en

supprimant quelques tapes dans le processus dadressage. Avec une EDO, ladressage

de la mmoire par la CPU seffectue une vitesse suprieure de 10 15 % par rapport

une FPM.[RAM]

SDRAM : DRAM synchrone jusqu 200 MO/s

Fin 1996, les SDRAM ont commenc quiper les systmes. la diffrence des technolo-

gies antrieures, la SDRAM se synchronise elle-mme avec la CPU. Ainsi, le contrleur

de mmoire connat le cycle dhorloge exact o les donnes seront disponibles. Donc,

la CPU nattend plus entre les accs mmoire. Les puces SDRAM bncient des modes

entrelacement et rafale , qui acclrent galement la recherche en mmoire. Les

modules SDRAM sont disponibles en diffrentes frquences, assurant ainsi la synchroni-

sation avec la vitesse dhorloge du systme o elles sont implantes. Par exemple, une

SDRAM PC66 est cadence 66 MHz, une SDRAM PC100 100 MHz, une SDRAM

PC133 133 MHz, et ainsi de suite... Des valeurs suprieures tels que 200 MHz et 266

MHz sont actuellement en cours de dveloppement.[RAM]

DDR SDRAM : fonctionne sur les deux fronts de lhorloge

La DDR SDRAM reprsente la gnration suivante de la technologie SDRAM. Elle permet

la puce mmoire deffectuer des transactions la fois durant la phase montante et durant

la phase descendante du cycle dhorloge. Par exemple, avec une DDR SDRAM, un bus

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 17

III.1. Classication des mmoires

mmoire 100 ou 133 MHz gre un dbit de donnes rel de 200 MHz ou 266 MHz. Des

systmes dots de DDR SDRAM sont apparus n de lan 2000.[RAM]

RAMBUS

Direct Rambus est une nouvelle norme darchitecture et dinterface de DRAM qui repr-

sente un d par rapport la conguration classique de la mmoire principale. Compare

aux anciennes technologies, Direct Rambus est extraordinairement plus rapide. Elle est

capable de transfrer les donnes une vitesse atteignant 800 MHz via un bus troit (16

bits), appel Direct Rambus Channel. Cette vitesse dhorloge leve est rendue possible

grce un dispositif "double horloge," qui autorise les transactions la fois durant la

phase montante et durant la phase descendante du cycle dhorloge. Donc chaque disposi-

tif de mmoire dun module RDRAM gnre une bande passante atteignant 1,6 giga-octet

par seconde - le double de celle disponible sur les SDRAM 100 MHz courantes.[RAM]

Autres technologies de mmoires [RAM]

ESDRAM : Enhanced SDRAM

An daugmenter la vitesse et lefcacit des modules mmoire standard, certains fabri-

cants ont incorpor une petite quantit de SRAM directement sur la puce, crant ainsi un

cache intgr. Une ESDRAM est donc essentiellement une SDRAM plus une petite quan-

tit de cache SRAM qui autorise un fonctionnement en rafale jusqu 200 MHz. Comme

avec un cache externe, la DRAM place les donnes le plus frquemment utilises dans le

cache SRAM an de rduire les accs la DRAM, moins rapide. Lun des avantages de

la SRAM sur puce est quelle permet la mise en place dun bus plus large entre la SRAM

et la DRAM, augmentant ainsi la bande passante et la vitesse de la DRAM.

FCRAM : Fast Cycle RAM

La FCRAM, dveloppe conjointement par Toshiba et Fujitsu est destine des applica-

tions spciques comme les serveurs volus, les imprimantes ou les systmes de commu-

tation dans les tlcommunications. Elle inclut une segmentation et un pipelinage interne,

qui acclrent les accs alatoires et rduisent la consommation lectrique.

SLDRAM : Synclink DRAM

Bien quelle soit considre comme obsolte aujourdhui, la SLDRAM a t dveloppe

par un groupe de fabricants de DRAM comme variante de la technologie Rambus, en n

dannes 1990.

VCM : Virtual Channel Memory

Dveloppe par NEC, la VCM permet diffrents bancs de mmoire dtablir de ma-

nire autonome une interface avec le contrleur de mmoire, grce un tampon. Il est

ainsi possible dattribuer diffrentes tches systme leurs propres canaux virtuels ;

de plus, les informations concernant une fonction ne partagent pas lespace tampon avec

dautres tches simultanes, ce qui rend le fonctionnement plus efcace.

2) Mmoires mortes : ROM

Elles sont ralises en technologie MOS et bipolaire. Ces mmoire trouvent leur

application dans la conversion de code, a gnration de caractres pour lafchage sous

forme de matrice de points, le stockage de certains programmes systme.

18 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

Elle ne ncessite pas dnergie pour conserver leur information. En gnral, seule la

lecture est possible. Il en existe plusieurs tpes :

ROM : Read only memory

Elles sont programmes en usine et ne peuvent pas tre reprogrammes ;

PROM : Programmable read only memory

Programmables par lutilisateur, elle ne peuvent pas tre reprogrammes ;

EPROM : erasable programmable read only memory. Encore appeles UV-

PROM, elles sont programmables par lutilisateur et effaables par effet photo-

lectrique laide dUV par la fentre place au-dessus du botier.

Remarque : les EPROM sont programmable par octet, mais effaables dans len-

semble. Il existe une variable OTP (one time programmable). Leur capacit va

jusqu 16 Mbits.

Exemple de botier : 2716. Lors de la programmation, il faut des impulsions de 50

ms sur prog (cf gure III.4).

A0

A11

VPP(25V) CE/prog

OE

D0

D7

FIG. III.4: Boitier 2716

EEPROM : Electricaly erasable programmable read only memory.

Elle peut tre efface lectriquement et reprogramme dans lapplication par octet.

Remarque : les RAM sont accessibles bit par bit. Sa capacit atteint 4 Mbits.

Lendurance est limite contrairement celle des RAM qui est innie. Elle est

moins rapide en criture que les RAM.

Flash EPROM :

La mmoire ash est une mmoire semiconducteurs, non volatile et rinscriptible, qui

fonctionne comme la combinaison dune RAM et dun disque dur. La mmoire ash stocke

les bits de donnes dans des cellules de mmoire, comme une DRAM, mais elle fonctionne

comme un disque dur, dans la mesure o les donnes sont conserves en mmoire lorsque

lalimentation lectrique est coupe. En raison de sa vitesse leve, de sa durabilit et de

sa faible consommation, la mmoire ash est idale pour de nombreuses applications -

comme les appareils photos numriques, les tlphones cellulaires, les imprimantes, les

ordinateurs portables, les rcepteurs dondes radio de poche et les dispositifs denregis-

trement sonore.[RAM]

Elle est programmable et effaable lectriquement comme les EEPROM. La seule

diffrence provient de la structure interne et de la technologie utilise qui permet

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 19

III.2. Interface mmoire

un meileur compromis vitesse/capacit.

Les ash sont programmables par octet et effaables soit dans leur ensemble

(comme les EPROM) soit par secteur (secteur > 1 octet). Leur capacit va de 16

128 Mbits en 2002, des capacits de 256 512 Mbits doivent apparatre courant

2003. Il existe des mmoires ash monotension (pour lalimentation de la lecture

et de leffacement) : elles remplaceront peut-tre terme les DRAM.

Remarque gnrale : les ash EPROM prennent actuellement plus de 50% du

march europen des mmoires non volatiles.

FRAM : Ferroelectric RAM.

Elle combine les performances de L/Eillimite des DRAM et la non volatilit. Sa

capacit est de 256 Kbits (trs faible).

PLA : Programmable logic array

Les PLA sont similaires aux ROM mais diffrents par leur structure interne. Ils

permettent de produire des fonctions logiques spciales. Ils sont mask program-

mable (MPLA) ou eld programmable (FPLA). Le PLA de base possde deux

matrices ET et OU permettant de raliser directement des sommes de produit :

matrice ET en entre, matrice OU en sortie.

III.2 Interface mmoire

Les lignes de donnes sont bidet 3 tats (sinon conit sur le bus) : lors de la lecture

seulement un des CI mmoire doit tre valid un instant donn.

Les cirucits INS8202 ou 74LS244 sont des octuples buffer/drivers de lignes et per-

mettent dinterfacer les lignes de donnes.

Les dcodeurs, qui permettent de dcoder les lignes dadresse, sont un autre type de

circuits dinterface mmoire.

III.3 Les diffrents type de mmoires vives dun ordinateur

On distingue plusieurs types de mmoires vives en fonction de :

leur utilisation ;

leur vitesse ;

leur mode dadressage ;

leur mode daccs aux donnes.

1) Les registres

Un registre est un ensemble ordonn de bascules dans lequel on peut crire puis

mmoriser un mot binaire. Ce sont des mmoires particulires car linformation ny est

pas adresse.

Les registres se situent lintrieur de lunit centrale, alors que la mmoire centrale

forme un bloc fonctionnel part entire en dehors de lunit centrale. Ils offrent un temps

daccs en lecture/criture beaucoup plus faible (rapport 10) que la mmoire centrale.

20 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

Conceptuellement, les registres et mmoire centrale sont semblables : ce sont le lieu

dimplantation dans la machine, la capacit de stockage et le temps daccs aux infor-

mations quils contiennent qui les diffrencient.

les registres accessibles aux programmeurs constituent une mmoire trs petite

(en gnral 16 registres dun mot) compars aux mmoires centrales, mais ils sont

beaucoup plus rapide.

au sein de la couche microprogramme, les registres sont utiliss pour assurer le

stockage dinformations ncessaires lexcution en cours de traitement.

2) Les piles

piles FIFO : elles sont ralises partir dun ensemble de registres dont laccs

aux donnesseffectue de manire squentielle sans laide dune adresse.

La premire information mmorise sera la premire lue. Une lecture est possible

tant que toutes informations nont pas t lues. Une criture est possible tant que

la pile nest pas sature.

Application : utilisation dune FIFO asynchrone avec deux horloges pour adapter

lchange dinformation entre deux systmes de vitesse diffrente.

Exemple : transmission de lordinateur vers limprimante en adaptant la vitesse de

communication (cf gure III.5).

FIFO

FIG. III.5: Adaptation de la vitessede communication par une FIFO

Remarque : il y a une diffrence importante entre une pile FIFO et un registre

dcalage conventionnel.

piles FILO : ces piles sont en gnral implantes sous forme logicielle.

La mmoire utilise est une RAMdont ladresse est gnre par un pointeur qui est

incrment ou dcrment selon lcriture ou la lecture des informations. Ces piles

sont utilises par le CPU pour mmoriser rapidement un ensemble de donnes ou

dadresses (retour de sous-programmes par exemple).

III.4 Mmoire centrale

Cest la zone de stockage des donnes et des programmes. Elle peut tre consid-

re comme un ensemble de registres accessibles individuellement grce une adresse

spcique : mmoire accs alatoire.

La capacit de la mmoire centrale est plus ou moins importante selon le systme. Ele

est en gnral forme de plusieurs botiers de RAM : cest une association de circuits en

parallle pour crer la longueur du mot dsir (traitable par le processeur) et de circuits

en srie pour crer la capacit dsire.

Exemple : constitution de 6 kmots de 8 bits laide de botiers de 2k4 bits.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 21

III.5. La mmoire cache, ou antmmoire

III.5 La mmoire cache, ou antmmoire

Les microprocesseurs 8 et 16 bits travaillent des vitesses environ gales aux temps

daccs mmoire : la performance dun systme tait donc due en gnral aux proces-

suers eux-mmes.

Le problme majeur avec lapparition des microprocesseurs rapides est de synchro-

niser laccs la mmoire avec la viesse du processeur (la vitesse des microprocesseur

augmente vite alors que celle des mmoires volue lentement). Autrement dit, il faut

pouvoir satisfaire assez vite les demandes en criture/lecture en mmoire pour ne pas

laisser le processeur tourner vide. La solution est la mmoire cache.

Principe : on place, entre le processeur et la mmoire centrale classique, quelques cir-

cuits de mmoire ultra-rapide (type SRAM) mais coteux ; ce bloc renfermera les l-

ments les plus utiliss lors dune tche (cf gure III.6).

Controleur de cache

^

cache Processeur rapide Mmoire centrale

FIG. III.6: Principe de la mmoire cache

Chaque fois que le processeur doit lire une donne, il commence par la cherche

dans la mmoire cache. Si elle sy trouve, il ny a alors aucune attente, sinon le systme

charge dans le cache non seulement la donne demande mais aussi toute la zone envi-

ronnante de la mmoire centrale. Grce cela la requte suivante du processeur a toutes

les chances dtre effectivemetn dans le cache (il y a duplication de linformation mais

ceci est transparent pour lutilisateur).

Remarque 1 : certains processeurs ont une mmoire cache interne (486 : 8 ko, Pentium :

16 ko, Celeron 32 ko L1 + 128 ko L2, Pentium III : 32 ko L1 + 256 ko L2, Athlon : 128

ko L1 + 256 ko L2, Pentium 4 : 32 ko L1 + 256 ko L2)

Remarque 1bis : le Pentium 4 possde en fait un chache L1 de 8 ko associ un cahce

de trace dexcution L1 de 12000 opration : on a donc un cache donnes et un cache

instructions distincts. Le cache L2 est de 256 ou 512 ko selon la version.

Remarque 2 : le 486 travaille en 32 bits (interne et externe) et le pentium en 64 bits

interne et 32 bits externe. Pour le Pentium certains constructeur ont conu un bus sur

64 bits pour relier le cache et le contrleur de cache ; dautres ont adapt des solutions

existantes et transfrent les 64 bits en 2 fois 32 bits.

Remarque 3 : le Pentium pose un autre problme : ce circuit est si rapide que le temps

de chargement du cache avec lensemble des donnes prsentes en mmoire vive devient

lui aussi critique. Quelques constructeurs proposent de relier cache et RAM par un bus

22 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

de 128 bits.

Structure gnrale dun cache :

La mmoire cache nest pas adresse comme toutes les mmoires, cest--dire en

faisant correspondre une adresse une cellule mmoire.

Dans un cache sont ranges en mme temps les donnes ainsi que leur adresse (la

cl) correspondante dans la mmoire centrale (ou seulement une partie).

Ce type de mmoire, appel mmoire associative , opre selon deux tapes :

test de prsence dadresse dans la mmoire adresse ;

si oui, mettre la donne sur le bus de donne.

Remarque : la recherche par cl (adresse) dans la mmoire associative ne seffectue pas

de manire squentielle, mais en parallle sur toutes les cases de la mmoire associative.

En un accs, on sait si linstruction cherche se trouve ou non dans lantmmoire.

Structure gnrale dun cache : recherche par clef (cf gure III.7).

Mmoire

adresse

Mmoire

donne

Bus donne

Bus adresse

Mmoire associative

FIG. III.7: Recherche par clef dans une mmoire cache

Structure gnrale dun cache : recherche par adresse (cf gure III.8).

Le contrleur de cache 80385 :

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 23

III.6. Mmoire virtuelle

adresse Information

contenue

cette

adresse

Mmoire normale

(recherche par adresse)

FIG. III.8: Recherche par adresse dans une mmoire centrale

La performance de mmoire cache se mesure laide du taux de succs (nombre dac-

cs fructueux lantmmoire divis par le nombre daccs total lantmmoire). Il

est obtenu exprimentalement et parfois dpasse 90%. Il dpend de la taille de lantm-

moire et de la localit du programme.

III.6 Mmoire virtuelle

Pour permettre lutilisation de programmes volumineux et multi-utilisateurs, on fait

appel un systme de gestion de la mmoire appel mmoire virtuelle .

Elle permet de disposer de plus de mmoire que nen offrent les circuits RAM de

lordinateur, lide tant de sparer les concepts de la mmoire adressable et de la m-

moire (RAM) disponible.

Fonctionnement : les parties de programmes ou de donnes qui excdent la mmoire de

lordinateur sont stockes sur une mmoire de masse (auxiliaire) et sont recharges dans

la RAM quand cela est ncessaire.

Rappel : hirarchie de la mmoire dans un ordi :

registres ;

cache ;

mmoire principale (RAM) ;

mmoire auxiliaire (disque dur).

1) Principe de la mmoire virtuelle

Cela consiste autoriser lexcution dun processus dont la capacit mmoire est

suprieur la RAM disponible.

Le dispositif pour la gestion de la mmoire virtuelle se compose de la RAM et dune

mmoire de masse (exemple : disque).

Exemple : soit un systme 16 lignes dadresse, donc de 64 ko despace adressable, mais

avec seulement 4 ko de mmoire centrale (RAM). Si le programme log dans les 4 ko

24 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

fait appel un processus dont ladresse est hors des 4 ko, alors un dfaut sera dtect. Le

processeur va alors cherche un bloc de programme dans la mmoire auxiliaire et le place

dans la zone disponible de la RAM. ce moment, ladresse dappel ne correspond

toujours aucun programme. Il faut donc par une mthode de table, raliser une translation

des adresses an que ladresse spcie rentre dans le cadre des adresses disponibles

cest--dire les adresses RAM (cf gure III.9).

de 4 k

auxiliaire

principale

Mmoire

Mmoire

FIG. III.9: Principe de la mmoire virtuelle

Remarque : le principe de la mmoire virtuelle peut tre compar au principe de la

mmoire cache.

2) Pagination

La pagination permet la gestion de la mmoire virtuelle. Elle consiste en une frag-

mentation de la mmoire auxiliaire en blocs de dimensions xes appeles pages .

Chaque page est charge en mmoire centrale ds quelle est appele par un processus.

Elle sera alors implante une adresse disponible qui sera rfrence dans une table de

processus (remarque : la mmoire centrale est aussi divise en pages, cf gures III.10 et

III.11).

La gestion de la mmoire virtuelle est ralise par le systme dexploitation qui ex-

cutera les instructions suivantes :

lappel de la page auxiliare ;

son implantation en mmoire principale ;

la mise jour de la table des pages.

Cette mthode de gestion est transparente pour lutilisateur (contrairement au prin-

cipe de la segmentation). Le programmeur peut travailler comme si lensemble de son

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 25

III.6. Mmoire virtuelle

page 0

page 1

page 2

page 15

page 0

page i

page j

page 2

16 pages de 4 k

8 pages de 4 k

Espace adressable

virtuel de 64 k

Mmoire principale

de 32 k

FIG. III.10: Exemple de pagination

programme tait constitu dune adresse linaire.

La mmoire virtuelle et la mmoire cache ont un aspect dynamique : cest sur de-

mande instantane (non planie) que le bloc dinformation est amen dans le niveau

infrieur. La mmoire centrale est comme une mmoire cache vis vis de la mmoire

virtuelle.

3) Segmentation

Dans ce cas la fragmentation de la mmoire est effectue en zones de tailles variables

contenant en gnral des entits homognes (tableaux, piles, programmes ...)

La segmentation est galement gr par une mmoire topologique qui prcise la

localisation des segments, mais aussi leur taille et leur prsence ou non en mmoire

principale.

26 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

1 100

page 0

page 1

page 2

page 15

adresse de la page en mmoire secondaire

1 : la page est en

mmoire physique

0 : elle ny est pas

N de la page relle

dans laquelle cette

page virtuelle est

placee (si elle est en

mmoire principale)

FIG. III.11: Fonctionnement dune mmoire topologique

Table

des

symboles

Seg 0

0

20 k

Texte

source

Seg 1

0

12 k

Arbre

syntaxique

Seg 2

0

16 k

Constante

Seg 3

0

8 k

Pile

Seg 4

0

12 k

FIG. III.12: Exemple de segmentation utilise par un compilateur

Remarque : chaque segment est gr indpendamment des autres.

4) Gestion de la mmoire virtuelle

Nous avons vu que la mmoire virtuelle est gre par lintermdiaire dune mmoire

topologique qui ralise le transcodage.

Il y a un va-et-vient des pages entre la mmoire principale et la mmoire secondaire

durant lexcution dun programme. Si le contenu dune page nest pas modi, il nest

pas ncessaire de la rcrire lorsquelle doit tre retire de la mmoire principale. Dans

le cas contraire, il y a rcriture (et donc ncessit de mmoriser si il y a eu ou pas eu de

modication).

En gnral, un systme utilisant la mmoire virtuelle travaille en multiprogramma-

tion, cest--dire avec plusieurs processus activables. Dans ce cas, chaque processus

correspond une table de transcodage.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 27

III.7. DMA (Direct memory access)

III.7 DMA (Direct memory access)

Le transfert de donnes entre un priphrique et la mmoire se fait souvent par bloc

de caractres. Chaque transfert de caractre ncessite une intervention du processeur,

donc une perte de temps pour le processeur, mme en mode interruption .

La solution est donc de remplacer le traitement logiciel par un traitement matriel,

en utilisant un circuit spcialis : le contrleur DMA.

I/O CPU Mmoire

HALT HALTA

DMA

FIG. III.13: Principe du DMA

Les contrleurs DMA sont assez coteux. Il existe plusieurs philosophies de DMA;

par exemple, un DMAC

1

peut suspendre le processeur, larrter, voler des cycles m-

moire au processeur, ou encore rallonger les priodes dhorloge.

1) Matriel pour la gestion mmoire

La ralisation des outils de gestion mmoire requiert de nombreux lments mat-

riels. Ceci peut inclure les mmoires associatives, les circuits de transformation dadresse

et les mmoires rapides pour les tables de pages. De tels quipements sont disponibles

dans de nombreux systmes.

Pour les micro-ordinateurs, ce matriel est fourni gnralement sous forme dun cir-

cuit intgr compatible avec le processeur utilis (le chipset). De tels CI acceptent les

adresses logiques du processeur et gnrent les adresses physiques en utilisant leurs

tables internes. Des tables spares peuvent tre fournies pour les espaces utilisateurs

et les espaces systme. Le contenu de ces tables qui peuvent donner des informations

de protection et de droit daccs est charg par le processeur.

La plupart des processeurs 16 et 32 bits disposent de circuits de gestion mmoire.

Remarques gnrales :

1

Direct memory access controller : contrleur daccs direct la mmoire, ou contrleur DMA

28 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

AD0AD15

ALE

Controleur DMA

^

controle

Bus de

^

Bus de

donnes

Mmoire

Priphrique

Latch

Adresse

IOR IOW MEMW MEMR

HOLDA

HOLD

FIG. III.14: Fonctionnement du DMA

La mmoire principale est lun des composants principaux des ordinateurs : leur

taille et leur vitesse xent la capacit des ordinateurs.

La mmoire cache est ralise en technologie bipolaire, alors que la mmoire prin-

cipale en technologie CMOS (cot plus faible).

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 29

III.7. DMA (Direct memory access)

30 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

IV Le processeur

Rle dans lordinateur : interprte et excute les instructions dun programme mmoris

en mmoire centrale.

Il se dcompose en deux grandes entits :

le squenceur : automate excutant de faon rptitive les squences de :

1. recherche dinstruction ;

2. dcodage de linstruction ;

3. excution de linstruction.

le chemin de donnes : lensemble des composants et moyens emprunts par une

information au cours du traitement (registres, mmoire, ALU, bus ...). Le chemin

de donnes est aussi appel la partie oprative.

IV.1 Le squenceur

Le systme apte raliser une succession dvnements an de parvenir un traite-

ment dsir sur une ou plusieurs donnes ou dclencher des actions de commande dun

processus.

Deux problmes se posent lors de llaboration dun systme squentiel :

1. prsentation du systme (pour diter et simuler son fonctionnement) ;

2. ralisation pratique.

Pour la prsentation dun systme squentiel on dispose de plusieurs mthodes :

GRAFCET, labor en 1977 ;

rseaux de Petri, labors en 1970 ;

graphes cartsiens ou organigrammes, labors en 1970.

1) GRAFCET (graphe tape-transition)

Cest une reprsentation dun systme squentiel base sur lalternance tape-

transition : une tape suit une transition et inversement.

1.a) Reprsentation

Chaque tape est reprsente par un carr dans lequel est spci un symbole associ

ltape (en gnral un numro). chaque tape est associe un rectangle pour prciser

laction correspondante.

Remarque : une tape active peut tre repre par un .

La transition franchir est reprsente par un segment plac sur la liaison entre deux

tapes.

Remarque : ct de ce segment on dnit une expression (en gnral logique) qui

reprsente la validit de la transition.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 31

IV.1. Le squenceur

1 Activer signal E

FIG. IV.1: Reprsentation dune tape

3

4

ab+d

FIG. IV.2: Reprsentation dune transition

Cette transition est appele rceptivit , elle peut tre fonction de :

ltat des variables dentre ;

lvolution de ces variables (front montant ou descendant) ;

lactivit dtapes ;

ltat des variables internes (compteur, horloge).

1.b) Les rgles dvolution rgissant le fonctionnement

Rgle 1 : une tape dinitialisation prcise le dbut du fonctionnement.

0 Conditions initiales

FIG. IV.3: Reprsentation dune condition initiale

Rgle 2 : une transition ne peut tre franchie que lorsque toutes les tapes imm-

diatement prcdentes sont actives et que la rceptivit (la transition) est vraie.

Rgle 3 : le franchissement dune transition entrane lactivation de toutes les

tapes immdiatement suivantes et la dsactivation des tapes immdiatement pr-

cdentes.

Rgle 4 : si au cours du fonctionnement une mme tape doit tre dsactive et

active simultanment, elle reste active.

32 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

4 est valide

si 3 est active

et si G est vrai

3

4

G=ab

FIG. IV.4: Condition de franchissement dune transition

1.c) Les diffrents cas de gures possibles

La gure ci-dessous prsente les diffrents cas de gure de la slection de squence

dun GRAFCET.

les divergences en OU les divergences en ET

ab ab

les convergences en OU les convergences en ET

d c

FIG. IV.5: Les diffrents types de divergences et convergences

1.d) Exemple : systme de transfert de matriaux par chariot

Le systme se compose dune trmie dont lactivation seffectue par un actionneur

T durant le temps ncessaire pour le remplissage dni par le capteur P. Le chariot

peut se dplacer gauche et droite laide des moteurs G et D. Les capteurs f et

d dnissent la localisation du chariot (f : n, d : dbut). Un actionneur V permet de

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 33

IV.1. Le squenceur

verser les matriaux dans le prcipice. Le bouton m ralise la mise en route du systme.

d f

m

FIG. IV.6: Exemple dutilisation du grafcet : tche automatiser

Prsenter cet exemple par un grafcet.

0

1

2

3

4

T.m

p

f.v

p

d

verser

moteur G

moteur D

remplir

v

FIG. IV.7: Exemple dutilisation du grafcet

2) Lorganigramme

Comme le GRAFCET, lorganigramme est une mthode de reprsentation dune

suite squentielle dactions par un graphique symbolique.

34 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

les actions sont dcrites dans un rectangle ;

les suites conditionnelles sont reprsentes par des gures plusieurs sorties (lo-

sange ou hexagone) ;

dautres symboles sont utiliss pour des descriptions de sous-programmes, des

tapes dinitialisation, etc.

Exemple : prsentation de lexemple prcdent par un organigramme.

3) Comparaison entre les deux mthodes

Le GRAFCET permet lactivation de plusieurs branches simultanment, ce que lor-

ganigramme exclus. Un tel mode de fonctionnement demande lcriture de plusieurs

organigrammes synchroniss par des variables secondaires.

IV.2 Ralisation pratique des circuits squentiels dnis par

un GRAFCET ou un organigramme

1) Les squenceurs asynchrones

Un systme volution squentielle se compose dun certian nombre dtapes au

cours desquelles les actions sont stabels, ce qui se traduit par un phnomne de mmoire

(circuits utilisables : bascules D, RS, JK, cf gure IV.8).

Pour respecter les rgles du GRAFCET, une tape (mmoire) est active si la m-

moire prcdente est active et si la rceptivit associe est vraie.

Q S

R

Etape en cours

Etape suivante

Rceptivit

Etape prcdente

FIG. IV.8: Ralisation dun GRAFCET laide de logique asynchrone

La dsactivation dune tape en cours est ralise par lactivation de ltape suivante,

par action sur lentre R.

Exemple :

Les gures IV.9 et IV.10 prsentent un GRAFCET implanter et le schma logique

de son implantation, respectivement.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 35

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

0

1

2 3

4

5

A

C A

B

C

b.d

b.c

b

a

FIG. IV.9: GRAFCET implanter laide dun circuit logique asynchrone

0

bc

2

3

a

1

a b

bd

A A

C

C

B

5

4

FIG. IV.10: Schma lectrique associ au GRAFCET prcdent

36 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

2) Les squenceurs synchrones cbls

il sagit de squenceurs synchrones raliss par le cblage de circuits logiques

voluant de faon synchrone sous la commande dune horloge.

le squenceur tudi prcdemment a une volution asynchrone (une tape est

active ds que les rceptivits sont vraies) : les tapes surviennent de manire

alatoire et un tel circuit est trs sensible aux parasites.

solution : synchroniser chaque bascule sur un front dhorloge : squenceur syn-

chrone.

2.a) Expos de la mthode

Les activation et dsactivation associes devant tre simultanes, on prend la mme

fonction logique pour lactivation des modules o lon va et la dsactivation des modules

que lon quitte.

Exemple :

b

a

n1

n

n+1

K

n1

= X

n1

.a

J

n

= X

n1

.a

K

n

= J

n+1

= X

n

.b

K

n+1

= J

n+2

=

FIG. IV.11: GRAFCET implanter ...

J

K

Q

H

n1

n1

n1

a

n1

X

J

K

H

X

n

n

Q

n

n

b

J

K

Q

H

X

n+1

n+1

n+1

n+1

FIG. IV.12: ... et son implantation laide de logique synchrone

Exercice : crire les expressions des commandes des bascules JKT ralisant le GRAF-

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 37

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

CET suivant :

c

c b

3

4

7

ab

c

m

6

b

5 2

d

1

m

0

J

0

= X

6

.m K

0

= J

1

J

1

= X

0

.m K

1

= J

2

+J

5

J

2

= X

1

.a.b K

2

= J

3

= J

8

J

3

= X

2

.c K

3

= J

4

J

4

= X

3

.c K

4

= J

6

J

5

= X

1

.b K

5

= J

6

J

6

= X

4

.X

8

.c.b +X

5

.d K

6

= J

0

J

7

= X

2

.c = J

3

K

7

= J

6

FIG. IV.13: Exemple de GRAFCET

2.b) Ralisation partir des compteurs-dcodeurs

Lorsque le nombre dtapes est petit ( infrieur 4), on peut affecter une bascule

chaque tape (le cblage reste de dimension raisonnable). Si le nombre dtapes aug-

mente (suprieur 8), on limite laccroissement du cblage en utilisant un registre comp-

teur et un dcodeur.

Plusieurs cas de gure traiter :

enchanement dtapes : en faisant compter le compteur, on peut reprsenter 2

n

38 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

2 = 16 sorties (nombre dtages)

4

Compteur (n bascules)

0 1 2 12 13 14 15

entres de chargement

entre du

comptage

FIG. IV.14: Ralisation dun squenceur laide dun compteur

tapes successives, de numro K, K + 1, K + 2,

Par exemple, soit le compteur dans ltat K = 7, seule la sortie 7 du dcodeur

est active, et elle commande les actions raliser durant cette tape. Lorsque

lvolution du squenceur fait passer le compteur dans ltat K + 1 = 8, la sortie

7 est dsactive ainsi que laction de ltape 7, et laction de ltape 8 est active.

tests et sauts dtapes (transitions conditionnelles)

test : le compteur doit patiner tant que la condition nest pas vraie ;

saut : en forant le compteur une valeur comprise entre 0 et 2

n1

, on peut

passer de nimporte quelle tape de numro i une autre de numro j.

4

2

a vrai

N

4

2

a

LOAD

compteur

codage

dcodage

a

entres de

chargement

H

GS

sortie 4

entre 2

FIG. IV.15: GS indique si une entre du codeur est active ou non

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 39

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

activation de plusieurs branches : lactivation simultane de plusieurs tats du

compteur est impossible. Or, la traduction dun GRAFCET en organigramme n-

cessite autant dorganigrammes que de branches actives simultanment, synchro-

niss par des variables secondaires : introduction de variable ssecondaires (telle

que start ag, end ag).

N

O

Start Flag

Start Flag

RAZ

SET

End Flag

a

squenceur principal

secondaire

squenceur

End Flag

O

N

End Flag

RAZ

Start Flag

SET

O

N

a

squenceur principal squenceur secondaire

FIG. IV.16: Activation de plusieurs branches laide de deux squenceurs

avec :

R

S

Q

Flag

Start

RAZ

SET

R

S

Q

Flag

RAZ

SET

End

FIG. IV.17: Gnration des signaux Start Flag et End Flag

40 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

2.c) Schma global du squenceru synchrone cbl

2.d) Exemple dun squenceur cbl

Ralisation dun multiplieur 8 bits par 8 bits sign en complment deux. Le rsultat

est donn sous forme de module et signe.

La partie oprative contient des circuits tels que :

des registres universels aussurant le chargement, le dcalage droite et gauche,

commands par 2 bits S1 et S2 ;

S1 S2

0 0 rien

0 1 dcalage droite

1 0 dcalage gauche

1 1 chargement

un registre rsultat de 15 bits pour le module et 1 bit pour le signe, valid sur front ;

une UAL sur 16 bits dont la fonction excuter est code sur 4 bits S

3

, S

2

, S

1

, et

S

0

:

S3 S2 S1 S0

A 0 0 0 0

A+1 1 1 1 1

zro 0 0 1 1

A+B 1 0 0 1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

un compteur de type 74160

PT LOAD

0 1 comptage invalid

X 0 chargement synchrone

1 1 comptage valid

On dispose du circuit de la partie oprative. Il est reprsent sur le schma suivant :

la partie oprative est le circuit sur lequel va tre ralise lopration dsire ;

au dpart, nous supposons que :

OP1 Reg1 (multiplicande)

OP2 Reg3 (multiplicateur)

Deux oprations sont effectuer :

validation du signe du rsultat et transformer les oprandes ngatifs en valeurs

positives (par le complment deux) ;

ensuite, ralisation de la multiplication.

Algorithme 8 bits 8 bits

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 41

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

Le multiplicateur est analys bit par bit partir du LSB. Sil baut 1, le multiplicande

est additionn au rsultat puis dcal gauche, sinon, il est seulement dcal gauche.

Exemple :

1 1 0 0 0 1 0 1

0 0 1 1 0 1 0 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 rsultat intermdiaire initialis 0

0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 bit 0 = 1

0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 R0

0 0 0 0 0 0 1 1 0 0 0 1 0 1 bit 2 = 1

0 0 0 0 0 0 1 1 1 1 0 1 1 0 0 1 R2

0 0 0 0 1 1 0 0 0 1 0 1 bit 4 = 1

0 0 0 1 0 0 0 0 0 0 1 0 1 0 0 1 R4

0 0 0 1 1 0 0 0 1 0 1 bit 5 = 1

0 0 1 0 1 0 0 0 1 1 0 0 1 0 0 1 R5 = rsultat nal, n du traitement

Organigramme

Reg1 et Reg2 contiennent OP1 sur deux octets pour permettre laddition des rsultats

intermdiaires sur deux octets.

On remarque que certaines actions sont actives sur des niveaux et dautres sur des

fronts. Pour viter les problmes de synchronisme, une horloge plusieurs phases est uti-

lise (pour cet exemple, deux phases dhorloge sont utilises :

2

est associ LOADR

et

1

active le squenceur).

Aprs la numrotation des tapes, il faut raliser le calcul des actions, le calcul des

validations chargement et comptage, et le calcul des adresses de chargement.

(1) Calcul des actions

RAZ start ag = E17

SET end ag = E17

SIGN = E1

S11 = E16 + E4 + E6 VAL1 = E3 + E5 + E15

S12 = E16 VAL2 = E15

S21 = E16 VAL3 = E8 + E10

S22 = E16 VALR = E4 + E6 + E11 + E9

S31 = E9 + E11 LOADR = E3 + E5 + E8 + E10 + E12 + E15

S32 = E16

Les actions (fonctions) de lALU :

42 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

S3 S2 S1 S0

A 0 0 0 0 E3 + E8

A+1 1 1 1 1 E5 + E10

zro 0 0 1 1 E12

A+B 1 0 0 1 E15

S3 = E5 + E10 + E15

S2 = E5 + E10 +

S1 = E5 + E10 + E12

S0 = E5 + E10 + E12 + E15

(2) Calcul des validations chargement et comptage

Lorganigramme comporte 17 tapes, ce qui nous impose de prendre un compteur de

5 bits au minimum.

Le compteur dont nous disposons possde deux entres LOAD et PT.

Le chargement doit tre valid (soit LOAD=0) chaque fois quil y a un saut dtape.

Calcul du patinage (arrt du comptage) : patinage si PT = E0.start ag

(3) Calcul des adresses de chargement

Dnition des lignes de chargement du compteur A4, A3, A2, A1, A0.

A4 A3 A2 A1 A0

0 0 1 1 1 E2 saut en E7

0 1 1 0 0 E7 saut en E12

1 0 0 0 1 E13 saut en E17

1 0 0 0 0 E14 saut en E16

0 0 0 0 0 E17 saut en E0

A0 = E2 + E13

A1 = E2

A2 = E2 + E17

A3 = E17

A4 = E13 + E14

3) Le squenceur microprogramm (microprogrammation)

Tout circuit squentiel est constitu dun circuit combinatoire reboucl sur lui-mme

travers un autre circuit.

Pour un squenceur cbl, le circuit combinatoire se compose de fonctions logiques

(constitues de circuits cbls) de manire raliser une succession dactions bien d-

termines et inchanges.

On peut raliser le systme de contrle laide de ces techniques classiques, mais

il est de plus en plus frquent doprer lide de la microprogrammation (le logiciel

associ reoit le nom de rmware).

3.a) Constitution dun squenceur microprogramm

comme dans tout systme programm, une mmoire contient la suite squentielle

des oprations effectuer (mmoire de contrle).

si nous regardons les reprsentations dun enchanement squentiel (GRAFCET,

organigramme), nous voyons qu chaque tape stable sont associes des informa-

tions telles que :

numro ou code ou adresse de ltape en cours ;

numro ou code ou adresse de ltape suivante ;

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 43

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

typede transition avec ltape suivante : inconditionnelle ou conditionnelle avec

les conditions associes ;

actions associes ltape.

en fait, chaque tape est reprsente par une che dcrivant les informations pr-

cdentes. Lensemble du chier constitue le microprogramme et chaque che une

microinstruction.

Les microinstructions dnissent tous les signaux de contrle pour le chemin de

donnes et ont la possibilit de dcider conditionnellement de linstruction excuter

ltape suivante.

Linvention de la microprogrammation permet de modier le jeu dinstructions en

changeant le contenu de la mmoire de contrle sans modier limplantation matrielle.

Schma de lorganisation du squencement de microinstructions :

3.b) Les composants du squenceur

(1) Circuit de dcodage dadresse

Un dcodeur est utilis pour gnrer ladresse de dbut dune microroutine donne

sur la base du code-oprtion contenu dans le registre dinstruction (IR).

(2) C.A.R.

Le CAR est un circuit apte mmoriser le numro (ladresse, le code) de ltape en

cours.

Il peut tre constitu de deux types de circuits :

un simple registre (ncessite un chargement obligatoire chaque fois) ;

un compteur.

Dans les deux cas, les trois cas de gure suivants devront tre excutables :

suite squentielle

registre : chargement de ladresse suivante ;

compteur : validation du comptage.

patinage

registre : ne pas charger ;

compteur : invalider le compteur.

branchement

registre : chargement de la nouvelle adresse ;

compteur : chargement de la nouvelle adresse.

(3) Mmoire de microprogramme

La mmoire de microprogramme est le circuit qui contient un code qui correspond

une tape donne. En fait, cette mmoire est un circuit combiatoire qui fournit un

ensemble dtats binaires en sortie en fonction dun ensemble dtats en entre (adresse).

Cette logique pourrait tre ralise laide de circuits logiques cbls, mais ceci

serait contraire leffet attendu, cest--dire la souplesse de la programmation.

44 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

Le circuits programmables sont :

les mmoires ;

les PLA.

Lorganisation des champs des microinstructions repose sur deux types :

la microprogrammation horizontale ;

la microprogrammation verticale.

Exemple de taille de la mmoire de microprogrammation : 4K microinstructions

avec 50 80 bits par microinstruction.

La microprogrammation horizontale

Ce type de codage de la microinstruction consiste employer un bit par micro-

commande, cest--dire affecter un bit particulier une action particulire et toujours

la mme. Donc, autant de bits que de bits de commande, ce qui aboutit des instructions

longues. Lintrt est que les actions sont effectues simultanment.

La microprogrammation verticale

On utilise un codage maximal des microcommandes. Seuls deux champs sont pr-

sents simultanment :

un champ dnissant le type du champ complmentaire ;

un champ complmentaire dnissant les microcommandes (concernant les ac-

tions, les adresses et les conditions).

champ complmentaire Type de champ (code opration)

ACTIONS

ADRESSES TYPE

CONDITIONS

En sortie du squenceur, il faut que les microcommandes soient aiguilles vers dif-

frentes fonctions effectuer. Ceci est ralis liade dun multiplexeur command par

le type de champ.

Le squencement est alors dcoup en plusieurs squences de microcommandes et

ceci pose un problme notamment lors de sauts conditionnels.

Lors des sauts conditionnels, il faut simultanment tester les variables externes, selon

ltat recharger ou non une nouvelle adresse dans le CAR et gnrer lordre de charge-

ment. Dans ce cas, il faudra raliser ceci en deux tapes et mmoriser un tat interm-

diaire

Lorganigramme de test se traduit en pratique par le schma ci-dessus. Do le

schma du squenceur microprogramm suivant :

Cette structure ncessite deux phases dhorloge dcales

1

et

2

. La condition de

validation de chargement sera prsente dans la bascule D aprs le calcul de la condition.

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 45

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

3.c) Exemple de squenceur

Reprenons lexemple du multiplieur cbl prcdant pour une microprogrammation

verticale.

(1) Organigramme

Il doit tre modi an de crer deux tapes lors de chaque test.

Deux diffrences apparaissent par rapport lorganigramme dun squenceur cbl :

les tests se partagent en deux tapes ;

les sauts inconditionnels gnrent des tapes parts entires.

Donc, si nous dcrivons le squenceur dun point de vue matriel, il nous faudra

raliser un saut conditionnel lorsque la variable secondaire est active.

Dans certains organigrammes, nous voyons que des sauts conditionnels dtapes

sont effectus lorsque les tests sont faux (ex : sup) ou lorsque des tests sont vrais (ex :

start ag).

Comme nous navons quune variable secondaire, il nous faut homogniser les tests

et sauts : soit tous les sauts conditionnels sont valides pour un rsultat VRAI du test, soit

tous les sauts seffectuent lors dun test VRAI ralis entre un bit du sqeunceur et un

tat qui forcera la sortie VRAI de la variable de chargement.

Ce qui donne au niveau du test matriel

(2) Organisation des microinstructions

Pour limiter le nombre de bits, nous travaillons en microprogrammation verticale.

Nous allons donc crer plusieurs types de champs complmentaires :

nous avons 28 tapes (daprs lorganigramme), ce qui ncessite un minimum de

5 bits pour son dcodage ;

lorsque nous analysons lorganigramme, nous nous apercevons que ltape 25 n-

cessite 7 actions simultanes : 4 pour lALU, un chargement de registre (LOADR)

et 2 validations de portes (VAL1, VAL2) ;

nous disposons de deux manires dagir : soit on augmente la taille des bits des

champs complmentaires, soit on dcoupe les tapes en plusieurs tapes et cre

des champs complmentaires diffrents (mais cela nest pas toujours possible, par

exemple lorsque la simultanit est ncessaire comme dans notre problme). Par

contre il existe un moyen en utilisant une mmorisation momentane des actions.

Nous allons associer une microinstruction contenant des actions de validation des

portes, un registre (mmoire) actif sur front

2

, la mme que celle qui active LOADR.

Ainsi lcriture suivante sera valable.

On peut maintenant dnir les diffrents types de microinstructions.

Les modications proposes accroissent le nombre des tapes. Il est ncessaire de

crer un champ complmentaire de 6 bits au minimum.

46 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

Microinstruction de type 1

Dans une microinstruction de type 1, nous allons inclure les 4 bits de fonctions

dALU (S3, S2, S1, S0), le chargement du registre rsultat (LOADR) et lordre de vali-

dation (VALR).

VALR LOADR S3 S2 S1 S0 0 0 1

type

Microinstruction de type 2

On y intgre les autres actions : SIGNF, VAL1, VAL2, VAL3, RAZSF, SETEF,

CLEAR. Nous avons 7 actions pour 6 bits, donc codage simultan de SIGNF, CLEAR,

VAL3.

SEF REF VAL1 VAL2 0 1 0

type

Microinstruction de type 3

On y inclut le reste des actions relatives aux commandes des registres. Nous y avons

six actions (S11, S12, S21, S22, S31, S32) pour 6 bits : il nest donc pas ncessaire de

les coder.

S11 S12 S21 S22 S31 S32 0 1 1

type

Microinstruction de type 4

Dans cette microinstruction de type 4, on dcrit les conditions de test. On dnombre

5 conditions : StartFlag, msbop1, msbop2, zero, lsbop2. Il nest pas besoin de les coder.

SF msbop1 msbop2 zero lsbop2 1 0 0

type

Microinstruction de type 5

Les adresses conditionnelles.

1 0 1

type

Microinstruction de type 6

On y place les adresses incondionnelles.

1 1 0

type

(3) Organigramme modi

Lorganigramme propos plus haut va tre lgrement modi compte-tenu de nou-

veaux regroupements des actions.

(4) Le microprogramme

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 47

IV.2. Ralisation pratique des circuits squentiels dnis par un GRAFCET ou un organigramme

Maintenant que nous avons dcrit la tche effectuer laide dun organigramme,

nous pouvons procder lcriture du microprogramme.

Il nous faut crire une succession de microinstructions composes dun ensemble

de bits disposs selon le codage qui a t dni prcdemment, ce qui est fastidieux et

source derreurs.

Il existe des langages dcriture de microprogrammes quivalents aux langages das-

semblage ou ventuellement aux langages de haut niveau de type interprteur.

Nous allons rester ici, au niveau du langage binaire ardu mais intressant pour la

comprhension du fonctionnement du squenceur.

N tape Champs complmentaires type de champ

0 100000 100

1 000011 101

2 000001 110

3 000010 010

4 010000 100

5 000111 101

6 001111 110

7 001011 010

8 010000 001

9 100000 001

10 100000 011

11 001000 010

12 011111 001

13 100000 001

.

.

.

.

.

.

.

.

.

48 Architecture des systmes microprocesseurs c M. Siadat & C. Diou

BIBLIOGRAPHIE

Bibliographie

[RAM] RAM Shopping Guide, http://www.ramshopping.com/guide.php

c M. Siadat & C. Diou Architecture des systmes microprocesseurs 49

Vous aimerez peut-être aussi

- Corrige 1Document29 pagesCorrige 1Bila100% (1)

- Programmation Des MicrocontroleursDocument108 pagesProgrammation Des MicrocontroleursHors ManPas encore d'évaluation

- Cours Systemes Micro-Programmes Parti1Document43 pagesCours Systemes Micro-Programmes Parti1alkassoum100% (3)

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Assembleur 8086Document45 pagesAssembleur 8086jamesamine100% (10)

- Cours Microcontrôleurs-Tres ImportantDocument132 pagesCours Microcontrôleurs-Tres ImportantNabil Dakhli0% (1)

- 04 Microprocesseur 8086Document21 pages04 Microprocesseur 8086Rafik OuchenePas encore d'évaluation

- AssembleurDocument26 pagesAssembleurHedi Yatouji100% (1)

- VhdlexDocument10 pagesVhdlexSoukaina NJPas encore d'évaluation

- Ch4 Stm32 Interface Usart CanDocument31 pagesCh4 Stm32 Interface Usart CanmanelPas encore d'évaluation

- Modelsim QuartusDocument23 pagesModelsim QuartusAli AlFiguiguiPas encore d'évaluation

- Chapitre 5 VHDLDocument91 pagesChapitre 5 VHDLdhdhPas encore d'évaluation

- MicroprocesseurDocument7 pagesMicroprocesseurwalidjoePas encore d'évaluation

- Architecture Des Systèmes À Microprocesseur TP N°2: Timer / Génération de Signal PWMDocument20 pagesArchitecture Des Systèmes À Microprocesseur TP N°2: Timer / Génération de Signal PWMAwatef MessaoudiPas encore d'évaluation

- Microprocesseur 8088 8086Document86 pagesMicroprocesseur 8088 8086Afenspy Pipose100% (3)

- VHDL Travaux2TP20180701ABDEL1Document8 pagesVHDL Travaux2TP20180701ABDEL1Tarek BouazzaPas encore d'évaluation

- TP 4 AssembleurDocument1 pageTP 4 AssembleurMohamed El Mourabit100% (1)

- MicroProcesseur Hicham ELKASMIDocument12 pagesMicroProcesseur Hicham ELKASMIEl Oufir El MehdiPas encore d'évaluation

- Algébre de BooleDocument25 pagesAlgébre de Boolesakre100% (5)

- TD4Document1 pageTD4Mounira Tarhouni100% (1)

- Fascicule de TP FpgaDocument32 pagesFascicule de TP FpgaHichem HamdiPas encore d'évaluation

- Assembleur x86Document96 pagesAssembleur x86Ibtihel MechleouiPas encore d'évaluation

- Initiation Au Langage Assembleur x86Document14 pagesInitiation Au Langage Assembleur x86electroblida100% (3)

- Travaux Dirigés FPGA & VHDLDocument28 pagesTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- Processeurs Embarques 1ppDocument66 pagesProcesseurs Embarques 1ppAhle Assenna0% (1)

- 1-TP Microprocesseur PDFDocument5 pages1-TP Microprocesseur PDFAmin DAHMANI100% (1)

- TP Sin 2018 2017 PDFDocument21 pagesTP Sin 2018 2017 PDFyapPas encore d'évaluation

- Les MemoiresDocument45 pagesLes MemoiresWalter FopaPas encore d'évaluation

- TD 2021Document4 pagesTD 2021elhaoudar.nassima100% (1)

- Fiche de Travaux Diriges PDFDocument6 pagesFiche de Travaux Diriges PDFGoran Person DongmoPas encore d'évaluation

- Formation Interface Communication 1Document19 pagesFormation Interface Communication 1اشر اقPas encore d'évaluation

- Corrigé TD 154Document3 pagesCorrigé TD 154MBADJOUN Daniel100% (1)