Académique Documents

Professionnel Documents

Culture Documents

Solutions Travaux Diriges N 1 2 3 Sam Au 2021 2022

Transféré par

Kam ZegTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Solutions Travaux Diriges N 1 2 3 Sam Au 2021 2022

Transféré par

Kam ZegDroits d'auteur :

Formats disponibles

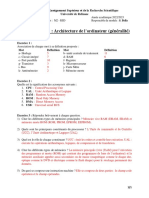

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 1

EXERCICE 2

CLK 𝑄𝑄0 𝑄𝑄1 𝑄𝑄2 𝑄𝑄3

0 0 0 0 0

1 1 0 0 0

2 0 1 0 0

3 1 0 1 0

4 1 1 0 1

5 0 1 1 0

6 0 0 1 1

7 0 0 0 1

8 1 0 0 0

9 0 1 0 0

10 1 0 1 0

SOL. TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/3

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 3

1)

2) Huit impulsions d’horloge

EXERCICE 4

SOL. TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/3

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 5

1)

ENTRÉES SORTIES

Clear Mode Parallèles

CLK Q3 Q2 Q1 Q0

�����

𝑀𝑀𝑀𝑀 S0 S1 P3 P2 P1 P0

1 1 1 1 1 0 1 1 1 0 1 1

2)

SOL. TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 3/3

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 1

1) Quelle est la capacité en bits d’une mémoire pouvant stocker 1073741824

Octets ?

Solution :

CM = 1 073 741 824×8 = 8 589 934 592 Bits.

2) Quelle est alors sa capacité en (a) Ko ; (b) Mo ; (c) Go ?

Solution :

a) CM = 1 073 741 824 × 8 = 230 ×8 Bits = 210 ×220 ×8 Bits = 220 ×8 kbits.

CM = 220 ko = 1 048 576 ko.

b) CM = 220 ko = 210 × 210 ko = 1024 ×210 ko = 210 Mo = 1024 Mo.

c) CM = 210 Mo = 1024 Mo = 1 Go.

EXERCICE 2

Quelles peuvent être les organisations d’une mémoire de 32kbits, sachant

qu’elle utilise des mots ayant une taille multiple d’une puissance de 2

(exemple : 8,16,…)

Solution :

32 kbits = 32768 bits.

Cette mémoire aura

- 4096 mots de 8 bits (4096=32768/8) ou

- 2048 mots de 16 bits ou

- 1024 mots de 32 bits ou encore

- 512 mots de 64 bits …

EXERCICE 3

Calculer la capacité mémoire d'un boitier dont le bus d'adresse est de 16

bits et un bus de données de 8 bits.

Solution : Puisque 8 bits = 1 octet, la capacité = 216 × 1 = 64 Ko

EXERCICE 4

1) Effectuez l’extension de la mémoire ROM de 64k × 4 de la figure ci-dessous

pour créer une mémoire ROM de 64k × 8.

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

Solution : Voir figure ci-dessous.

Notez qu’une adresse spécifique est accédée dans ROM 1 et ROM 2 au même

moment. Les quatre bits d’une adresse sélectionnée dans ROM 1 et les quatre

bits de l’adresse correspondante dans ROM 2 sortent en parallèle pour former

un mot de huit bits sur le bus de données. Notez également qu’un niveau BAS

sur la ligne de validation du circuit, 𝑉𝑉� , (qui forme un bus de commande

simple) valide les deux mémoires.

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

2) Décrivez la procédure d’extension d’une mémoire ROM de 64k × 1 pour former

une mémoire ROM de 64k × 8.

Solution :

Huit mémoires ROM de de 64k × 1 sont connectées en parallèle pour former une

mémoire ROM de 64k × 8.

EXERCICE 5

1) Utilisez les mémoires de l’exercice 4 pour former une mémoire ROM de

64k × 16.

Solution :

Vous devez créer une mémoire pouvant stocker 65 536 mots de 16 bits. Il faut

donc quatre mémoires ROM de 64k × 4, comme l’illustre la figure ci-dessous.

2) Combien faut-il de mémoires ROM de 64k × 1 pour créer une mémoire ROM de

64k × 16.

Solution :

Seize mémoires ROM de 64k × 1.

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 3/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 6

1) Utilisez des mémoires SRAM de 1M × 4 pour créer une mémoire SRAM de

1M × 8.

Solution :

Le schéma de principe simplifié de la figure suivante illustre les

interconnexions des deux mémoires SRAM de 1M × 4.

2) Utilisez des mémoires SRAM de 1M × 8 pour former une mémoire SRAM de

1M ×16.

Solution : Voir figure suivante (Page 5).

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 4/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 7

1) Utilisez des mémoires RAM1 de 512k × 4 pour créer une mémoire RAM2 de

1M × 4.

Solution : Voir figure suivante (Page 6).

L’extension d’adressage est obtenue en connectant l’entrée de validation du

circuit (𝑉𝑉�0), au vingtième bit d’adresse (𝐴𝐴19 ), comme l’illustre la figure

ci-dessous. L’entrée (𝑉𝑉�1 ) sert d’entrée de validation commune aux deux

mémoires. Lorsque le vingtième bit d’adresse est au niveau BAS, le mémoire

RAM 1 est sélectionnée (RAM 2 est bloquée) et les 19 bits d’adresse les

moins significatifs (𝐴𝐴0 − 𝐴𝐴18 ) accèdent à chacune des adresses de la mémoire

RAM 1. Lorsque le vingtième bit d’adresse est au niveau HAUT, la mémoire RAM

2 est validée par le niveau BAS à la sortie de l’inverseur (RAM 1 est

bloquée) et les 19 bits (𝐴𝐴0 − 𝐴𝐴18 ) accèdent à chacune des adresses de la

mémoire RAM 2.

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 5/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

2) Quelles sont les échelles d’adresses de chaque mémoire RAM1 formant la

mémoire résultante RAM2.

Solution :

- RAM 1 : de 0 à 524 287 (0 à 219 − 1) ;

- RAM 2 : de 524 288 à 1 048 575 (219 à 220 − 1)

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 6/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 8

À l’aide de plusieurs RAM (M1) de la figure ci-dessous de 512 octets

possédant un bus de donnée de 4 bits, on souhaite réaliser une RAM (M2) de 8

KO possédant un bus de donnée de 16 bits.

1) Donnez le nombre de mots et la largeur du bus d’adresse des deux types de

RAM.

Solution :

- M1 : 512 octets = (512 × 8/4) mots de 4 bits = 1 Kilo mots de 4 bits.

1 Kilo mots = 210 mots.

La mémoire M1 possède 10 fils d’adresse.

- M2 : 8 KO = (8K × 8/16) mots de 16 bits = 4 Kilos mots de 16 bits.

4 Kilos mots = 212 mots.

La mémoire M2 possède 12 fils d’adresse.

2) Combien de mémoires doit-on assembler en série ?

Solution :

- On passe d’une profondeur de 1 Kilo mots à une profondeur de 4 Kilos

mots.

- Il faut assembler 4 mémoires en série (4K / 1K = 4).

3) Combien de mémoires doit-on assembler en parallèle ?

Solution :

- On passe d’un bus de donnée de 4 bits à un bus de donnée de 16 bits.

- Il faut assembler 4 mémoires en parallèle (16 / 4 = 4).

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 7/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

���� (Chip Select) des

4) Combien de bits d’adresse vont servir à déterminer le 𝑪𝑪𝑪𝑪

mémoires M1 ?

Solution :

Ce sont les 2 bits d’adresse supplémentaires de la mémoire M2 (par

rapport à la mémoire M1) qui vont servir à déterminer le �𝐶𝐶𝐶𝐶

��� des RAM

(12 – 10 = 2).

5) Donnez le schéma de câblage.

Solution : Voir figure ci-dessous.

SOL. TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 8/8

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 1

Indiquer le mode d’adressage dans chacune des instructions suivantes :

N° Instruction Mode d’adressage

01 MVI A,0AH Immédiat

02 STA 204AH Direct

03 LXI H,2049H Immédiat

04 INX H Registre

05 MOV B,M Indirect à Registre

06 ADD B Registre

07 MOV C,A Registre

08 SUB C Registre

09 CMA Implicite

10 LXI D,204BH Immédiat

11 STAX D Indirect à Registre

12 HLT Implicite

EXERCICE 2

Après exécution du programme de l’exercice 1, écrit en assembleur 8085,

quel est le contenu des cases mémoires dont les adresses sont : 204AH et

204BH ?

Solution :

- Le contenu de la case mémoire dont l’adresse 204AH = 0AH.

- Le contenu de la case mémoire dont l’adresse 204BH = FFH.

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 3

1) Quelle est la taille en Octet (Byte) de chaque instruction du programme

de l’exercice 1.

2) Donner le code Hexa de chaque instruction

Solution :

N° Instruction Taille de l’instruction en Byte Code Hexa

01 MVI A,0AH 2 3E

0A

02 STA 204AH 3 32

4A

20

03 LXI H,2049H 3 21

49

20

04 INX H 1 23

05 MOV B,M 1 46

06 ADD B 1 80

07 MOV C,A 1 4F

08 SUB C 1 91

09 CMA 1 2F

10 LXI D,204BH 3 11

4B

20

11 STAX D 1 12

12 HLT 1 76

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 4

Vérifier chaque instruction du programme ci-dessous si elle correcte ou

non et corriger-la si nécessaire.

Solution :

N° Instruction Instruction Correction Commentaires

CORRECTE ?

01 MOV A,01H NON MVI A,01H Adressage immédiat

02 MVI H, L NON MOV H, L Adressage registre

03 MOV C, D OUI

04 INX L NON INR L INX pour incrémenter des paires

registres 16 bits par exemple : INX H

05 INX H OUI

06 ADD B OUI

07 ADI 200H NON ADI fonctionne sur 8 bits or 200H

(51210) est codé sur 9 bits

08 SUB B, E NON La soustraction se fait

obligatoirement avec l’ACC par

exemple : SUB E

09 DCX D OUI

10 XRI 02H OUI

11 XRI E NON XRA E Adressage registre or XRI pour un

adressage Immédiat

12 SBI 05H OUI

13 LDAX C NON Il faut utiliser des paires de

LDAX B registres sur 16 bits par exemple :

B(BC), D(DE), H(HL)

14 HLT OUI

15 JNC NON Il faut préciser l’adresse de

JNC Adr branchement

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 3/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 5

Écrire un programme en assembleur 8085 qui permet de calculer l’expression

W = X + Y – Z. Le résultat doit être rangé à l’adresse FF03H tout en sachant

que X, Y et Z se trouvent à l’adresse FF00H, FF01H et FF02H respectivement.

Solution :

#ORG FF00H

#DB 0AH, 0BH, 06H

#ORG FF04H

#BEGIN FF04H

LXI H,FF00H

MOV A,M

INX H

ADD M

INX H

SUB M

STA FF03H

HLT

EXERCICE 6

Écrire un programme en assembleur 8085, qui permet de multiplier le contenu

de l’accumulateur par la valeur 5.

Solution :

# ORG 0000H

# BEGIN 0000H

MVI A,0AH

MOV B,A

ADD A ; ACC = A+A

ADD A ; ACC = (A+A) + (A+A)

ADD B ; ACC = (A+A) + (A+A)+ A => ACC X 5

HLT

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 4/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 7

Écrire un programme en assembleur 8085, qui permet de multiplier le contenu

de l’accumulateur par la valeur 4.

Solution :

# ORG 0000H

# BEGIN 0000H

MVI A,08H

ANA A ; clear carry

RAL

ANA A

RAL

HLT

EXERCICE 8

Écrire un programme en assembleur 8085, qui permet de diviser le contenu

de l’accumulateur par la valeur 8.

Solution :

# ORG 0000H

# BEGIN 0000H

MVI A,20

ANA A

RAR

ANA A

RAR

ANA A

RAR

HLT

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 5/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 9

Écrire un programme en assembleur 8085, qui permet de stocker à l’adresse

FF03H le plus grand de deux nombres X et Y se trouvant à l’adresse FF00H

et FF01 respectivement, et de stocker la valeur BBH à l’adresse FF02H. Si

X est égal à Y, le programme doit permettre stocker X ou Y à l’adresse

FF03H et la valeur EEH à l’adresse FF02H.

Solution :

# ORG FF00H

# DB 01H, 11H,10H

# ORG FF04H

# BEGIN FF04H

LXI H,FF00

MOV A,M

INX H

MOV C,M

CMP C

JZ EQUAL

JC GREATER

STA FF03

MVI A,BB

STA FF02

HLT

EQUAL:STA FF03

MVI A,EE

STA FF02

HLT

GREATER:MOV A,C

STA FF03

MVI A,BB

STA FF02

HLT

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 6/7

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : L3 (3ème année Licence LMD)

Unité d’enseignement : UEF 1.1.1

Matière 1: Systèmes à Microprocesseurs

EXERCICE 10

Écrire un programme en assembleur 8085, qui permet de transférer 10 octets,

situés dans la zone mémoire délimitée par l’adresse de début, FFA0H, à la

zone mémoire délimitée par l’adresse de début FFB0H.

Solution :

# ORG FFA0

# DB A0H, A1H, A2H, A3H, A4H, A5H, A6H, A7H, A8H, A9H

# ORG 0000H

# BEGIN 0000H

MVI B,0A

LXI H,FFA0

LXI D,FFB0

LOOP: MOV A,M

STAX D

INX H

INX D

DCR B

JNZ LOOP

HLT

SOL. TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 7/7

Vous aimerez peut-être aussi

- Bâtiment Zéro Énergie: L'énergie totale consommée par les services publics est égale à l'énergie renouvelable totale produiteD'EverandBâtiment Zéro Énergie: L'énergie totale consommée par les services publics est égale à l'énergie renouvelable totale produitePas encore d'évaluation

- Travaux Diriges N 1 2 3 Sam Au 2021 2022Document9 pagesTravaux Diriges N 1 2 3 Sam Au 2021 2022Kam ZegPas encore d'évaluation

- Simulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysD'EverandSimulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysPas encore d'évaluation

- TD Série 1Document2 pagesTD Série 1ayman coukiPas encore d'évaluation

- Technologie Chimique Électrothermique: La solution miracle pour pénétrer la prochaine génération de chars avancésD'EverandTechnologie Chimique Électrothermique: La solution miracle pour pénétrer la prochaine génération de chars avancésPas encore d'évaluation

- TD2 PDFDocument6 pagesTD2 PDFKheir eddine DaouadiPas encore d'évaluation

- Batterie Au Lithium-Air: Ouvrir la voie aux avions de ligne électriquesD'EverandBatterie Au Lithium-Air: Ouvrir la voie aux avions de ligne électriquesPas encore d'évaluation

- Examen SN - 2020 2021 - Smi5 Lp2iDocument2 pagesExamen SN - 2020 2021 - Smi5 Lp2iØssama AjbliPas encore d'évaluation

- Théorie et conception des filtres analogiques, 2e édition: Avec MatlabD'EverandThéorie et conception des filtres analogiques, 2e édition: Avec MatlabPas encore d'évaluation

- Serie 3Document2 pagesSerie 3merouane mehdiPas encore d'évaluation

- Récupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriqueD'EverandRécupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriquePas encore d'évaluation

- Exam - Réseaux Ratt - Fev22Document2 pagesExam - Réseaux Ratt - Fev22Øssama AjbliPas encore d'évaluation

- 3 Serie DevoirDocument2 pages3 Serie Devoirelmehdi.elkhoutiPas encore d'évaluation

- examen-WLAN 2023 2024Document3 pagesexamen-WLAN 2023 2024Faïza TabbanaPas encore d'évaluation

- BTP RESEAUDocument2 pagesBTP RESEAUNoùr Haffoudhi Ep KramtiPas encore d'évaluation

- TP Cna 2022Document11 pagesTP Cna 2022imadPas encore d'évaluation

- TD 01Document2 pagesTD 01Saadallah SebbaghPas encore d'évaluation

- Série de TD 3: Module NS522 ELN3Document2 pagesSérie de TD 3: Module NS522 ELN3Adel-Hani MiloudiPas encore d'évaluation

- CPCG TD1Document2 pagesCPCG TD1Bella SalimaPas encore d'évaluation

- Réalisation D'un Rucher ConnectéDocument85 pagesRéalisation D'un Rucher ConnectéAbderrahmane SmaaliPas encore d'évaluation

- TD1 Reseaux1Document4 pagesTD1 Reseaux1Ahmed La MiriPas encore d'évaluation

- TD Liaison Des DonnéesDocument2 pagesTD Liaison Des DonnéesSarra SamaaliPas encore d'évaluation

- Solution Série3Document6 pagesSolution Série3Aymen Khelaif100% (1)

- Cours Microcontroleur ITT2 Supptic DR TCHAGNA 2021Document47 pagesCours Microcontroleur ITT2 Supptic DR TCHAGNA 2021simo kamto guy lionelPas encore d'évaluation

- m1 Instrumentation - TD Fpga-VhdlDocument6 pagesm1 Instrumentation - TD Fpga-VhdlazedPas encore d'évaluation

- TDN°01Document2 pagesTDN°01Samo SamoPas encore d'évaluation

- Controle3s1 Bts Dsi ReseauDocument3 pagesControle3s1 Bts Dsi ReseauAbdelhak FadiliPas encore d'évaluation

- CPCG TD1 SolutionDocument2 pagesCPCG TD1 SolutionBella SalimaPas encore d'évaluation

- 7machine Tri Postal PDFDocument49 pages7machine Tri Postal PDFELmokhtar HamrouniPas encore d'évaluation

- DiodesDocument51 pagesDiodesJohn HeshimaPas encore d'évaluation

- Info 4e Trim1Document2 pagesInfo 4e Trim1ArmandPas encore d'évaluation

- Microprocesseurs Et MicrocontrôleursDocument169 pagesMicroprocesseurs Et MicrocontrôleursDhekra JebaliPas encore d'évaluation

- Ds Réseaux Locaux Et IndustruellesDocument3 pagesDs Réseaux Locaux Et IndustruellesnyanguitatianaoliviaPas encore d'évaluation

- Predoc_Teleinfo_Hiver_2003Document13 pagesPredoc_Teleinfo_Hiver_2003ibara guelorPas encore d'évaluation

- Microprocesseur UPLDocument83 pagesMicroprocesseur UPLkitungwa gaelPas encore d'évaluation

- Examen Internet 2022Document2 pagesExamen Internet 2022TabbanaPas encore d'évaluation

- Bts Snir 2022 PDFDocument56 pagesBts Snir 2022 PDFKarim HanzazPas encore d'évaluation

- Circuits ProgrammablesDocument95 pagesCircuits ProgrammablesRyheb B'MRzPas encore d'évaluation

- Fiche-TD 1 2 3 4 5Document6 pagesFiche-TD 1 2 3 4 5BafadePas encore d'évaluation

- Intra E02Document10 pagesIntra E02Sana BerchechPas encore d'évaluation

- Sol 03Document2 pagesSol 03Kahel el hadj chikhPas encore d'évaluation

- Réseau de TerrainDocument4 pagesRéseau de TerrainBader KassamePas encore d'évaluation

- Sys 7 Machine Tri Postal CORRECTIONDocument6 pagesSys 7 Machine Tri Postal CORRECTIONMC YoùNés AkOùrimPas encore d'évaluation

- Devoir 2 Teleinfo Epta Rit 2023Document3 pagesDevoir 2 Teleinfo Epta Rit 2023Bezout BEPas encore d'évaluation

- Chapitre - 2 RIL EthernetDocument10 pagesChapitre - 2 RIL Ethernetعبد الله عبد اللهPas encore d'évaluation

- Final NFA004 2022Document2 pagesFinal NFA004 2022assaadshreim365Pas encore d'évaluation

- AO L2 Série1Document4 pagesAO L2 Série1Smail Smart100% (1)

- Cours PICDocument71 pagesCours PICCherry CandyPas encore d'évaluation

- Chapitr 001Document5 pagesChapitr 001oussama bouguerraPas encore d'évaluation

- Compte - Rendu TP N°1: ObjectifDocument6 pagesCompte - Rendu TP N°1: Objectifya toPas encore d'évaluation

- Solintra E02Document9 pagesSolintra E02fahmiPas encore d'évaluation

- SDVariante2 231109 073529Document1 pageSDVariante2 231109 073529Djihene Babahenini100% (1)

- TP/Projet D'introduction Aux Systèmes Embarqués: Réalisation D'une Station MétéoDocument13 pagesTP/Projet D'introduction Aux Systèmes Embarqués: Réalisation D'une Station Météodhaoaudi fatmaPas encore d'évaluation

- Annale API Epreuves Info Tle A PDFDocument64 pagesAnnale API Epreuves Info Tle A PDFJoseph OndouaPas encore d'évaluation

- Reseau 2019 CorrigéDocument4 pagesReseau 2019 CorrigéDkfk HdjdPas encore d'évaluation

- Réseau Métropolitain Réseau Local Réseau ÉtenduDocument2 pagesRéseau Métropolitain Réseau Local Réseau ÉtenduBryan AydenPas encore d'évaluation

- Master Spécialisé en Big Data Et Cloud Computing 2Document2 pagesMaster Spécialisé en Big Data Et Cloud Computing 2Fatima Zahra100% (1)

- Annale Info Tle-A ESG-22Document69 pagesAnnale Info Tle-A ESG-22oceannemballa173Pas encore d'évaluation

- Fiche TD N°1Document1 pageFiche TD N°1Tiki RistoPas encore d'évaluation

- Fiche de TD1 AO USTO 2023-2024 BEKDocument4 pagesFiche de TD1 AO USTO 2023-2024 BEKsup.contactPas encore d'évaluation

- Cours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Document80 pagesCours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 7 Micro Processeur (Mode de Compatibilité)Document19 pagesCours 7 Micro Processeur (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Manuel Laboratoire Controleurs EmbarquesDocument92 pagesManuel Laboratoire Controleurs EmbarquesKam ZegPas encore d'évaluation

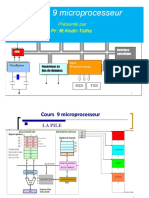

- Cours 9 UP KEDIR (Mode de Compatibilité)Document21 pagesCours 9 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 10 UP KEDIR (Mode de Compatibilité)Document29 pagesCours 10 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 8 UP KEDIR (Mode de Compatibilité)Document14 pagesCours 8 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 1 Communications SériesDocument1 pageCours 1 Communications SériesKam ZegPas encore d'évaluation

- Chapitre 1Document3 pagesChapitre 1Kam ZegPas encore d'évaluation

- CHPITRE 1couche 1 - SuiteDocument28 pagesCHPITRE 1couche 1 - SuiteKam ZegPas encore d'évaluation

- Chapitre 4Document17 pagesChapitre 4Kam ZegPas encore d'évaluation

- CHPITRE 1couche 1 - OSIDocument16 pagesCHPITRE 1couche 1 - OSIKam ZegPas encore d'évaluation

- Chapitre 3Document35 pagesChapitre 3Kam ZegPas encore d'évaluation

- Local Media1101029635307551998Document14 pagesLocal Media1101029635307551998Djam's100% (1)

- Chapitre 2Document8 pagesChapitre 2Kam ZegPas encore d'évaluation

- Cours Systemes A MicroprocesseursDocument134 pagesCours Systemes A MicroprocesseursKam ZegPas encore d'évaluation

- CHPITRE 1couche 1 MultiplexageDocument41 pagesCHPITRE 1couche 1 MultiplexageKam ZegPas encore d'évaluation

- DSP CH2 CovidDocument52 pagesDSP CH2 CovidKam ZegPas encore d'évaluation

- Fascicule ASBAIDocument90 pagesFascicule ASBAIKam ZegPas encore d'évaluation

- TP Systemes A MicroprocesseuersDocument40 pagesTP Systemes A MicroprocesseuersKam ZegPas encore d'évaluation

- Chapitre 0 IteletDocument22 pagesChapitre 0 IteletKam ZegPas encore d'évaluation

- 3 Cours Microprocesseur 16 BitsDocument15 pages3 Cours Microprocesseur 16 BitsSeghiour AbdellatifPas encore d'évaluation

- Architecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Document204 pagesArchitecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Kam ZegPas encore d'évaluation

- ArchitectureDocument108 pagesArchitectureMorus SidusPas encore d'évaluation

- Microprocesseur 8088 8086Document86 pagesMicroprocesseur 8088 8086Afenspy Pipose100% (3)

- Index: Paquet en Ligne Double L'architecture de Harvard AtmelDocument4 pagesIndex: Paquet en Ligne Double L'architecture de Harvard AtmelKam ZegPas encore d'évaluation

- Interfaces ES InterruptionDocument4 pagesInterfaces ES InterruptionKam ZegPas encore d'évaluation

- Saidat Farsi 2Document46 pagesSaidat Farsi 2Kam ZegPas encore d'évaluation

- Chi Bane MouloudDocument73 pagesChi Bane MouloudKam ZegPas encore d'évaluation

- Chapitre 1-Notion de Pointeur PDFDocument8 pagesChapitre 1-Notion de Pointeur PDFMakrem NessibPas encore d'évaluation

- Fileserver Qu'est-Ce Qu'un Serveur de Fichiers - IONOSDocument12 pagesFileserver Qu'est-Ce Qu'un Serveur de Fichiers - IONOSLA-ZOUBE GAELPas encore d'évaluation

- Re16 TD4Document8 pagesRe16 TD4Widad BouzidaPas encore d'évaluation

- 1 Introduction Au Cours - Définitions Et Rôles Du PHP Et Du MySQL - Pierre Giraud - 1Document4 pages1 Introduction Au Cours - Définitions Et Rôles Du PHP Et Du MySQL - Pierre Giraud - 1La SadPas encore d'évaluation

- Expose XMLDocument36 pagesExpose XMLissamPas encore d'évaluation

- Correction TD5 Communication Et SynchronisationDocument3 pagesCorrection TD5 Communication Et SynchronisationMouad1993100% (2)

- TP LVMDocument4 pagesTP LVMAnonymous k2SY4zdI3Pas encore d'évaluation

- Mod 1Document43 pagesMod 1Salem SaidiPas encore d'évaluation

- Comment Compresser Des Fichiers PDFDocument2 pagesComment Compresser Des Fichiers PDFSahriPas encore d'évaluation

- Cours HadoopDocument56 pagesCours HadoopSalahPas encore d'évaluation

- Cours PigDocument93 pagesCours PigOussama PanoramaPas encore d'évaluation

- E - Compteurs SynchronesDocument4 pagesE - Compteurs SynchronesMectronique 201B100% (1)

- Coursatelier FTPDocument14 pagesCoursatelier FTPWilfreed Minfoundi ManguelePas encore d'évaluation

- Grigori Petrovitch Grabovoi L Homme Des Codes de Guerison Miracle 2923568109Document2 pagesGrigori Petrovitch Grabovoi L Homme Des Codes de Guerison Miracle 2923568109kalyPas encore d'évaluation

- Free NasDocument3 pagesFree Nastchuipet100% (1)

- Expose JaxbDocument18 pagesExpose Jaxbarbogaste adzabaPas encore d'évaluation

- Chap 3 Logique SéquentielleDocument13 pagesChap 3 Logique SéquentielleNidal LaatabPas encore d'évaluation

- IPSec Tunnel Mode VS GRE Over IPSEC (GREoIPSEC)Document4 pagesIPSec Tunnel Mode VS GRE Over IPSEC (GREoIPSEC)Agouassou Kouadio100% (1)

- Sen Rappels TCP IpDocument48 pagesSen Rappels TCP IpcalculovPas encore d'évaluation

- Chapitre 1 - Introduction Au Base de Données NoSQLDocument19 pagesChapitre 1 - Introduction Au Base de Données NoSQLKhadija HoPas encore d'évaluation

- 2-Réseaux Informatiques - CORRIGE: Exercices TIBDocument4 pages2-Réseaux Informatiques - CORRIGE: Exercices TIBOumaima BouhaniPas encore d'évaluation

- 2 Arbres Equilibres PDFDocument68 pages2 Arbres Equilibres PDFMohamed BaammiPas encore d'évaluation

- Sujet - TP - 4 Kibana - Tierno Oumar DIALLO Bach3 Cyber EcetechDocument19 pagesSujet - TP - 4 Kibana - Tierno Oumar DIALLO Bach3 Cyber EcetechAnonyme10Pas encore d'évaluation

- Innovateur de ProximitéDocument6 pagesInnovateur de ProximitéramuPas encore d'évaluation

- Semaine 3Document13 pagesSemaine 3DJIGUIBA MAGASSAPas encore d'évaluation

- Memoire Online - Etude Et Application de Microcontroleur 16f84 - Mustapha BODocument10 pagesMemoire Online - Etude Et Application de Microcontroleur 16f84 - Mustapha BOAbderrahmane SmaaliPas encore d'évaluation

- Transmissions Numériques Sur Onde PorteuseDocument17 pagesTransmissions Numériques Sur Onde PorteuseOthman NchifaPas encore d'évaluation

- Devoir 100 ds1 Informatique 2eme Eco Gestion 2009 12 09Document4 pagesDevoir 100 ds1 Informatique 2eme Eco Gestion 2009 12 09isimgPas encore d'évaluation

- Codage de Lempel Ziv WelchDocument4 pagesCodage de Lempel Ziv WelchMalak arabPas encore d'évaluation

- postgreSQL PostgisDocument31 pagespostgreSQL PostgisLotfi LadhariPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Gestion de projet : outils pour la vie quotidienneD'EverandGestion de projet : outils pour la vie quotidienneÉvaluation : 5 sur 5 étoiles5/5 (2)

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Manuel de fabrication du savon: Je fabrique mes savons facilementD'EverandManuel de fabrication du savon: Je fabrique mes savons facilementÉvaluation : 5 sur 5 étoiles5/5 (4)

- Création d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileD'EverandCréation d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Marketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxD'EverandMarketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxPas encore d'évaluation

- 101 idées pour travailler à domicile: Plus tous les conseils pour bien démarrerD'Everand101 idées pour travailler à domicile: Plus tous les conseils pour bien démarrerÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- La psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsD'EverandLa psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsPas encore d'évaluation

- Blockchain: Applications et compréhension du monde réel: Comment appliquer la Blockchain dans votre mondeD'EverandBlockchain: Applications et compréhension du monde réel: Comment appliquer la Blockchain dans votre mondePas encore d'évaluation

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Forex Trading facile à apprendre: Le guide d'introduction au marché des changes et aux stratégies de négociation les plus efficaces dans l'industrie des devises.D'EverandForex Trading facile à apprendre: Le guide d'introduction au marché des changes et aux stratégies de négociation les plus efficaces dans l'industrie des devises.Évaluation : 4 sur 5 étoiles4/5 (1)