Académique Documents

Professionnel Documents

Culture Documents

Travaux Diriges N 1 2 3 Sam Au 2021 2022

Transféré par

Kam ZegTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Travaux Diriges N 1 2 3 Sam Au 2021 2022

Transféré par

Kam ZegDroits d'auteur :

Formats disponibles

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 1

La figure suivante montre trois registres à décalage type SISO. Donner le

contenu du registre de sortie C, après quatre impulsions d’horloge.

EXERCICE 2

Le circuit de la figure ci-dessous montre un registre type SIPO avec une porte

logique XNOR utilisant certains bits du registre à décalage pour générer le

prochain bit d’entrée (DIN). Le circuit est initialement à l’état

𝑄𝑄3 𝑄𝑄2 𝑄𝑄1 𝑄𝑄0 = 0000. Complétez le tableau suivant pour montrer les sorties du

registre après le nombre des impulsions du signal horloge, CLK, indiqué sur le

tableau.

CLK 𝑄𝑄0 𝑄𝑄1 𝑄𝑄2 𝑄𝑄3

0 0 0 0 0

1

2

3

4

5

6

7

8

9

10

TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/4

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 3

1) Développez le diagramme logique du registre à décalage de La figure ci-

dessous en remplaçant les bascules D par des bascules JK.

2) Combien faut-il d’impulsions de signal d’horloge pour entrer un octet en

série dans un registre à décalage de huit bits.

EXERCICE 4

Déterminer l’état du registre à décalage de la figure (a) ci-dessous après

chaque impulsion de signal d’horloge en réponse à la forme d’onde de l’entrée

������������ de la figure (a). Présumez que 𝑄𝑄3 𝑄𝑄2 𝑄𝑄1 𝑄𝑄0 = 1011 et que

de commande 𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷𝐷/𝐺𝐺𝐺𝐺𝐺𝐺𝐺𝐺𝐺𝐺𝐺𝐺

la ligne d’entrée des données série est au niveau BAS.

(a)

(b)

TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/4

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 5 Étude du registre à décalage universel 74LS194

On désire utiliser le registre à décalage universel 74LS194 pour un chargement

parallèle des données et une lecture série de ces données avec décalage vers

la droite :

1) Remplir le tableau de fonctionnement ci-dessous pour permettre un chargement

parallèle du mot binaire 1011 dans le registre 74LS194 ?

ENTRÉES SORTIES

Clear Mode CLK Parallèle

Q3 Q2 Q1 Q0

�����)

(𝑀𝑀𝑀𝑀 S0 S1 (CP) P3 P2 P1 P0

2) En supposant que le chargement du mot binaire a été effectué, donnez le

câblage du 74LS194 pour réaliser un décalage rotatif de la gauche vers la

droite ?

TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 3/4

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

TD N°1/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 4/4

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 1

1) Quelle est la capacité en bits d’une mémoire pouvant stocker 1073741824

Octets ?

2) Quelle est alors sa capacité en (a) Ko ; (b) Mo ; (c) Go ?

EXERCICE 2

Quelles peuvent être les organisations d’une mémoire de 32kbits, sachant

qu’elle utilise des mots ayant une taille multiple d’une puissance de 2

(exemple : 8,16,…)

EXERCICE 3

Calculer la capacité mémoire d'un boitier dont le bus d'adresse est de 16 bits

et un bus de données de 8 bits.

EXERCICE 4

1) Effectuez l’extension de la mémoire ROM de 64k × 4 de la figure ci-dessous

pour créer une mémoire ROM de 64k × 8.

2) Décrivez la procédure d’extension d’une mémoire ROM de 64k × 1 pour former

une mémoire ROM de 64k × 8.

EXERCICE 5

1) Utilisez les mémoires de l’exercice 4 pour former une mémoire ROM de

64k × 16.

2) Combien faut-il de mémoires ROM de 64k × 1 pour créer une mémoire ROM de

64k × 16.

TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/2

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 6

1) Utilisez des mémoires SRAM de 1M × 4 pour créer une mémoire SRAM de

1M × 8.

2) Utilisez des mémoires SRAM de 1M × 8 pour former une mémoire SRAM de

1M ×16.

EXERCICE 7

1) Utilisez des mémoires RAM1 de 512k × 4 pour créer une mémoire RAM2 de

1M × 4.

2) Quelles sont les échelles d’adresses de chaque mémoire RAM1 formant la

mémoire résultante RAM2.

EXERCICE 8

À l’aide de plusieurs RAM (M1) de la figure ci-dessous de 512 octets possédant

un bus de donnée de 4 bits, on souhaite réaliser une RAM (M2) de 8 KO possédant

un bus de donnée de 16 bits.

1) Donnez le nombre de mots et la largeur du bus d’adresse des deux types de

RAM.

2) Combien de mémoires doit-on assembler en série ?

3) Combien de mémoires doit-on assembler en parallèle ?

���� (Chip Select) des

4) Combien de bits d’adresse vont servir à déterminer le 𝑪𝑪𝑪𝑪

mémoires M1 ?

5) Donnez le schéma de câblage.

TD N°2/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/2

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 1

Indiquer le mode d’adressage dans chacune des instructions suivantes :

N° Instruction

01 MVI A,0AH

02 STA 204AH

03 LXI H,2049H

04 INX H

05 MOV B,M

06 ADD B

07 MOV C,A

08 SUB C

09 CMA

10 LXI D,204BH

11 STAX D

12 HLT

EXERCICE 2

Après exécution du programme de l’exercice 1, écrit en assembleur 8085,

quel est le contenu des cases mémoires dont les adresses sont : 204AH et

204BH ?

EXERCICE 3

1) Quelle est la taille en Octet (Byte) de chaque instruction du programme

de l’exercice 1 ?

2) Donner le code Hexa de chaque instruction

TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 1/3

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 4

Vérifier chaque instruction du programme ci-dessous si elle correcte ou

non et corriger-la si nécessaire.

N° Instruction

01 MOV A,01H

02 MVI H, L

03 MOV C, D

04 INX L

05 INX H

06 ADD B

07 ADI 200H

08 SUB B, E

09 DCX D

10 XRI 02H

11 XRI E

12 SBI 05H

13 LDAX C

14 HLT

15 JNC

EXERCICE 5

Écrire un programme en assembleur 8085 qui permet de calculer l’expression

W = X + Y – Z. Le résultat doit être rangé à l’adresse FF03H tout en sachant

que X, Y et Z se trouvent à l’adresse FF00H, FF01H et FF02H respectivement.

EXERCICE 6

Écrire un programme en assembleur 8085, qui permet de multiplier le contenu

de l’accumulateur par la valeur 5.

TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 2/3

Université Mohamed El Bachir El Ibrahimi - Bordj Bou Arréridj 2021/2022

Faculté des Sciences et de la Technologie

Département d’électronique

Domaine : Sciences et Technologies

Filière : Électronique

Niveau : 3ème année Licence LMD

Unité d’enseignement : UEF 3.1.1

Matière 1 : Systèmes à microprocesseurs

EXERCICE 7

Écrire un programme en assembleur 8085, qui permet de multiplier le contenu

de l’accumulateur par la valeur 4.

EXERCICE 8

Écrire un programme en assembleur 8085, qui permet de diviser le contenu

de l’accumulateur par la valeur 8.

EXERCICE 9

Écrire un programme en assembleur 8085, qui permet de stocker à l’adresse

FF03H le plus grand de deux nombres X et Y se trouvant à l’adresse FF00H

et FF01 respectivement, et de stocker la valeur BBH à l’adresse FF02H. Si

X est égal à Y, le programme doit permettre stocker X ou Y à l’adresse

FF03H et la valeur EEH à l’adresse FF02H.

EXERCICE 10

Écrire un programme en assembleur 8085, qui permet de transférer 10 octets,

situés dans la zone mémoire délimitée par l’adresse de début, FFA0H, à la

zone mémoire délimitée par l’adresse de début FFB0H.

TD N°3/UEF 3.1.1/Matière 1: Systèmes à Microprocesseurs |Page 3/3

Vous aimerez peut-être aussi

- Bien débuter en programmation: Formation professionnelleD'EverandBien débuter en programmation: Formation professionnellePas encore d'évaluation

- DOBBI-Equipements ForageDocument114 pagesDOBBI-Equipements ForageMohamed Anis Boumaza100% (6)

- Detection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013D'EverandDetection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013Pas encore d'évaluation

- Les macros avec OpenOffice CALC: La programmation BASIC pour tousD'EverandLes macros avec OpenOffice CALC: La programmation BASIC pour tousPas encore d'évaluation

- Cours Systemes A MicroprocesseursDocument134 pagesCours Systemes A MicroprocesseursKam ZegPas encore d'évaluation

- Architecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Document204 pagesArchitecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Kam ZegPas encore d'évaluation

- Micro-Controleurs 16F84A - FinalDocument10 pagesMicro-Controleurs 16F84A - FinalElmokh Lassaad100% (1)

- Lycee Bilingue de Latsuet-Tsinmelieu: Epreuve TheoriqueDocument4 pagesLycee Bilingue de Latsuet-Tsinmelieu: Epreuve TheoriqueWilly DmtPas encore d'évaluation

- TD Mup 8085 Fezari 2018Document35 pagesTD Mup 8085 Fezari 2018koyabePas encore d'évaluation

- TP N°1 - Prise en Main de L'environnement APIDocument6 pagesTP N°1 - Prise en Main de L'environnement APIFarouk MalkiPas encore d'évaluation

- Conception D Une Chaise Electrique MonteDocument81 pagesConception D Une Chaise Electrique MonteFettal AbdelilahPas encore d'évaluation

- Ais Edf Normasource NS500Document16 pagesAis Edf Normasource NS500haroldPas encore d'évaluation

- Solutions Travaux Diriges N 1 2 3 Sam Au 2021 2022Document18 pagesSolutions Travaux Diriges N 1 2 3 Sam Au 2021 2022Kam ZegPas encore d'évaluation

- 7machine Tri Postal PDFDocument49 pages7machine Tri Postal PDFELmokhtar HamrouniPas encore d'évaluation

- Proposition V2Document4 pagesProposition V2Siham DLPas encore d'évaluation

- TD1 ArchitecturedesOrdinateursDocument4 pagesTD1 ArchitecturedesOrdinateursstephaniemakeu7Pas encore d'évaluation

- ExamenArchitectureSMI4 2018-RattrapageDocument2 pagesExamenArchitectureSMI4 2018-Rattrapagehamzaaouni79Pas encore d'évaluation

- TD 01: Microcontrôleur Exercice 1: Notions de BaseDocument1 pageTD 01: Microcontrôleur Exercice 1: Notions de BasemeddPas encore d'évaluation

- Système de NumérationDocument2 pagesSystème de Numérationzakia zerroukiPas encore d'évaluation

- Exam - Réseaux Ratt - Fev22Document2 pagesExam - Réseaux Ratt - Fev22Øssama AjbliPas encore d'évaluation

- Examen SN - 2020 2021 - Smi5 Lp2iDocument2 pagesExamen SN - 2020 2021 - Smi5 Lp2iØssama AjbliPas encore d'évaluation

- Reseau 2019 CorrigéDocument4 pagesReseau 2019 CorrigéDkfk HdjdPas encore d'évaluation

- Final NFA004 2022Document2 pagesFinal NFA004 2022assaadshreim365Pas encore d'évaluation

- Predoc_Teleinfo_Hiver_2003Document13 pagesPredoc_Teleinfo_Hiver_2003ibara guelorPas encore d'évaluation

- 555Document13 pages555hafsa midiniPas encore d'évaluation

- TD 01Document2 pagesTD 01Saadallah SebbaghPas encore d'évaluation

- Examen - M2 - Bus de Terrain Et RLI - Février 2019Document3 pagesExamen - M2 - Bus de Terrain Et RLI - Février 2019aymenPas encore d'évaluation

- Examen 07-02-2009 Rattrapage CompressedDocument2 pagesExamen 07-02-2009 Rattrapage CompressedMoha MansouriPas encore d'évaluation

- Sy Ee Sem Iv Dem 22421 QP Model AnswersDocument37 pagesSy Ee Sem Iv Dem 22421 QP Model Answerskpatil9887Pas encore d'évaluation

- Fiche de TD1 AO USTO 2023-2024 BEKDocument4 pagesFiche de TD1 AO USTO 2023-2024 BEKsup.contactPas encore d'évaluation

- RE FichesTDDocument10 pagesRE FichesTDEl Kadiri Mohamed0% (1)

- Cours PICDocument71 pagesCours PICCherry CandyPas encore d'évaluation

- DSarchitectureTi2 2010Document2 pagesDSarchitectureTi2 2010الضحك حتى تصبح مضحكPas encore d'évaluation

- Mat 131 TDDocument3 pagesMat 131 TDPharellePas encore d'évaluation

- m1 Instrumentation - TD Fpga-VhdlDocument6 pagesm1 Instrumentation - TD Fpga-VhdlazedPas encore d'évaluation

- TD Architecture Des Ordinateurs 2021-2022Document5 pagesTD Architecture Des Ordinateurs 2021-2022Ouattara larsonPas encore d'évaluation

- Mi 2an Usthb Isil Acad Emd Archi2013Document3 pagesMi 2an Usthb Isil Acad Emd Archi2013Colmain NassiriPas encore d'évaluation

- Bts Snir 2022 PDFDocument56 pagesBts Snir 2022 PDFKarim HanzazPas encore d'évaluation

- Serie 2Document5 pagesSerie 2Malick100% (1)

- TP Cna 2022Document11 pagesTP Cna 2022imadPas encore d'évaluation

- Fiche-TD 1 2 3 4 5Document6 pagesFiche-TD 1 2 3 4 5BafadePas encore d'évaluation

- TD1 VHDL GM2 22-23Document2 pagesTD1 VHDL GM2 22-23mariam.ouaaabedPas encore d'évaluation

- RE FichesTD PDFDocument19 pagesRE FichesTD PDFgargield63Pas encore d'évaluation

- Examen 2012-2013 + CorrigéDocument3 pagesExamen 2012-2013 + Corrigéyacine lebgPas encore d'évaluation

- Exemple Examen Arch OrdDocument2 pagesExemple Examen Arch Ordhamzaaouni79Pas encore d'évaluation

- TD 2 - La couche PhysiqueDocument2 pagesTD 2 - La couche Physiqueadil.benyousseffPas encore d'évaluation

- TP SestrDocument25 pagesTP SestrTamokouePas encore d'évaluation

- TD Série 1Document2 pagesTD Série 1ayman coukiPas encore d'évaluation

- Serie 3Document2 pagesSerie 3merouane mehdiPas encore d'évaluation

- TD2 PDFDocument6 pagesTD2 PDFKheir eddine DaouadiPas encore d'évaluation

- 2015 08 21 TD32 Le Microprocesseur 0708S1Document4 pages2015 08 21 TD32 Le Microprocesseur 0708S1Mēđ GouigaPas encore d'évaluation

- Examen Internet 2022Document2 pagesExamen Internet 2022TabbanaPas encore d'évaluation

- TD1 Reseaux1Document4 pagesTD1 Reseaux1Ahmed La MiriPas encore d'évaluation

- TD1 - P APIDocument2 pagesTD1 - P APIMohammed ALMUSHIAAPas encore d'évaluation

- Support Microprocesseurs PDFDocument64 pagesSupport Microprocesseurs PDFRidhaNommanePas encore d'évaluation

- Microprocesseurs Et MicrocontrôleursDocument169 pagesMicroprocesseurs Et MicrocontrôleursDhekra JebaliPas encore d'évaluation

- Solutionnaire Archi TD1Document5 pagesSolutionnaire Archi TD1Colmain Nassiri100% (1)

- TD 1-BisDocument2 pagesTD 1-BisHejer nasriPas encore d'évaluation

- TD2 Reseaux1 2021 2022 FinDocument2 pagesTD2 Reseaux1 2021 2022 FinAhmed La MiriPas encore d'évaluation

- TD-initiation Aux RéseauxDocument3 pagesTD-initiation Aux RéseauxJeremy Le Prophète100% (1)

- Bts Snec 2023 Nc 1 SujetDocument59 pagesBts Snec 2023 Nc 1 Sujetjodie.goupiePas encore d'évaluation

- Solintra E02Document9 pagesSolintra E02fahmiPas encore d'évaluation

- Examen 18-01-2010 CompressedDocument2 pagesExamen 18-01-2010 Compressedخالد خالدPas encore d'évaluation

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

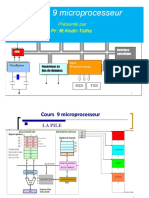

- Cours 9 UP KEDIR (Mode de Compatibilité)Document21 pagesCours 9 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 8 UP KEDIR (Mode de Compatibilité)Document14 pagesCours 8 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Local Media1101029635307551998Document14 pagesLocal Media1101029635307551998Djam's100% (1)

- Cours 1 Communications SériesDocument1 pageCours 1 Communications SériesKam ZegPas encore d'évaluation

- Manuel Laboratoire Controleurs EmbarquesDocument92 pagesManuel Laboratoire Controleurs EmbarquesKam ZegPas encore d'évaluation

- Cours 10 UP KEDIR (Mode de Compatibilité)Document29 pagesCours 10 UP KEDIR (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Document80 pagesCours Micro Processeur Chp1-2-3 (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Cours 7 Micro Processeur (Mode de Compatibilité)Document19 pagesCours 7 Micro Processeur (Mode de Compatibilité)Kam ZegPas encore d'évaluation

- Chapitre 1Document3 pagesChapitre 1Kam ZegPas encore d'évaluation

- Chapitre 4Document17 pagesChapitre 4Kam ZegPas encore d'évaluation

- Chapitre 2Document8 pagesChapitre 2Kam ZegPas encore d'évaluation

- DSP CH2 CovidDocument52 pagesDSP CH2 CovidKam ZegPas encore d'évaluation

- CHPITRE 1couche 1 MultiplexageDocument41 pagesCHPITRE 1couche 1 MultiplexageKam ZegPas encore d'évaluation

- CHPITRE 1couche 1 - SuiteDocument28 pagesCHPITRE 1couche 1 - SuiteKam ZegPas encore d'évaluation

- Chapitre 3Document35 pagesChapitre 3Kam ZegPas encore d'évaluation

- CHPITRE 1couche 1 - OSIDocument16 pagesCHPITRE 1couche 1 - OSIKam ZegPas encore d'évaluation

- TP Systemes A MicroprocesseuersDocument40 pagesTP Systemes A MicroprocesseuersKam ZegPas encore d'évaluation

- Microprocesseur 8088 8086Document86 pagesMicroprocesseur 8088 8086Afenspy Pipose100% (3)

- Chapitre 0 IteletDocument22 pagesChapitre 0 IteletKam ZegPas encore d'évaluation

- Fascicule ASBAIDocument90 pagesFascicule ASBAIKam ZegPas encore d'évaluation

- Interfaces ES InterruptionDocument4 pagesInterfaces ES InterruptionKam ZegPas encore d'évaluation

- ArchitectureDocument108 pagesArchitectureMorus SidusPas encore d'évaluation

- Chi Bane MouloudDocument73 pagesChi Bane MouloudKam ZegPas encore d'évaluation

- Index: Paquet en Ligne Double L'architecture de Harvard AtmelDocument4 pagesIndex: Paquet en Ligne Double L'architecture de Harvard AtmelKam ZegPas encore d'évaluation

- 3 Cours Microprocesseur 16 BitsDocument15 pages3 Cours Microprocesseur 16 BitsSeghiour AbdellatifPas encore d'évaluation

- Saidat Farsi 2Document46 pagesSaidat Farsi 2Kam ZegPas encore d'évaluation

- Manuel Ecran Ge Nano Comap PDFDocument91 pagesManuel Ecran Ge Nano Comap PDFJessica Barrocal100% (1)

- 32pfl4908 f8 QSG Esp PDFDocument10 pages32pfl4908 f8 QSG Esp PDFHegel AmadorPas encore d'évaluation

- Step Mouhamadia TBTF03Document103 pagesStep Mouhamadia TBTF03hicham boutouchePas encore d'évaluation

- Commande MCCDocument20 pagesCommande MCCAmIne Omda100% (1)

- Programmation en C Des Microcontrôleurs RISC AVR Télécharger, Lire PDFDocument6 pagesProgrammation en C Des Microcontrôleurs RISC AVR Télécharger, Lire PDFFaiza RebbouhPas encore d'évaluation

- 4.4. Instruction de Manoeuvre Du DSCDocument30 pages4.4. Instruction de Manoeuvre Du DSCMartin FoxxxPas encore d'évaluation

- Metier AnalogiqueDocument408 pagesMetier AnalogiqueNatasha HayesPas encore d'évaluation

- Defaut 191-31-32 - AlphaDocument71 pagesDefaut 191-31-32 - Alphafaf31aPas encore d'évaluation

- 25 Le Freinage GénéralitéDocument12 pages25 Le Freinage GénéralitéClément GuérinPas encore d'évaluation

- Schéma Electrique Gestion MoteurDocument3 pagesSchéma Electrique Gestion Moteurcastrer les-consPas encore d'évaluation

- Logan TransmiLOGAN Transmisie-FR MR-388.PDsie FR MR 388Document43 pagesLogan TransmiLOGAN Transmisie-FR MR-388.PDsie FR MR 388Fleancu Cristian100% (1)

- Fiche Technique U17 3@Document1 pageFiche Technique U17 3@Mito ManPas encore d'évaluation

- NFC 13-100 (2015)Document69 pagesNFC 13-100 (2015)Karim KammounPas encore d'évaluation

- SSP 126 Etude Technique Boite de Vitesses DSG7 0AMDocument64 pagesSSP 126 Etude Technique Boite de Vitesses DSG7 0AMLakhdar BouchenakPas encore d'évaluation

- Notice Technique ELEXIUMDocument19 pagesNotice Technique ELEXIUMMaestro AbdellahPas encore d'évaluation

- CI11!8!10-Cablage Ligne Telephonique - EleveDocument16 pagesCI11!8!10-Cablage Ligne Telephonique - EleveHamdiMidouPas encore d'évaluation

- Td3 Machine AsynchroneDocument5 pagesTd3 Machine Asynchronehassankch100% (2)

- IT Chapitre 3Document31 pagesIT Chapitre 3venanceharoldPas encore d'évaluation

- 2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDDocument25 pages2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDAFAD100% (1)

- Catalogue - WeMos - 090154Document160 pagesCatalogue - WeMos - 090154ngollyjoachimPas encore d'évaluation

- Powerpact Chapitre ADocument49 pagesPowerpact Chapitre Aأحمد العابدPas encore d'évaluation

- Manuel de Bord 607Document169 pagesManuel de Bord 607BertrandPas encore d'évaluation

- Manuel Onduleur Solaire Effekta Ks3000stDocument72 pagesManuel Onduleur Solaire Effekta Ks3000stphilgoninPas encore d'évaluation

- ElectrotechniqueSTSCNED TP2 PDFDocument18 pagesElectrotechniqueSTSCNED TP2 PDFKarim ZaraiPas encore d'évaluation

- Cours Architectures Avancées Sur PucesDocument84 pagesCours Architectures Avancées Sur PucesArafet BelhajPas encore d'évaluation

- LU Sixty FRDocument40 pagesLU Sixty FREduardo SantanaPas encore d'évaluation

- Liste Codes OBDDocument101 pagesListe Codes OBDAlex GauthierPas encore d'évaluation