Académique Documents

Professionnel Documents

Culture Documents

Chapitre I Le Microprocesseur 6809

Transféré par

Sabri AbidiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Chapitre I Le Microprocesseur 6809

Transféré par

Sabri AbidiDroits d'auteur :

Formats disponibles

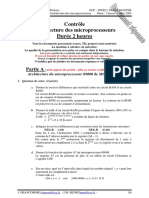

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

Le Microprocesseur 6809

I- Généralités :

Le microprocesseur 6809 est un processeur 8 bits de haute gamme, dont

l’organisation interne est orientée 16 bits. Il peut adresser 64 K-octets par

l’intermédiaire de son bus d’adresses.

Il est compatible au niveau source avec les programmes écrits pour le 6800 et

peut utiliser tous les circuits périphériques de ce dernier. Toutefois, le 6809 ne se

présente pas seulement comme une version améliorée du 6800, mais comme un

nouveau produit, dont l’architecture interne, les modes d’adressage et le jeu

d’instruction en fait un processeur orienté logiciel.

Cette première partie est consacrée à l’étude du composant seul, elle a pour but

d’amener le stagiaire à bien connaître le produit avant d’aborder ses possibilités

logicielles.

Les deux versions du 6809 (horloge interne ou externe) sont présentées dans ce

chapitre. La description de chacune des broches permet une analyse détaillée des

caractéristiques matérielles.

L’architecture interne du microprocesseur 68009 est orienté 16 bits. En effet, il

possède : deux accumulateurs A et B de 8 bits pouvant être concaténés pour former un

seul accumulateur D 16 bits, deux registres d’index (16 bits), deux registres pointeurs

de pile (16 bits) utilisables en index, un pointeur de page (8 bits) permettant de

diviser l’espace mémoire du CPU en 256 pages de 256 octets chacune, et un registre

d’état de 8 bits. Le rôle détaillé de chacun de ces registre sera présenté

ultérieurement.

II- Organisation matérielle du 6809

1- Introduction

Le microprocesseur 6809 fabriqué en Technologie MOS canal N se présente

sous la forme d’un boîtier DIL, 40 broches et mono-tension (+5V).

C’est un composant dont le jeu d’instructions est figé. Son fonctionnement est

entamé par une horloge interne (6809) ou externe (6809E).

Il possède trois bus indépendants :

un bus de données de 8 bits ;

un bus d’adresses de 16 bits ;

un bus de contrôle de 10 bits pour le 6809 et 12 bits pour le 6809E.

Le microprocesseur 6809E est adapté aux applications multiprocesseurs, ainsi

qu’aux applications nécessitant la synchronisation du microprocesseur avec une

horloge générée à l’extérieur.

La compatibilité matérielle entre les deux versions du 6809 et les modules

mémoires et périphériques du 6809 E est totale.

Ben Soussia Afif Page 1

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

La seconde partie de ce chapitre est consacrée à la description des signaux

communs aux deux versions.

Les deux paragraphes suivants détaillent d’une part les signaux spécifiques au

6809 et d’autre part ceux du 6809 E.

2- Description des signaux communs au 6809 et 6809 E

2-1- Alimentation

Le boîtier est alimenté par une tension unique. Vss est la masse du boîtier ou

0V, Vcc est à + 5V 5%.

2-2- Bus de données : D0-D7

La communication entre le microprocesseur et le bus de données bidirectionnel

du système se fait par l’intermédiaire de huit broches. Chaque broche peut piloter une

charge TTL plus 8 circuit de la famille 6800. Les « drivers » de bus sont en logique

trois états. Le chargement du sens de fonctionnement des broches se fait sans conflit

grâce à la période E. Q (horloges) maintient le bus en état haute impédance.

2-3- Bus d’adresses : A0-A15

Le transfert des adresses du microprocesseur vers le bus d’adresses de système

se par l’intermédiaire de 16 broches unidirectionnelles. Chaque broche peut piloter

une charge TTL plus 8 circuit de la famille 6800. Les « drivers » de bus sont en

logique trois états. Lorsque le bus n’est pas occupé par le processeur pour gérer un

transfert de données, il est positionné à l’adresse FFFF (hexadécimale) avec la ligne

R/W = 1 (lecture) et BS = 0 (fonctionnement normal).

2-4- Bus de contrôle :

2-4-1- Lecture – Ecriture :R/W (Read/Write)

Cette broche de sortie détermine la direction du transfert sur le bus des

données. R/W = 1, le microprocesseur est en lecture, D0-D7 sont des entrées ; R/W=0,

le processeur est en écriture, D0-D7 sont des sorties. Cette broche est en logique trois

états.

2-4-2- Lignes d’état du bus : BA (Bus Available) / BS (Bus State)

Le signal de disponibilité du bus BA indique la présence d’un signal de contrôle

interne qui met les bus du microprocesseur dans l’état haute impédance.

A0-A15

BA =1 D0-D7 état haute impédance

R/W

Ce signal est très utile pour les applications possédant un périphérique capable

de gérer les bus adresses et données à la place du microprocesseur (un DMA par

exemple). Il n’implique pas que le bus soit disponible pendant plus d’un cycle. Quand

BA passe à l’état bas, il s’écoule un cycle supplémentaire avant que le

microprocesseur ne reprenne le contrôle des bus.

Ben Soussia Afif Page 2

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

Les quatre combinaisons possibles des lignes BA-BS permettent de connaître à

chaque instant, l’état du microprocesseur. Ces indications sont données sur le front

montant de Q.

BA BS Fonctionnement du CPU

0 0 Normal

0 1 Reconnaissance d’interruption

1 0 Reconnaissance de synchro externe

1 1 Arrêt ou bus accordé

BA.BS = 0.0 : le microprocesseur est en fonctionnement normal, il gère les

bus adresses et données.

BA.BS = 0.1 : le microprocesseur est en phase de reconnaissance d’interruption

pendant deux cycles. Cet état correspond à la recherche matérielle du vecteur

interruption (RESET, NMI, IRQ, FIRQ, SWI, SWI2 ou SWI3).

BA.BS = 1.0 : ce signal est positionné lorsque le CPU rencontre l’instruction de

synchronisation externe (SYNC). Il attend cette synchronisation d’une des lignes

d’interruption, les bus sont en haute impédance.

BA.BS = 1.1 : cet état correspond à l’arrêt du processeur ou à l’autogestion venant

du 6809 de faire gérer les bus adresses et données par un circuit externe (EX.

DMA). Les bus sont en haute impédance.

2-4-3- Arrêt du microprocesseur : HALT

Cette entrée permet d’interrompre le déroulement d’un programme de façon

« hardware ». Le processeur termine l’instruction en cours, puis positionne BA et BS à

1. Il n’y a pas perte d’information, le processeur reprend la suite du programme dès

que la broche HALT est de nouveau haute. Tant que le processeur est l’arrêt :

les demandes d’interruptions IRQ et FIRQ sont masquées,

les demandes d’accès direct mémoire sont autorisées,

les demandes d’interruptions prioritaires RESET et NMI sont prises en comte mais

le traitement est différé,

les horloges fonctionnent normalement.

2-4-4- Initialisation : RESET

Un niveau bas sur cette entrée entraîne une réinitialisation complète du

microprocesseur :

L’instruction en cours est arrêtée.

Le registre de page est mis à zéro.

Les interruptions IRQ et FIRQ sont masquées.

L’interruption non masquable est désarmée.

Les vecteurs d’initialisation sont accessibles aux adresses FFFE-FFFF.

L’adresse constituée par ces deux octets mémoire est chargée dans le compteur

programme PC puis le processeur exécute le programme à partir de cette adresse.

2-4-5- Broches d’interruption : NMI, FIRQ, IRQ

2-4-5-1- Broche NMI (No Masquable Interrupt)

Ben Soussia Afif Page 3

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

Cette entrée est active sur un front descendant. Elle ne peut être masquée par

logiciel. Après une séquence d’initialisation, cette broche est validée par un

chargement du pointeur de pile S. Le processeur exécute un programme de traitement

d’interruption approprié, NMI doit avoir retrouvé son état initial avant la fin de celui-

ci.

2-4-5-2- Broches FIRQ et IRQ (Fast Interrupt Request, Interrupt Request)

Ces deux entrées sont actives sur des niveaux bas. Elles sont masquées ou

validées par logiciel. Le processeur exécute un programme de traitement, en fonction

de l’interruption détectée. La ligne FIRQ est prioritaire sur IRQ. Dans les deux cas,

ces lignes doivent être remises à l’état initial pendant l’exécution du sous-programme

d’interruption.

3- Les signaux spécifiques au 6809

3-1- Les signaux horloges

3-1-1- Entrées horloges : XTAL et EXTAL

Deux modes de fonctionnement sont possible :

- L’oscillateur interne est connecté par ces deux broches à un quartz externe

(résonance parallèle).

- Une horloge TTL est connectée à EXTAL, XTAL étant reliée à la masse. Le

quartz ou la fréquence externe quatre fois la fréquence bus.

3-1-2- Sorties horloges : E out et Q out

- E out : signal horloge du système (synchronisation avec la périphérie), la

fréquence est celle de base du microprocesseur.

- Q out : signal d’horloge, en quadrature avec E. Les adresses du CPU sont

correcte à partir d’un front montant de Q. Les données sont mémorisées sur

un front descendant de E.

E out

Q out

¼ cycle

Début de Validation des Fin de cycle

cycle adresses Mémorisation des données

3-2- Les signaux de contrôle

3-2-1- Allongement de l’horloge E : MRDY (Memory Ready)

Cette entrée de commande permet l’allongement de E pour utiliser des

mémoires lentes (temps d’accès aux données augmenté). L’allongement de E est un

multiple de ¼ de cycle bus, sa valeur maximum est de 10µs. Dans les cycles VMA,

MRDY n’a pas d’effet sur E.

3-2-2- DMA et rafraîchissement mémoire : DMA/BREQ

Ben Soussia Afif Page 4

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

L’entrée DMA/BREQ permet de suspendre l’utilisation des bus par le

microprocesseur, pour faire de l’accès direct ou un rafraîchissement mémoire. Tant

que Q est au niveau haut, le passage à l’état bas de DMA/BREQ entraîne l’arrêt à la

fin de l’instruction en cours. BA et BS passent à l’état 1 ; les bus données, adresses et

la ligne R/W sont à l’état haute impédance, l’horloge interne est bloquée, E et Q

continuent à osciller.

Tous les 16 cycles, trois cycles seront nécessaires pour l’auto-rafraîchissement

du microprocesseur.

4- Les signaux spécifiques au 6809E

4-1- Les signaux horloges : E in et Q in

Ces deux signaux d’entrée sont identiques à E out et Q out du microprocesseur

à horloge interne. Les fonctions ainsi que le diagramme des temps sont les mêmes.

L’horloge externe travaille cette fois à la fréquence de base du microprocesseur.

4-2- Les signaux de contrôle

4-2-1- Contrôle trois états : TSC (Three State Control)

Cette entrée joue le même rôle que l’entrée DMA/BREQ du 6809. Quand TSC

est à l’état 1, les bus adresses, données et la ligne R/W sont en haute impédance. Il est

à ce moment possible de faire de l’accès direct ou du rafraîchissement mémoire ou

encore la gestion des bus avec un autre microprocesseur.

4-2-2- Dernier cycle d’une instruction : LIC (Last Instruction Cycle)

Cette sortie est à l’état haut pendant le dernier cycle de chacune des

instructions exécutées par le microprocesseur. Le cycle CPU qui suit ce signal est

donc toujours un cycle de recherche de opératoire. LIC est à l’état haut quand le

processeur est en attente d’une synchronisation externe (SYNC), en phase d’empilage

au cours d’une gestion d’interruption, ou dans l’état HALT.

4-2-3- Contrôle des ressources communes en multiprocesseur : AVMA (Advanced

Valid Memory Adress)

C’est une sorte de validation d’adresse mémoire perfectionnée qui passe à

l’état un au cours du cycle précédant un accès bus par le microprocesseur. Le signal

permet un contrôle efficace des ressources communes d’un dispositif multiprocesseur.

Si le microprocesseur est en HALT ou SYNC, AVMA est au niveau bas.

4-2-4- Occupation des bus : BUSY

Comme le signal précédent, BUSY facilite les applications multiprocesseurs. Ce

signal passe à l’état haut pendant les instructions de type lecture, modification,

écriture (ASL par exemple). De cette façon, les zones mémoires ne sont adressées

simultanément par deux processeurs.

III- Architecture interne du 6809

Le microprocesseur 6809 comporte neuf registre interne programmable,

accessible par l’utilisateur :

deux accumulateurs 8 bits (transformables en accumulateur 16 bits D) ;

Ben Soussia Afif Page 5

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

deux registres d’index X et Y (16 bits) ;

deux registres pointeurs de pile U et S (16 bits) ;

un compteur programme PC (16 bits) ;

un registre de page DP (8 bits) ;

un registre codes condition CCR (8 bits).

1- Accumulateurs : A, B, D

Les calculs arithmétiques et les manipulations de données se font grâce aux

accumulateurs A et B. ces deux registres sont interchangeables sauf pour les

instructions ABX, DAA et les opérations sur 16 bits.

Le double accumulateur 16 bits ou registre D est le résultat de la concaténation

des accumulateurs A et B. le registre A constitue l’octet de poids fort, le registre B

celui de poids faible.

2- Registres pointeurs : S, U, X, Y

2-1- Registres d’index : X, Y

Ces deux pointeurs d’utilisation parfaitement identique sont utilisés dans les

modes d’adressage indexé.

Le contenu de ces registres (16 bits) permet de pointer des données, il est

modifiable par addition d’une constante optionnelle ou d’un déplacement codé sur 8

ou 16 bits.

Les possibilités de pré-décrémentation et post-incrémentation permettent une

gestion efficace des données rangées sous forme de table.

Les registres U et s peuvent être également utilisés comme index.

2-2- Registres pointeurs de pile : U, S

Le 6809 possède deux pointeurs de pile (16 bits). Le pointeur de pile S

(système) est utilisé par le microprocesseur pour gérer la sauvegarde de ses registres

internes pendant l’exécution de programmes d’interruptions ou de sous programmes.

Le pointeur de pile U (utilisateur) est utilisé uniquement par le programmeur pour

réaliser des passages d’arguments de ou vers des sous-programmes.

La décrémentation du pointeur (S ou U), précède toujours le début de la phase

d’empilement. A la fin du stockage, le pointeur reste au niveau du dernier registre

entré.

La gestion des piles utilisateurs ou systèmes est identiques. Dans le cas d’un

dépilement, le dernier registre entré est le premier sorti. Le dernier registre dépilé est

suivi d’une incrémentation du pointeur.

Les pointeurs de pile U et S ont les mêmes possibilités d’adressage indexé que

les registres X et Y.

3- Registre compteur programme : PC

Le contenu de ce registre (16 bits) détermine l’adresse de l’instruction que doit

exécuter le processeur. Il pointe en permanence l’adresse de la prochaine instruction

à exécuter.

Dans certains cas, ce compteur programme peut être utilisé comme un index.

Ben Soussia Afif Page 6

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

4- Registre de page : DP

Ce registre (8 bits) est prévu pour étendre les possibilité d’adressage direct à

tout l’espace mémoire, sous contrôle du logiciel. Le contenu de ce registre apparaît

sur les lignes d’adresses poids fort (A8-A15), au cours de l’exécution d’une instruction

en mode d’adressage direct. Le contenu de DP et l’octet suivant le code opératoire

d’une instruction en adressage direct, contrôlent le bus adresses du microprocesseur.

A la mise sous tension le registre de page est mis à zéro (pour rester compatible avec

le 6800).

5- Registre de codes condition : CCR

Le registre codes condition (8bits) définit à tout instant l’état des indicateurs du

processeur. Les bits de ce registres sont :

7 6 5 4 3 2 1 0

CCR E F H I N Z V C

Etat de sauvegarde Retenue

Masque d’interruption FIRQ Débordement

Demi-Retenue Zéro

Masque d’interruption IRQ Négatif

Ces indicateurs peuvent se scinder en deux parties indépendantes : d’une part,

les bits 0, 1, 2, 3 et 5 positionnés en fonction du résultat des instructions qui

manipulent les données, et d’autre part, les bits 4, 6 et 7 dont le rôle est lié au

fonctionnement en interruptions.

5-1- Rôle des indicateurs arithmétiques

5-1-1- Rôle du bit C (b0) : Carry / retenue

Ce bit indicateur de retenue est positionné lors d’une opération arithmétique.

Les manipulations de données et opérations logiques n’affectent pas C. Suivant les

opérations effectuées : C peut jouer différents rôles.

Exemple 1 :

ADCA #$2C addition avec retenue du contenu de l’accumulateur A et de la valeur

hexadécimale 2C

A = $ E2

1110 0010

+ 0010 1100 C=1

1 0000 1110

C indique ici un débordement non signé.

Exemple 2 :

SUBA #$22 Soustraction de la valeur $22 au contenu de l’accumulateur A

Ben Soussia Afif Page 7

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

A = $C3

1100 0011

complément à deux de $22 + 1101 1110 C=0

1 1010 0001

Dans le cas d’une soustraction (CMP, NEG, SUB, SBC) l’indicateur Carry est

le complément de la retenue de l’opération effectuée.

Exemple 3 :

MUL Multiplication du contenu de l’accumulateur A par celui de l’accumulateur B.

Le résultat est dans D

A = $C1 1100 0001

B = $45 0100 0101

1100 0001

11 0000 01

0011 0000 01

0011 0100 0000 0101

résultat A = $34

B = $05 C=0

Le bit C représente ici le bit 7 du résultat. Il est utile lorsque l’utilisateur ne

veut prendre en compte que les poids forts (accumulateur A), on peut de cete façon

arrondir le résultat.

5-1-2- Rôle du bit V (b1) : Overflow / Débordement en complément à deux

Ce bit est l’indicateur de débordement. Il est mis à un si le résultat (en

complément à deux) d’une opération arithmétique déborde. Les instructions de

chargements, stockages et opérations logiques positionnent V à zéro. Les opérations

arithmétiques positionnent V dans l‘état approprié.

Exemple 1 :

LDA #$12 chargement de l’accumulateur A avec la valeur 12

$12 A V =0

ici V est forcé à zéro.

Exemple 2 :

ADDA #$A0 Addition du contenu du registre A et de la valeur $A0

A = $9E

1001 1110 les retenues entre b6-b7 et au-delà de b7 sont différentes

+ 1010 0000 il y a débordement V =1

1 0011 1110

5-1-3- Rôle du bit Z (b2) : Zéro / résultat nul

Le bit n°2 est l’indicateur de 0, il est mis un si le résulta de l’opération

précédente est nul. Les instructions de chargements, de stockages, les opérations

logiques et arithmétiques positionnent Z dans l’état approprié.

Exemple 1 :

Ben Soussia Afif Page 8

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

A NDA #$C4 « et logique » entre le contenu de l’accumulateur A et la valeur

hexadécimale C4. Le résultat est dans A

A = $3B

0011 1011

et 1100 0100

0000 0000 Z= 1

Exemple 2 :

A NDA #$C3 « et logique » entre le contenu de l’accumulateur A et la valeur

hexadécimale C3. Le résultat est dans A

A = $3B

0011 1011

et 1100 0011

0000 0011 Z= 0

5-1-4- Rôle du bit N (b3) : Négatif / résultat négatif

Le bit 3 indique un résultat négatif. Il contient le bit de poids fort de l’octet

résultat de l’opération précédente. Un résultat négatif pour une opération en

complément à deux positionne N à un. Les instructions de chargement, stockages, les

opérations arithmétiques et logiques positionnent toutes N à l’état approprié.

Exemple :

LDA #$C1 chargement de l’accumulateur A avec la valeur hexadécimale C1

1100 0001 A

b7 = 1 N = 1

5-1-5- Rôle du bit H (b5) : Half-Carry / démi-retenue

Le bit 5 est le bit de demi-retenue. Il est utilisé dans l’UAL comme indicateur de

retenue du bit 3, pour les additions 8 bits seulement. Dans l’opération d’ajustement

décimal, l’instruction DAA utilise le bit indicateur de demi-retenue . Pour les

instructions de soustractions ou équivalentes, l’état de ce bit est indéfini.

Les instructions du microprocesseur 6809 s’exécutent en fonction de ces

indicateurs, et les positionnent. Certaines instructions de branchement utilisent deux

indicateurs (N et V) pour s’assurer de la validité des résultats. En effet, en complément

à deux, le bit N pourra être incorrect, si l’opération a engendré un débordement

(V=1).

5-2- Rôle des indicateurs d’interruptions

5-2-1- Rôle du bit I (b4) : Interrupt mask/ masque d’interruption

Ce bit, lorsqu’il est à un, masque les interruptions IRQ, seules les interruptions

plus prioritaires seront alors prises en compte.

5-2-2- Rôle du bit F (b6) : Fast Interrupt mask/ masque d’interruption rapide

Ce bit, lorsqu’il est à un, masque les interruptions FIRQ, seules les

interruptions plus prioritaires seront prises en compte.

5-2-3- Rôle du bit E (b7) : sauvegarde des registres dans la pile

Ben Soussia Afif Page 9

Chapitre I : Le Microprocesseur 6809 CSFE De Sousse

Le bit 7 est l’indicateur de sauvegarde des registres dans la pile. Si E est à 1,

tout le contexte du processeur est sauvegardé dans la pile. Si E est à zéro, une partie

des registres internes est sauvegardée.

Ben Soussia Afif Page 10

Vous aimerez peut-être aussi

- MicroprocesseurDocument25 pagesMicroprocesseurTH3JAZOULIPas encore d'évaluation

- 6809 EnsaDocument15 pages6809 EnsaAchraf Rossoneri75% (12)

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaPas encore d'évaluation

- Cours 6809 CIDocument117 pagesCours 6809 CIHamid Rezagui85% (13)

- Partie 2Document66 pagesPartie 2Fadoua MoutaoikilPas encore d'évaluation

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- Interruption du 6809-2Document12 pagesInterruption du 6809-2bouchenebPas encore d'évaluation

- Chapitre III Microprocesseur 6809 GSEA1Document36 pagesChapitre III Microprocesseur 6809 GSEA1kaoutarPas encore d'évaluation

- Chapitre I Microprocesseur 6809 GSEA12013 PDFDocument56 pagesChapitre I Microprocesseur 6809 GSEA12013 PDFRyan Hj100% (1)

- TP 1 Info Indus07Document15 pagesTP 1 Info Indus07MOHAMED TAMZAITIPas encore d'évaluation

- Cours 6809 CIDocument121 pagesCours 6809 CISoubkiPas encore d'évaluation

- Info IndusDocument14 pagesInfo IndusAhmed MsfPas encore d'évaluation

- Microprocesseur 6809: Présentation GénéraleDocument11 pagesMicroprocesseur 6809: Présentation GénéraleMOHAMED TAMZAITIPas encore d'évaluation

- Chapitre I Microprocesseur 6809 GSEA12013Document56 pagesChapitre I Microprocesseur 6809 GSEA12013xanafahd78% (9)

- Chapitre 2 Microcontroleur Pic 16f877Document8 pagesChapitre 2 Microcontroleur Pic 16f877Redouane AmianPas encore d'évaluation

- Partie3 Microcontroleur s4 E2iDocument9 pagesPartie3 Microcontroleur s4 E2iMoha BenmohaPas encore d'évaluation

- MicroDocument4 pagesMicroKOUASSI INNOCENT YAOPas encore d'évaluation

- Chap 3-MicrocontroleurDocument35 pagesChap 3-MicrocontroleurYosra rhim YosraPas encore d'évaluation

- TP Info IndusDocument26 pagesTP Info IndusAmine MassawiPas encore d'évaluation

- Programmation Des MicrocontroleursDocument108 pagesProgrammation Des MicrocontroleursHors ManPas encore d'évaluation

- MICROPROCESSEUR CORRIGE SUJET 2 - Copie - CopieDocument8 pagesMICROPROCESSEUR CORRIGE SUJET 2 - Copie - Copieawomariane hungerfortPas encore d'évaluation

- Initiation Aux Microcontrôleurs: Application Au 68HC11: Chapitre 3Document11 pagesInitiation Aux Microcontrôleurs: Application Au 68HC11: Chapitre 3Salma sahmadPas encore d'évaluation

- Chapitre 1Document17 pagesChapitre 1louizini abderahmanePas encore d'évaluation

- DSPIC30FDocument51 pagesDSPIC30Fouss18Pas encore d'évaluation

- 5cpu 8086Document9 pages5cpu 8086Ben Aissa OussamaPas encore d'évaluation

- Chapitre 4 - Architecture Des Systèmes ProgrammésDocument25 pagesChapitre 4 - Architecture Des Systèmes ProgrammésTtech hackPas encore d'évaluation

- Chapitre 3 - 090738Document11 pagesChapitre 3 - 090738Rãmï RøÿãlPas encore d'évaluation

- Chapitre 2 PPTDocument18 pagesChapitre 2 PPTabdel dalilPas encore d'évaluation

- Chapitre2 SE ARCHITECTURE DES MICROCONTROLLEURSDocument24 pagesChapitre2 SE ARCHITECTURE DES MICROCONTROLLEURSKarima ChakerPas encore d'évaluation

- chapitre 5 microcontroleursDocument28 pageschapitre 5 microcontroleursbenachour ismailPas encore d'évaluation

- Cours Ci Chap1Document8 pagesCours Ci Chap1Amir DridiPas encore d'évaluation

- Microcontrôleur Famille PIC 16oDocument10 pagesMicrocontrôleur Famille PIC 16oAbdellah Faqdani100% (1)

- Du Microprocesseur À La Carte de Prototypage Partie 1: Microprocesseur Et MicrocontrôleurDocument4 pagesDu Microprocesseur À La Carte de Prototypage Partie 1: Microprocesseur Et MicrocontrôleurBsusnksPas encore d'évaluation

- Cours MP - ELECT4Document124 pagesCours MP - ELECT4MoundherNasmlahe100% (1)

- Le Microcontroleur PIC16F876Document13 pagesLe Microcontroleur PIC16F876hmema13Pas encore d'évaluation

- AsservissementDocument2 pagesAsservissementSimo Bouna100% (1)

- Base Des Microcontrôleur2021Document62 pagesBase Des Microcontrôleur2021Ayman LamzouriPas encore d'évaluation

- Le Protocole de La Bus I2CDocument12 pagesLe Protocole de La Bus I2CØûssæmã SâmsøümPas encore d'évaluation

- PIC16F84Document22 pagesPIC16F84Rida bellarranePas encore d'évaluation

- Nouveau Présentation Microsoft PowerPointDocument22 pagesNouveau Présentation Microsoft PowerPointmaiz100% (1)

- Structure Systeme MicropDocument6 pagesStructure Systeme MicropLahoussine ElmahniPas encore d'évaluation

- Cours Projet Electronique 1Document17 pagesCours Projet Electronique 1ryadhPas encore d'évaluation

- Chap 2 Architecture Et Fonctionnement D'un MicroprocesseurDocument12 pagesChap 2 Architecture Et Fonctionnement D'un MicroprocesseurSamen Lempire100% (1)

- Exposé Le MicroprocesseurDocument8 pagesExposé Le MicroprocesseurMamadou Seydou Diallo67% (6)

- 065 Le Microprocesseur-1Document33 pages065 Le Microprocesseur-1Martin LéonardPas encore d'évaluation

- Architecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnDocument47 pagesArchitecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnamalPas encore d'évaluation

- Microprocesseur 6800 Chap1Document6 pagesMicroprocesseur 6800 Chap1Mountasser KhalPas encore d'évaluation

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- Moto 6809Document46 pagesMoto 6809Kawtar FelkiPas encore d'évaluation

- Systemes Microcontroleurs Chap.1 Chap.2Document15 pagesSystemes Microcontroleurs Chap.1 Chap.2MENANI ZineddinePas encore d'évaluation

- Fonction Traitement de L'Information: Le MicroprocesseurDocument10 pagesFonction Traitement de L'Information: Le MicroprocesseurToniPas encore d'évaluation

- 02 - Microcontroleur de La Famille PIC PDFDocument59 pages02 - Microcontroleur de La Famille PIC PDFFarid Afifi100% (1)

- Compte RENDU InformatiqueindutrielDocument21 pagesCompte RENDU InformatiqueindutrielOUTMANE FERNOUCHPas encore d'évaluation

- Le Microprocesseur Power PC750Document21 pagesLe Microprocesseur Power PC750Zinai AbdelatifPas encore d'évaluation

- Les Microcontroleur (Traduction)Document24 pagesLes Microcontroleur (Traduction)Abcp CorpPas encore d'évaluation

- Transformateur À Semi-Conducteurs: Révolutionner le réseau électrique pour la qualité de l'électricité et l'efficacité énergétiqueD'EverandTransformateur À Semi-Conducteurs: Révolutionner le réseau électrique pour la qualité de l'électricité et l'efficacité énergétiquePas encore d'évaluation

- Grille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesD'EverandGrille Intelligente: Échange d'électricité et d'informations entre les maisons et les centrales électriquesPas encore d'évaluation

- Bosse De Pilier En Cuivre Thermique: Refroidissement des zones sensibles des microprocesseurs et des processeurs graphiquesD'EverandBosse De Pilier En Cuivre Thermique: Refroidissement des zones sensibles des microprocesseurs et des processeurs graphiquesPas encore d'évaluation

- Ingénierie Neuromorphique: La pratique consistant à utiliser des systèmes de circuits électriques analogiques pour imiter les structures neurobiologiques présentes dans le système nerveuxD'EverandIngénierie Neuromorphique: La pratique consistant à utiliser des systèmes de circuits électriques analogiques pour imiter les structures neurobiologiques présentes dans le système nerveuxPas encore d'évaluation

- Batterie Lithium Fer Phosphate: Détrôner le lithium-ion dans les véhicules électriques, les mobiles et les ordinateurs portablesD'EverandBatterie Lithium Fer Phosphate: Détrôner le lithium-ion dans les véhicules électriques, les mobiles et les ordinateurs portablesPas encore d'évaluation

- 1-Modes D'adressage: S ° J ' P I 8086Document4 pages1-Modes D'adressage: S ° J ' P I 8086Sara Benseba67% (3)

- MémoireDocument10 pagesMémoiremasckPas encore d'évaluation

- SDM DyDocument116 pagesSDM DyAbdoulaye NiassePas encore d'évaluation

- En-P4 GBM2Document52 pagesEn-P4 GBM2DONIA JBELI100% (1)

- À Retenir: Option-RegDocument2 pagesÀ Retenir: Option-RegMechergui Wissem100% (1)

- Bureau D'etude STM32F4Document227 pagesBureau D'etude STM32F4MARWA BEN HAMMOUDA50% (2)

- ExosSupp CircuitsSéquentiels 2011-2012Document9 pagesExosSupp CircuitsSéquentiels 2011-2012Hamza ToumiPas encore d'évaluation

- Mardi16-Electronique Numerique SER1Document48 pagesMardi16-Electronique Numerique SER1Nabil EL-AKCHIOUIPas encore d'évaluation

- Correctd 3Document8 pagesCorrectd 3Ernest AdouPas encore d'évaluation

- Electronique Numérique Niveau Licence 3Document235 pagesElectronique Numérique Niveau Licence 3yayaPas encore d'évaluation

- EMD STRM2 - 2019 (Rattrapage) (Corrigé)Document4 pagesEMD STRM2 - 2019 (Rattrapage) (Corrigé)nait amara zaidPas encore d'évaluation

- Questions de CoursDocument2 pagesQuestions de CoursbilalPas encore d'évaluation

- Chap2 2Document16 pagesChap2 2SennahPas encore d'évaluation

- Circuit IntégréDocument25 pagesCircuit IntégréDamine Haj Ali100% (1)

- Devoir Corrigé de Contrôle N°2 - Génie Électrique Panneau Solaire Panneau Solaire - Bac Technique (2009-2010) Mme Feki FaizaDocument12 pagesDevoir Corrigé de Contrôle N°2 - Génie Électrique Panneau Solaire Panneau Solaire - Bac Technique (2009-2010) Mme Feki FaizaNesrine NouiraPas encore d'évaluation

- J PortesDocument16 pagesJ PortesBOUCHEFFA HalimPas encore d'évaluation

- Chapitre2 SE DriverHalDocument34 pagesChapitre2 SE DriverHalmehdi abidaPas encore d'évaluation

- Document EleveDocument13 pagesDocument EleveakremibechirPas encore d'évaluation

- ECE 2004-Corrige PDFDocument6 pagesECE 2004-Corrige PDFbaydiPas encore d'évaluation

- TD RevisionDocument2 pagesTD RevisionMãrÿ ŌûmåPas encore d'évaluation

- Corrigé TD2Document3 pagesCorrigé TD2Nihal TaguercifiPas encore d'évaluation

- SignauxDocument13 pagesSignauxUlysse ThorPas encore d'évaluation

- TD1 VHDLLDocument5 pagesTD1 VHDLLMontaha Ben SalemPas encore d'évaluation

- Intra Ele1300 A2013 Corrige PDFDocument17 pagesIntra Ele1300 A2013 Corrige PDFMaxence KouessiPas encore d'évaluation

- Les Fonctions LogiqueDocument7 pagesLes Fonctions LogiqueBOUCHEFFA HalimPas encore d'évaluation

- L2 en Cours 2 Timer555 2 PolyDocument10 pagesL2 en Cours 2 Timer555 2 PolyanassPas encore d'évaluation

- Lpi101frv2 0Document297 pagesLpi101frv2 0chabchoobPas encore d'évaluation

- TH4 1 Aid Act11Document8 pagesTH4 1 Aid Act11Bucky's DollPas encore d'évaluation

- Cours-Microproc 2018Document192 pagesCours-Microproc 2018Badr Eddine EL HAGAOUIPas encore d'évaluation

- Automate TSX 37Document10 pagesAutomate TSX 37Yasser BenioualPas encore d'évaluation