0% ont trouvé ce document utile (0 vote)

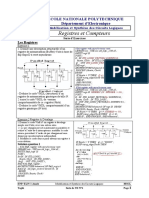

76 vues4 pagesImplémentations Logiques et VHDL

Le document présente une série d'exercices de révision sur la conception de circuits logiques, y compris des implémentations avec des puces 7400, ROM, PLA, PAL et FPGA. Il inclut également des questions sur un programme VHDL, demandant des compléments sur un diagramme de temps et une représentation de design. Enfin, il aborde un circuit séquentiel dont la description et la simulation en VHDL sont demandées.

Transféré par

Zineb BendahganeCopyright

© © All Rights Reserved

Nous prenons très au sérieux les droits relatifs au contenu. Si vous pensez qu’il s’agit de votre contenu, signalez une atteinte au droit d’auteur ici.

Formats disponibles

Téléchargez aux formats PDF, TXT ou lisez en ligne sur Scribd

0% ont trouvé ce document utile (0 vote)

76 vues4 pagesImplémentations Logiques et VHDL

Le document présente une série d'exercices de révision sur la conception de circuits logiques, y compris des implémentations avec des puces 7400, ROM, PLA, PAL et FPGA. Il inclut également des questions sur un programme VHDL, demandant des compléments sur un diagramme de temps et une représentation de design. Enfin, il aborde un circuit séquentiel dont la description et la simulation en VHDL sont demandées.

Transféré par

Zineb BendahganeCopyright

© © All Rights Reserved

Nous prenons très au sérieux les droits relatifs au contenu. Si vous pensez qu’il s’agit de votre contenu, signalez une atteinte au droit d’auteur ici.

Formats disponibles

Téléchargez aux formats PDF, TXT ou lisez en ligne sur Scribd