Académique Documents

Professionnel Documents

Culture Documents

1 Technologie

Transféré par

Hamza BadrTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

1 Technologie

Transféré par

Hamza BadrDroits d'auteur :

Formats disponibles

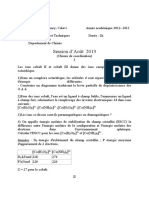

Mthodologie de conception des circuits intgrs VLSI - 1.

Technologie

28/01/10

I Technologie des circuits intgrs

1. Technologie MOS

- Le transistor MOS : prsentation gnrale

- Modle et performances

- Technologies MOS (nMOS, pMOS, CMOS) et volutions

2. Fabrication des circuits intgrs

- Processus de fabrication

- Phnomnes physiques et chimiques

- Exemples d'une diode et de transistors MOS

3. Evolution technologiques

- Evolution des processeurs

- Notion de scaling

31

I.1 Transistor MOS

D

Polysilicon

B

NMOS Enhancement

NMOS Depletion

PMOS Enhancement

Aluminum

NMOS with

Bulk Contact

Types de Transistors

Transistor NMOS

32

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Transistor MOS

demo

33

1.1 Technologie MOS

MOSFET : Metal (Polysilicum) Oxide Silicium Field

Effect Trans.

Vdd

Grille

Mtal

Oxyde (SiO2)

Source

VGS = 0 : Aucune conduction

Roff +

Drain

VGS > Vt (tension de seuil)

N

Champs Grille-Source => accumulation

dlectrons sous la grille

Substrat P

Cration d une zone d inversion le

substrat P devient N sous la grille :

apparition du canal N (e- majoritaires)

G

Canal Induit

D

S

N

Symtrique pour un MOS Canal P (Vgs

< Vt, porteurs : e+)

Substrat

P

Zone Dpeuple

(accepteurs ioniss)

Olivier Sentieys

Apparition d une zone dpeuple dans

le substrat (accepteurs ioniss)

Conduction par porteurs majoritaires

contrairement au bipolaire

34

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Transistors NMOS/PMOS

Transistor nMOS

Transistor PMOS

Vgs < Vt

Vgs > Vdd - Vt

Vgs > Vt

Vgs < Vdd - Vt

Transmission de Niveaux (Source > Drain)

Transmission correcte du 0

Transmission dgrade du 1 (Vdd-Vt)

Transmission correcte du 1

Transmission dgrade du 0 (Vss+Vt)

Porteurs

Electrons

Trous

Polarisation Substrat/Caisson

Vss : 0V

Vdd : 5v

35

1.2 Modles du MOS

L

Grille

D

tox

Diffusion

G

G

Source

Drain

PolySi

W

S

canal

Oxyde

Diffusion N/P

0

2

Vds

Ids =

K

(

Vgs -

Vt ).Vds -

2

K

( Vgs -

Vt ) 2

2

bloqu

Vgs -

Vt

0

linaire

0 <

Vds <

Vgs -

Vt

satur

0 <

Vgs -

Vt <

Vds

L est approxim, tox est lpaisseur de lisolant (#400)

K dpend du process et de la gomtrie du MOS

K = W / tox L = W . k / L

: mobilit des porteurs de charges

NMOS (lectrons) N = 500 cm2 / V-sec # 2 P

PMOS (trous) P = 270 cm2 / V-sec

: permittivit de lisolant # 4 0 = 3,5 10 - 13 F/cm

Transconductance K dpend de W/L

Ids max dpend de W

Temprature : comment voluent et Ids max

36

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Elments parasites du MOS

NMOS Enhancement

CGS

CGD

D

CGB

CSB

CDB

Rsistance drain/source : Ron =

1

1

L

=

K (Vdd Vt ) k (Vdd Vt ) W

.W .L

= W .L.Cox

tox

Capacit drain / source / bulk : Csb = Cdb W .L.Cj

Capacit de grille : Cg =

= Ron.Cg=

L

(Vgs-Vt)

37

MOS SPICE model 1

Expression dIds

Mode

Bloqu

Condition

Vgs < 0

Linaire Vds < Vgs Vt

Satur

Vds > Vgs Vt

Tension de seuil Vt

Expression d ' Ids

Ids = 0

W

Vds 2

Ids = KP (Vgs Vt )Vds

L

2

KP W

(Vgs Vt )2

2 L

Vt = VT 0 + GAMMA + PHI Vb PHI

Paramtre

Dfinition

NMOS 0.25u

PMOS 0.25u

VT0

Tension de seuil

0.4V

-0.4V

KP

Coefficient de transconductance

300A/V2

120A/V2

PHI

Potentiel de surface forte inversion

0.3V

0.3V

GAMMA

Paramtre de seuil du bulk

0.4V0.5

0.4V0.5

Largeur du canal MOS

0.5-20m

0.5-40m

Longueur du canal MOS

0.25m

0.25m

38

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

MOS SPICE model 3

Bloqu

Vgs < 0

Normal Vgs > Von

Ids = 0

W

(1 + KAPPA.Vds )Vde (Vgs Vt ) Vde

Ids = Keff

Leff

2

Von = 1.2 Vt , Vt = VTO + GAMMA PHI Vb PHI

Vde = MIN (Vds, Vdsat ), Vdsat = Vc + Vsat Vc + Vsat 2 , Vsat = Vgs Vt

Leff

KP

Vc = VMAX

, Leff = L 2.LD, Keff =

0.06

1 + THETA(Vgs Vt )

Sous seuil Vgs < Von

W

(1 + KAPPA.Von )Vde (Vgs Vt ) Vde e

Leff

2

Vde = MIN (Von, Vdsat )

Ids = Keff

q (Vgs Von )

nkT

Paramtre

Dfinition

NMOS 0.25u

PMOS 0.25u

LD

Lateral diffusion into channel

0.01m

0.01m

KAPPA

Saturation field vector

0.01V-1

0.01V-1

VMAX

Maximum drift velocity

150km/s

150km/s

THETA

Mobility degradation factor

0.3V-1

0.3V-1

NSS

Subthreshold factor

0.07V-1

0.07V-1

39

1.3 Technologies MOS

Technologie NMOS / PMOS : 1970-1980

Un seul type de transistor N ou P

Rsistances ralises avec NMOS dpltion

Vdd

Transistor dpltion : normalement ouvert

sem

en

t

Ids

N

E

N

Substrat P

D

pl

tio

n

En

ric

his

Inverseur Nmos

Vss

Vgs

Bonne qualit dintgration mais

Difficult dquilibrage des temps de monte et de descente

Transmission imparfaite des niveaux

Consommation en saturation

Do (1980) Technologie CMOS :

association de transistors N et P

40

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

MOS : Technologies

nMOS et pMOS

1970-1980

Un seul type de transistor N ou P

Resistances ralises avec Tr dpletion

inverseur nMOS

S

E

CMOS (Complementary MOS)

1980->

Utilisation de transistors N et P

Trise Tfall si Tn et Tp identiques

inverseur CMOS

Pseudo nMOS

Resistances de charges ralises avec Tr pMOS

Taille des P > Taille des N pour diminuer Rp

MD-MOS (Multi Drains)

Equivalent I2L (bipolaire)

Source de courant en nMOS dpletion

Logique cable type collecteur ouvert

Rp

S

E

Rn

!A

41

Technologies MOS

Technologie CMOS

Transmission parfaite des niveaux

Pmos reli au Vdd assure le passage du 1 pour E=0

Nmos reli au Vss assure le passage du 0 pour E=1

Vdd

Rp

Id

E

E=0

=1

Vss

Marges de bruit excellentes

(VOH=VDD ; VOL=VSS)

marge de bruit :

niveau de bruit pouvant tre support

sans modifier l'entre de la porte suivante.

S=1

=0

Rn

CL

"1"

V

OH

NM H

Marge de bruit haute

Mage de bruit basse

Rgion indfinie

NM L

V

OL

V

IH

IL

"0"

Gate Output

sortie tage N

Gate Input

entre tageN+1

42

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

MOS : autres technologies

BiCMOS

Permet de conjuguer les avantages du bipolaire (rapidit) et du CMOS

(densit, consommation)

Utilisation dun push-pull bipolaire en sortie de cellule

Canal N

S

BiCMOS

AsGa

Technologie AsGa (Arsniure de Gallium)

Mobilit de llectron plus grande que pour Si -> frquences leves

Meilleure tenue en temprature, faibles courant dentres

Temps de propagation symtriques

Mais pas de MESFET canal P

43

MOS : autres technologies

Techniques SOI (Silicon On Insulator)

Dans le CMOS lisolation des caissons entrane des capacits parasites

et des courants de fuite

Utilisation dun isolant comme substrat, roissance pitaxiale de Si sur

isolant

Pas de latchup

Capacits parasites diminuent

Compatible avec CMOS

Solution davenir

Less distance between nMOS

and pMOS

Less capacitance

Less leakage

44

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

I Technologie des CI

1. Technologie MOS

- Le transistor MOS : prsentation gnrale

- Modle et performances

- Technologies MOS (nMOS, pMOS, CMOS) et volutions

2. Fabrication des C.I.

- Processus de fabrication

- Phnomnes physiques et chimiques

- Exemples d'une diode et de transistors MOS

3. Evolution technologiques

- Evolution des processeurs

- Notion de scaling

45

I.2 Comment fabrique t'on un CI ?

Du sable au silicium

Du silicium au circuit intgr

http://www.intel.com/education/makingchips

46

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

I.3

28/01/10

Fabrication des circuits intgrs

Lingot de Silicium (environ 100kg) pur 99,9999999%

Mono-crystal

Silicon Ingot

Ingot slicing

Silicon Wafer

47

I.3

Fabrication des circuits intgrs

Wafer : disque de silicium pure oxyd en surface

(substrat)

Wafer = ensemble de puces (die) isoles entre elles

Gravure identique de toutes les puces

Wafer

Olivier Sentieys

48

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

I.3

28/01/10

Fabrication des circuits intgrs

Contrle sous pointes des puces

49

I.3

Sparation des puces

Montage sous botier protecteur

Soudure du botier

Contrle final

# 20-30cm

Fabrication des circuits intgrs

puce

0,5 1,5 cm

50

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Fabrication des circuits intgrs

Comme l'impression en 3D d'un livre miniature

51

Fabrication des circuits intgrs

52

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Plus propre que propre

Salle blanche

53

Fabrication des circuits intgrs

Phnomnes physiques

Diffusion

Diffusion d'impurets de la surface silicium dans sa masse haute temprature (#1100C) : dopage de type N ou P

impurets de type N: antimoine, phosphore, arsenic

impurets de type P

impurets de type P: bore

Profondeur de la surface la jonction varie de 0,1 20 (Si)

Rsistivit par carr fonction de la distribution des impurets

La diffusion se ralise en gnral travers une fentre (masque)

Implantation ionique

Permet le dopage du Si (# diffusion) par un bombardement de la surface des plaquettes de Si par des ions

d'impurets de type souhait possdant une nergie cintique leve. Ce procd se fait temprature

ambiante suivit d'un recuit basse temprature (450 C) pour rtablir la structure cristalline.

Procds chimiques

Croissance pitaxiale pour les couches enterres

Premiers C.I. bipolaires diffusion triple -> limitation du Tr

L'pitaxie est un procd chimique qui permet de continuer la structure mono-cristalline d'un substrat par

Dposition de couches atomiques additionnelles partir d'une phase gazeuse des tempratures comprises

entre 1000 et 1200 C. On obtient un film pitaxial qui peut tre dop.

Permet de doper le fond des caissons par une couche profonde de faible rsistivit.

Les atomes de Si dposs proviennent de SiCl4 (ttrachlorure de Si) ou de SiH4 (silane) en phase gazeuse. En

moyenne, le film crot d'environ 1m par minute. Les impurets sont mlanges au gaz.

P

N

N+

substrat de type p

Transistor NPN en triple diffusion

Olivier Sentieys

Transistor NPN avec croissance epitaxiale

54

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Fabrication des circuits intgrs

Procds chimiques (suite)

Passivation (oxydation)

Passivation de la surface de silicium par un dilectrique (dioxyde de silicium SiO2) :

oxydation du silicium par de la vapeur d'eau : Si + 2H2O -> SiO2 + 2H2

Ralisation de masques pour la passivation

Protection, isolation, dilectrique des capacits intgres

SiO2

Substrat

Photolithographie

Permet l'limination locale du SiO2.

On recouvre la surface de l'oxyde par une rsine photosensible qui, tant qu'elle n'est

pas polymrise, reste soluble dans certains rvlateurs.

La polymrisation est obtenue par un rayonnement UV travers un masque

photographique.

Rsine

UV

Masque

Gravure sches (Plasma)

55

Exemple : fabrication dune diode

a) Croissance du SiO2

d) Dveloppement de la rsine

SiO2

Substrat

b) Application de la rsine photosensible

Rsine

c) Exposition aux UV travers un masque

UV

e) Gravure du SiO2 par un rvlateur et

dissolution de la rsine

f) Dpt et diffusion des impurets

impurets de type P

Masque

N

56

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

demo

28/01/10

Technologie MOS

Inverseur CMOS O.25 um

58

Fabrication de Transistors MOS N et P

1) Diffusion du Caisson

Caisson N

Tranche de silicium : substrat de type P

2) Croissance d'oxyde de grille 790nm : 1050, 150'

n

SiO2 pais

SiO2 mince

3) Couche de Polysilicium -> grilles des Tr

PolySi

p

Grille

p

Grille

n

59

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Fabrication de Transistors MOS N et P

4)

Diffusion drain et source

n+

n+

p+

5)

p+

p+

Contacts et Interconnexions

n+

n+

p+

SiO2

Contacts Aluminium

p

n+

n+

p+

p+

Mtal 1

60

I Technologie des CI

1. Technologie MOS

- Le transistor MOS : prsentation gnrale

- Modle et performances

- Technologies MOS (nMOS, pMOS, CMOS) et volutions

2. Fabrication des C.I.

- Processus de fabrication

- Phnomnes physiques et chimiques

- Exemples d'une diode et de transistors MOS

3. Evolution technologiques

- Evolution des processeurs

- Notion de scaling

61

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Un transistor et un circuit en vrai!

62

Silicon Technology

0.35 m in 1995, 0.25 m in 1998, 0.18 m in 2000

130 nm in 2002, 90 nm in 2004, 65 nm in 2007

Silicon Atom

45 nm in 2010 (first ship 2008) [ITRS 2009]

5.43 A

11-15 metal levels, wafer 30cm

(0.5 nm)

0.6-0.9 Volts

700 MHz (ASIC) - 9 GHz (on-chip 12 inverters) - 5 GHz (off-chip)

3-4 (MPU), 1 (DRAM) - 4-8 (ASIC) cm2

DRAM: 4Gbits, 4Gbits/cm2, 0.005 $/Mbits

300 (MPU) - 6000 (ASIC) MTr/cm2, 0.05-0.1 $/MTr (MPU)

SRAM: 1500MTr/cm2, 250Mbits/cm2

6000 RISC processors (e.g. ARM7)

32 nm in 2013 (first chip in 2010)

11 nm in 2019-2021 and then ?

Post-Silicon Technologies (nanotechnologies)

63

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Silicon in 2015

Power Supply: 0.6-0.8 V

Technology: 25 nm CMOS (200 Ang.)

20 GTransistors, wafer 45 cm, 2-4 cm2, 13-17 metal levels

Inverter 2.5 ps, 0.6 Volt

33 GHz (on-chip 12 inverters) - 29 GHz (off-chip)

DRAM 16 GBits at 10ns, 0.006 $/Mbits

SRAM (cache) 1 GBits at 1.5ns

256-bit Bus

More than 8500 Person.Month Design Cycle

Software

Mask set is few M$US

64

volutions technologiques

Scaling technologique chaque gnration

Scaling factor : s

Entre deux gnrations successives : s # 0.7

250 nm

180 nm

130 nm

65

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

volutions technologiques

Evolution de la tension dalimentation (Vdd)

5

4.5

4

Voltage

3.5

3

2.5

2

1.5

1

0.5

0

5

0.8

0.6

0.5 0.35 0.25 0.18 0.15 0.13 0.1

Process Geometry

66

Evolutions technologiques

Taille de la puce : x2 tous les 3 ans

Nombre de transistors :

Logique : x2 tous les 3 ans

Mmoire : x4 tous les 3 ans

Vitesse :

Logique : x2 tous les 3 ans

Mmoire : x4 tous les 10 ans

Performance des processeurs

50% par an

67

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

volutions technologiques

Scaling technologique chaque gnration

Frquence augmente de 43%

Capacit totale et tension d'alimentation sont rduites de 30%

nergie rduite de 65%

E = C*Vdd2 = C'*0.7 * (Vdd'*0.7)2 = 0.35*C'*Vdd'2 = 35% E'

Puissance rduite de 50%

P = f*C*Vdd2 = 1.43*f * 0.35*C'*Vdd'2 = 50% P'

On considre que l'activit du circuit est constante

Mais nombre de transistors constant!

Densit de transistor double chaque gnration

Surface des puces augmente de 25%

Densit de puissance augmente avec un facteur 2

Courant d'alimentation augmente de faon importante

68

volutions technologiques

Scaling technologique chaque gnration

Scaling factor : s

Entre deux gnrations successives : s # 0.7

Device dimensions :

W, L, tox, junction depth

Transistor area (W.L)

Capacitance per unit area : Cox

Capacitances : C=WLCox

Vdd, Vt

Gate delay

Power/gate

Power.delay product

Power density

s

s2

1/s

s

s

s

s2

s3

1

69

Olivier Sentieys

Mthodologie de conception des circuits intgrs VLSI - 1. Technologie

28/01/10

Submicronique profond (DSM)

Changement fondamental dans le dlai des composants

Les interconnexions dominent le temps de fonctionnement et la

consommation

Jusqu' 60% du chemin critique du aux interconnexions

Problme pour prdire de manire prcise le routage

Exemple: temps de propagation d'une NAND 2 entres :

connect 2mm de mtal : 280 ps

connect 0.5mm de mtal : 119 ps

DSM implique un comportement non linaire des portes

Cuivre, augmentation du nombre de niveaux de mtal

70

Olivier Sentieys

Vous aimerez peut-être aussi

- Travaux PratiqueDocument30 pagesTravaux Pratiqueيس محمدPas encore d'évaluation

- CORRECTION Evaluation N°3 de Physique-Chimie: Exercice 1 - Mélange de Produits Ménagers: Attention Dangers!Document5 pagesCORRECTION Evaluation N°3 de Physique-Chimie: Exercice 1 - Mélange de Produits Ménagers: Attention Dangers!Hakimi AbderrahmanePas encore d'évaluation

- FPGA HandoutDocument58 pagesFPGA HandoutHamza BadrPas encore d'évaluation

- MI Cours Reseau Cours1 PDFDocument32 pagesMI Cours Reseau Cours1 PDFHamza BadrPas encore d'évaluation

- Archi Cours5Document21 pagesArchi Cours5Hamza BadrPas encore d'évaluation

- (Unknown) Les Réseaux de NeuronesDocument27 pages(Unknown) Les Réseaux de NeuronesKhalifa Bakkar100% (1)

- 2012PFE Elhassani ImaneDocument56 pages2012PFE Elhassani ImaneHamza BadrPas encore d'évaluation

- Za 7Document7 pagesZa 7Hamza BadrPas encore d'évaluation

- Chapitre 4 Mouvement Des Satellites Et Des PlaDocument6 pagesChapitre 4 Mouvement Des Satellites Et Des PlaHamza BadrPas encore d'évaluation

- UE1 BCH1 03 Chap 2 Config Electronique PDFDocument29 pagesUE1 BCH1 03 Chap 2 Config Electronique PDFHamza BadrPas encore d'évaluation

- Transfert Thermique Exercices04Document2 pagesTransfert Thermique Exercices04kridatimaPas encore d'évaluation

- St-Fa1 Principes de La Fabrication Additive-DuoDocument2 pagesSt-Fa1 Principes de La Fabrication Additive-DuoBoussalem MeryemePas encore d'évaluation

- These CadiDocument139 pagesThese CadiHeisenberg WWPas encore d'évaluation

- Is 877583Document2 pagesIs 877583ZakariaAllakiPas encore d'évaluation

- Exercices SVT 5eDocument2 pagesExercices SVT 5eBaye Faly FALL0% (1)

- Mfi M1 2005Document63 pagesMfi M1 2005Ludovic ChatellierPas encore d'évaluation

- 2 DynamicPart1Reactulise20Document5 pages2 DynamicPart1Reactulise20Said Benamour TopoPas encore d'évaluation

- Équipements de Chauffage Et Locaux TechniqueDocument13 pagesÉquipements de Chauffage Et Locaux Techniquebaho btwPas encore d'évaluation

- 2022 Tle Spã© Chapitre 12 Dynamique D Un Circuit ElectriqueDocument5 pages2022 Tle Spã© Chapitre 12 Dynamique D Un Circuit Electriquemavrinissue4Pas encore d'évaluation

- Partie 6 Chap 5 Les DosagesDocument44 pagesPartie 6 Chap 5 Les DosagesdPas encore d'évaluation

- 12 Les EvaporateursDocument13 pages12 Les EvaporateursakroudPas encore d'évaluation

- DCN1 2022Document5 pagesDCN1 2022briki faical briki faicalPas encore d'évaluation

- TD Sur Les CarbonylesDocument2 pagesTD Sur Les CarbonylesDEMBA SYLLAPas encore d'évaluation

- tp06 PDFDocument7 pagestp06 PDFmadPas encore d'évaluation

- 27 Corrosion Td-EnonceDocument7 pages27 Corrosion Td-EnonceAbdo Aiaiche100% (2)

- TPE M.Daouas 2 - CopieDocument56 pagesTPE M.Daouas 2 - CopieChourouk MeskiniPas encore d'évaluation

- Oem Dlhi 1Document7 pagesOem Dlhi 1Udei SchikhauiPas encore d'évaluation

- AoutDocument2 pagesAoutBaroka julien YANEPas encore d'évaluation

- Fascicule Segpa 3eme 2018 ElectriciteDocument20 pagesFascicule Segpa 3eme 2018 ElectriciteGregory CollinPas encore d'évaluation

- Polymérisation en Émulsion GMP 18Document17 pagesPolymérisation en Émulsion GMP 18mennanesalaheddinePas encore d'évaluation

- Stéréochimie Isomérie Conformationnelle-1Document17 pagesStéréochimie Isomérie Conformationnelle-1adnan aitlahcPas encore d'évaluation

- CataloguePrepasScientifiques 2023 BD+Document32 pagesCataloguePrepasScientifiques 2023 BD+lotfi elasriPas encore d'évaluation

- Metallographie SDMDocument13 pagesMetallographie SDMYoucef YoucefPas encore d'évaluation

- STDHX5000M - Analyseur de Ciments Par Fluorescence-X de Paillasse, Equipe D'un Detecteur SSD A Purge HeliumDocument3 pagesSTDHX5000M - Analyseur de Ciments Par Fluorescence-X de Paillasse, Equipe D'un Detecteur SSD A Purge HeliumFrançois VergonPas encore d'évaluation

- Rapport de Stage Dans ONA TouggourtDocument20 pagesRapport de Stage Dans ONA TouggourtAmira KrimaPas encore d'évaluation

- Corrosion 2Document20 pagesCorrosion 2Abdellah El khamlichiPas encore d'évaluation

- TD MQ L2 2019 PDFDocument27 pagesTD MQ L2 2019 PDFLamine GuéyePas encore d'évaluation

- Exo Type BacDocument3 pagesExo Type Baciwiw.btpPas encore d'évaluation