Académique Documents

Professionnel Documents

Culture Documents

Ex Corrigé

Transféré par

Hamza RahaliCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Ex Corrigé

Transféré par

Hamza RahaliDroits d'auteur :

Formats disponibles

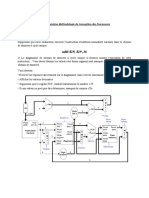

Le DLX est un processeur RISC 32 bits.

On y retrouve nombre des principes architecturaux qui

y sont mis en œuvre dans des processeurs tels que les MIPS ou les PowerPC.

Le DLX comporte 5 niveaux de pipeline qui sont détaillés sur la figure suivante :

Architecture DLX simplifiée

Cette architecture est celle d’une machine “pédagogique”. Elle est dotée de :

- 32 registres entiers 32 bits (R0 est spécial et important : son contenu est 0 !) ;

- 32 registres flottants 32 bits (non représentés dans la figure) ;

- Les instructions arithmétiques et logiques ne peuvent pas s’effectuer en

mémoire ;

- Les opérations arithmétiques et logiques comportent 3 opérandes ;

- Les modes d’adressage sont les suivants :

o Immédiat : add r1,r2,#5 ; // r1 := r2+5

o Par registres : add r1,r2,r3 ; // r1 := r2+r3

o Déplacement : lw r1,22(r2) ; // r1 := [r2+22]

o Indirection : sw 0(r1),r2 ; // r2 ! [r1]

o Absolu : lw r12,2004(r0) ; // r12 := [2004]

Les cinq phases du pipeline exécutent les opérations suivantes :

1- Fetch (F) : lecture instruction ;

The next instruction to be executed is read from the instruction memory at the address pointed by the Program

Counter(PC) register. The next address is computed as the current address plus 4 or the value coming from

the next stage if a jump has to be executed.

2- Decode (D) : décodage et accès aux registres impliqués dans l’instruction ;

The instruction coming from the IF stage is decoded and the register file is accessed. Conditional branches

are also evaluated in this stage and the jump address is computed and sent back to the IF stage.

3- Execute (E) : exécution des opérations arithmétiques et calcul d’adresses ;

Logic and arithmetic operations are executed on the operand coming from the ID stage. The result of this

operation can either be a value to be written back in the register file or the address of the data memory to be

accessed in the next stage.

4- Memory (M) : accès à la mémoire. Pour les branchements, c’est dans cette phase que

s’effectue la modification du compteur ordinal ;

Data memory is accessed (either read or write).

5- Write back (W) : écriture des résultats dans les registres.

The value to be written in the register file (if any) is sent back to the ID stage.

I/Pipeline d’instructions

Soit la boucle suivante :

etiq : LW R1, 10(R2)

ADDI R1, R1, #1

SW R1, 10(R2)

ADDI R2, R2, #4

SUB R4, R3, R2

LW R5, 10(R6)

BNZ R4, etiq

1- La spécification des instructions est donnée par le tableau suivant :

Instructions pouvant Signification Cycle du pipeline

être pipelinées où l’opération

termine (le résultat

étant disponible 1

cycle plus tard)

LW R1, 10(R2) R1 :=Mem[10+R2] W

ADDI R1, R1, #1 R1 :=R1+1 W

SW R1, 10(R2) Mem[10+R2] :=R1 M

SUB R4, R3, R2 R4 :=R3-R2 W

BNZ R4, etiq Branchement si non zéro E

Dresser dans un tableau la trace de l’exécution de cette boucle en utilisant au besoin

des suspensions (rupture de séquence). Pour l’instruction de branchement, considérez

que le pipeline suspend en attendant la fin de toutes les instructions de la boucle. En

déduire le nombre de cycles d’horloge requis pour l’exécution de cette boucle

Cycle d’horloge 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

LW R1, 10(R2) F D E M W

ADDI R1, R1, #1 F D ! ! E M W

SW R1, 10(R2) F ! ! D E ! M W

ADDI R2, R2, #4 F D ! E M W

SUB R4, R3, R2 F ! D ! ! E M W

LW R5, 10(R6) F ! ! D E M W

BNZ R4, etiq F D ! E M W

LW R1, 10(R2) ! ! ! F D

Ou

Instruction x

Pas de prédiction du

branchement ->

exécution de la

boucle en 15 cycles

d’horloge

LW R1, 10(R2) F D E M W

Avec prédiction de

branchement

exécution de la

boucle en 12 cycles

d’horloge

ADDI R1, R1, #1 F …

2- Une nouvelle spécification des instructions est considérée dans le tableau suivant :

Instructions pouvant Signification Cycle du pipeline

être pipelinées où l’opération

termine

LW R1, 10(R2) R1 :=Mem[10+R2] W

ADDI R1, R1, #1 R1 :=R1+1 E

SW R1, 10(R2) Mem[10+R2] :=R1 M

SUB R4, R3, R2 R4 :=R3-R2 E

BNZ R4, etiq Branchement si non zéro D

Dresser la trace d’exécution de cette boucle et déduire le nouveau nombre de cycles.

En considère dans ce cas une politique de prédiction de branchement pris.

Cycle d’horloge 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

LW R1, 10(R2)

ADDI R1, R1, #1

SW R1, 10(R2)

ADDI R2, R2, #4

SUB R4, R3, R2

LW R5, 10(R6)

BNZ R4, etiq

Vous aimerez peut-être aussi

- Formation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesD'EverandFormation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesPas encore d'évaluation

- Exercice PipelineDocument3 pagesExercice PipelineHamza Rahali100% (1)

- Tdprocesseur 001Document4 pagesTdprocesseur 001lifekingPas encore d'évaluation

- Exercices Comp 1Document4 pagesExercices Comp 1ziribologhin2014Pas encore d'évaluation

- Architecture Des Ordinateurs: Exercices: Exercices Sur La Partie Langage D'assemblageDocument11 pagesArchitecture Des Ordinateurs: Exercices: Exercices Sur La Partie Langage D'assemblageNouzha BoukoubaPas encore d'évaluation

- Examen AO Corrig Univ Guelma 2018Document6 pagesExamen AO Corrig Univ Guelma 2018Siaka Dycosh BertePas encore d'évaluation

- Serie2 2021-2022Document3 pagesSerie2 2021-2022ikram HERAOUAPas encore d'évaluation

- Correction Rattrapage 2013Document10 pagesCorrection Rattrapage 2013abir cherifPas encore d'évaluation

- TP 5 Realisation Modulation FM À VaricapDocument3 pagesTP 5 Realisation Modulation FM À VaricapYves AbrahamPas encore d'évaluation

- Remarques Et Astuces de Programmation en AssembleurDocument31 pagesRemarques Et Astuces de Programmation en AssembleuramaniPas encore d'évaluation

- Command LineDocument199 pagesCommand LineDIMI EKONGA NZELLYPas encore d'évaluation

- Le Microprocesseur 8086Document22 pagesLe Microprocesseur 8086Merbai YassinePas encore d'évaluation

- CC2 Ex1Document7 pagesCC2 Ex1kingfak100% (1)

- Examen Automatique Session Du PrintempsDocument3 pagesExamen Automatique Session Du PrintempsZakaria Belyamani100% (1)

- AlgorithmiqueDocument184 pagesAlgorithmiquemanel fitouriPas encore d'évaluation

- Partiels2a PDFDocument314 pagesPartiels2a PDFchfakhtPas encore d'évaluation

- TP4 Atelier MCPDocument6 pagesTP4 Atelier MCPmohamedPas encore d'évaluation

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihPas encore d'évaluation

- Chapitre 1Document13 pagesChapitre 1Dhafer MezghaniPas encore d'évaluation

- Analyses VH DDocument10 pagesAnalyses VH DMustapha El IdrissiPas encore d'évaluation

- CircombrevsolDocument9 pagesCircombrevsolrahma kaabi100% (1)

- Cours - Microcontroleur - PIC-16F887 - 2018 - 2019 VFDocument316 pagesCours - Microcontroleur - PIC-16F887 - 2018 - 2019 VFoassarikhiPas encore d'évaluation

- PDF Le Grafcet Cours Exercices Corriges - TextmarkDocument186 pagesPDF Le Grafcet Cours Exercices Corriges - Textmarkousmane kanePas encore d'évaluation

- Introduction Freertos 2Document28 pagesIntroduction Freertos 2jtohnPas encore d'évaluation

- Examen 2013 (ACAD)Document4 pagesExamen 2013 (ACAD)zakiPas encore d'évaluation

- TD1Document2 pagesTD1Abdelfatah FerhatPas encore d'évaluation

- Introduction À L'automatismeDocument10 pagesIntroduction À L'automatismeTBG GadjiPas encore d'évaluation

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaPas encore d'évaluation

- Cours DSP 2020-Programmation - 43Document44 pagesCours DSP 2020-Programmation - 43Youssef Mahdi0% (1)

- Corrige td1 PDFDocument3 pagesCorrige td1 PDFKhaoula TergouPas encore d'évaluation

- TD 2 Complémentaire SoC MulticyckeDocument10 pagesTD 2 Complémentaire SoC MulticyckeDhafer MezghaniPas encore d'évaluation

- Jeu D - Instructions Du PIC16F84ADocument9 pagesJeu D - Instructions Du PIC16F84AOMAR ENNAJIPas encore d'évaluation

- Exercice 1: Les Interruptions LogiciellesDocument2 pagesExercice 1: Les Interruptions LogiciellesMounia ChakkourPas encore d'évaluation

- Devoir RLE1Document3 pagesDevoir RLE1assouoPas encore d'évaluation

- TP Initiation Langage C Sur PIC CorrectionDocument10 pagesTP Initiation Langage C Sur PIC CorrectionSofiane AbmPas encore d'évaluation

- 2015 2016 Graphe TD6 OptimationDocument5 pages2015 2016 Graphe TD6 OptimationSa LimPas encore d'évaluation

- 3 Diagrammes UML v2022-23 (Classes Et Objets)Document74 pages3 Diagrammes UML v2022-23 (Classes Et Objets)watsopPas encore d'évaluation

- Projet VHDLDocument6 pagesProjet VHDLFadwa JabriPas encore d'évaluation

- Intro Mémoire ProcesseurDocument209 pagesIntro Mémoire ProcesseurImane el omariPas encore d'évaluation

- Examen Rattrapage IE5 2020 FinalDocument9 pagesExamen Rattrapage IE5 2020 FinalDhafer MezghaniPas encore d'évaluation

- Test n2 Correction Reduit2 PDFDocument10 pagesTest n2 Correction Reduit2 PDFSoufiane BoulachgourPas encore d'évaluation

- Travaux Dirigés FPGA & VHDL - 2Document28 pagesTravaux Dirigés FPGA & VHDL - 2simohamed1993Pas encore d'évaluation

- Ex 1 TP 3 DSPDocument4 pagesEx 1 TP 3 DSPAmineSlamaPas encore d'évaluation

- Travaux Diriges Sur Les Reseaux Locaux Et Les Reseaux Hauts DebitsDocument3 pagesTravaux Diriges Sur Les Reseaux Locaux Et Les Reseaux Hauts DebitsBarry Seidou JacquesPas encore d'évaluation

- TD Jeux Dinstruction 2021 22Document5 pagesTD Jeux Dinstruction 2021 22Sarah Ben BelaidPas encore d'évaluation

- TP2Document8 pagesTP2Zouhair IguerhzifenPas encore d'évaluation

- TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Document15 pagesTP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Smart ClassePas encore d'évaluation

- Examen MP1ERTA Janvier 2020 FinalDocument9 pagesExamen MP1ERTA Janvier 2020 FinalDhafer MezghaniPas encore d'évaluation

- Bascule JK Maître EsclaveDocument8 pagesBascule JK Maître EsclaveMafiazoPas encore d'évaluation

- Examen MIPS 2019Document8 pagesExamen MIPS 2019Wael KhemakhemPas encore d'évaluation

- GNS 3Document38 pagesGNS 3jaouad AGHLALAPas encore d'évaluation

- 29 Pldpal2Document14 pages29 Pldpal2Amina GhardallouPas encore d'évaluation

- Série de Révision Méthodologie de Conception Des ProcesseursDocument6 pagesSérie de Révision Méthodologie de Conception Des ProcesseursmezghaniPas encore d'évaluation

- Serie TD6Document7 pagesSerie TD6Sarah NourPas encore d'évaluation

- Chap5 Description StructurelleDocument25 pagesChap5 Description StructurelleNajlaealalawiPas encore d'évaluation

- Janvier 2005 ExamDocument4 pagesJanvier 2005 ExamYassine AmrPas encore d'évaluation

- Corrige Exam 2005Document6 pagesCorrige Exam 2005Yassine AmrPas encore d'évaluation

- Exam 2008Document4 pagesExam 2008Yassine AmrPas encore d'évaluation

- TD 2Document5 pagesTD 2adda chariPas encore d'évaluation

- Oxymètre de PoulsDocument7 pagesOxymètre de PoulsHamza RahaliPas encore d'évaluation

- Chapitre I Introduction Aux Systèmes EmbarquésDocument27 pagesChapitre I Introduction Aux Systèmes EmbarquésHamza RahaliPas encore d'évaluation

- Acfrogbomoqtev40hikghc3covwhsdznviwifokez75jhwpsg2grvi68z7emfz Wsd32dift9jiiirnuryqhvs071f8a8uxi7xpfjnwjy Kxbucsdlyz3mgfay9jz Y7uiyhzzdmf2 Fls1ijnDocument26 pagesAcfrogbomoqtev40hikghc3covwhsdznviwifokez75jhwpsg2grvi68z7emfz Wsd32dift9jiiirnuryqhvs071f8a8uxi7xpfjnwjy Kxbucsdlyz3mgfay9jz Y7uiyhzzdmf2 Fls1ijnHamza RahaliPas encore d'évaluation

- Exemple de Spécifications Fonctionnelle Et TechniqueDocument11 pagesExemple de Spécifications Fonctionnelle Et TechniqueHamza RahaliPas encore d'évaluation

- Oxymètre de PoulsDocument7 pagesOxymètre de PoulsHamza RahaliPas encore d'évaluation

- CV Hamza Rahali FDocument1 pageCV Hamza Rahali FHamza RahaliPas encore d'évaluation

- CV Hamza RahaliDocument1 pageCV Hamza RahaliHamza RahaliPas encore d'évaluation

- CH 3Document80 pagesCH 3Hamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- Chapitre 4 Caracterisation Des Materiaux CompositesDocument15 pagesChapitre 4 Caracterisation Des Materiaux CompositesYounessElkarkouriPas encore d'évaluation

- Chapitre I Introduction Aux Systèmes EmbarquésDocument27 pagesChapitre I Introduction Aux Systèmes EmbarquésHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- CV Hamza Rahali CFDocument1 pageCV Hamza Rahali CFHamza RahaliPas encore d'évaluation

- Cours de Topographie Et Topométrie GénéraleDocument65 pagesCours de Topographie Et Topométrie GénéraleMay KodoPas encore d'évaluation

- Ds-Ex TopoDocument65 pagesDs-Ex TopoSofiene Guedri67% (3)

- CV Hamza Rahali CFDocument1 pageCV Hamza Rahali CFHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- Poplycopie Kaid NoriaDocument98 pagesPoplycopie Kaid Noriaferhati100% (3)

- Emploi S15 &16 (15 Au 20-01-2021) Classes VF PDFDocument9 pagesEmploi S15 &16 (15 Au 20-01-2021) Classes VF PDFHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- Topo CoursDocument90 pagesTopo CoursḾøķhtàriHƿkPas encore d'évaluation

- Exercices RedressementDocument23 pagesExercices Redressementarnaud2990% (10)

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- Défi Logo ENIB (Dec. 2020) PDFDocument2 pagesDéfi Logo ENIB (Dec. 2020) PDFHamza RahaliPas encore d'évaluation

- Emploi S15 &16 (15 Au 20-01-2021) Classes VF PDFDocument9 pagesEmploi S15 &16 (15 Au 20-01-2021) Classes VF PDFHamza RahaliPas encore d'évaluation

- TdSQLCorrection PDFDocument2 pagesTdSQLCorrection PDFHamza RahaliPas encore d'évaluation

- MCSEDI Formation Mcse Desktop Infrastructure PDFDocument6 pagesMCSEDI Formation Mcse Desktop Infrastructure PDFCertyouFormationPas encore d'évaluation

- CCNA2 - Chapitre 3Document7 pagesCCNA2 - Chapitre 3Narjiss Hach100% (1)

- Ligne de Commandes Linux.Document23 pagesLigne de Commandes Linux.titusPas encore d'évaluation

- Fiche Formation Fcourtes Iut Geii Systeme Dexploitation Temps Reel Rtos PDFDocument1 pageFiche Formation Fcourtes Iut Geii Systeme Dexploitation Temps Reel Rtos PDFEylul MoodPas encore d'évaluation

- TP Sécurité MasterDocument5 pagesTP Sécurité Masterr00TPas encore d'évaluation

- Ofppt Ofppt: Royaume Du MarocDocument85 pagesOfppt Ofppt: Royaume Du MarocYoussef ElhaddajiPas encore d'évaluation

- TP Agrgation de Liens-Stp-Routage Inter-VlanDocument9 pagesTP Agrgation de Liens-Stp-Routage Inter-Vlanapi-247116054Pas encore d'évaluation

- Préparation À La Certification LPIC-2Document26 pagesPréparation À La Certification LPIC-2Trong Oganort Gampoula0% (1)

- Cahier Des Charges Stockage Sauvegarde 12202013 22de25Document19 pagesCahier Des Charges Stockage Sauvegarde 12202013 22de25Marouani AmorPas encore d'évaluation

- Exercice 1: Tssri-Reseaux@Document3 pagesExercice 1: Tssri-Reseaux@radouanePas encore d'évaluation

- Product PDFDocument4 pagesProduct PDFaaou4250Pas encore d'évaluation

- MODULE Microcontroleur MMOAMPADocument131 pagesMODULE Microcontroleur MMOAMPAMycompte HukkersPas encore d'évaluation

- 6.8.2 Lab - Configure NAT For IPv4 - ILMDocument18 pages6.8.2 Lab - Configure NAT For IPv4 - ILMmarvin ranokePas encore d'évaluation

- Cours Cisco CCNA2Document203 pagesCours Cisco CCNA2samireverPas encore d'évaluation

- Réponses Aux Questions de L'épreuve de Linux DOURMADocument7 pagesRéponses Aux Questions de L'épreuve de Linux DOURMACrypto SylvainPas encore d'évaluation

- Série Supplémentaire 1Document2 pagesSérie Supplémentaire 1Nadjah NamanePas encore d'évaluation

- Cours Java Gestion Des FluxDocument26 pagesCours Java Gestion Des Fluxyves1ndriPas encore d'évaluation

- Fiche de Pote InformatDocument4 pagesFiche de Pote InformatBaye Guy Ange Henoc YoboPas encore d'évaluation

- TP Powershell Par Khalid KatkoutDocument7 pagesTP Powershell Par Khalid KatkoutMoussa67% (3)

- TS612G Formation Ibm Tivoli Storage Manager 6 3 TSM Implementation Et AdministrationDocument2 pagesTS612G Formation Ibm Tivoli Storage Manager 6 3 TSM Implementation Et AdministrationCertyouFormationPas encore d'évaluation

- 2ème SI InformatiqueDocument240 pages2ème SI Informatiqueafrouk10% (1)

- SyllabusDocument4 pagesSyllabusdakirPas encore d'évaluation

- Système D'exploitation La Gestion Des Entrées Et Sorties Série TD1Document3 pagesSystème D'exploitation La Gestion Des Entrées Et Sorties Série TD1Manel El AzizPas encore d'évaluation

- LandTiger Programmation - rr1Document122 pagesLandTiger Programmation - rr1nad_chadi8816Pas encore d'évaluation

- Anatomie Du PC 2 L'unite Centrale - CopieDocument14 pagesAnatomie Du PC 2 L'unite Centrale - Copiesteve memgbaPas encore d'évaluation

- TP de Supervision Prometheus GrafanaDocument4 pagesTP de Supervision Prometheus GrafanavtinomoevarePas encore d'évaluation

- Cours Sys ThreadsDocument22 pagesCours Sys ThreadsLounes AmazighPas encore d'évaluation

- 7 SpiDocument3 pages7 SpiCHADDOUPas encore d'évaluation

- F12038-1 - Lancement Gamme ZeusDocument37 pagesF12038-1 - Lancement Gamme ZeusLaurent FARAUDPas encore d'évaluation

- WAB Admin Guide FRDocument142 pagesWAB Admin Guide FRAziz RhazlaniPas encore d'évaluation

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Manuel de fabrication du savon: Je fabrique mes savons facilementD'EverandManuel de fabrication du savon: Je fabrique mes savons facilementÉvaluation : 5 sur 5 étoiles5/5 (4)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- Kali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.D'EverandKali Linux pour débutant : Le guide ultime du débutant pour apprendre les bases de Kali Linux.Évaluation : 5 sur 5 étoiles5/5 (1)

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Gestion de projet : outils pour la vie quotidienneD'EverandGestion de projet : outils pour la vie quotidienneÉvaluation : 5 sur 5 étoiles5/5 (2)

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)

- La psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsD'EverandLa psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsPas encore d'évaluation

- Marketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxD'EverandMarketing: Guide Pour Gagner De L'argent En Ligne Avec Les Réseaux SociauxPas encore d'évaluation

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Le plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentD'EverandLe plan marketing en 4 étapes: Stratégies et étapes clés pour créer des plans de marketing qui fonctionnentPas encore d'évaluation