Académique Documents

Professionnel Documents

Culture Documents

Corrigé Examen Systèmes Logiques 1 GE11 15 Janvier 2023

Transféré par

Khalil Haj nasserCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Corrigé Examen Systèmes Logiques 1 GE11 15 Janvier 2023

Transféré par

Khalil Haj nasserDroits d'auteur :

Formats disponibles

INSTITUT SUPÉRIEUR DES ETUDES

EXAMEN JANVIER 2023 TECHNOLOGIQUES DE NABEUL

DÉPARTEMENT : GE

Module : Systèmes logiques 1 Documents autorisés : Non Oui

Groupes : GE11–GE12–GE13–GE14–GE15 Calculatrices autorisées : Non Oui

Date : Jeudi 5 Janvier 2023 Nombre de pages : 8

Heure : 13 h 30 15 h 00 Barème : Ex1 (5 points), Ex2 (6 points), Ex2 (9 points)

Enseignants : Mrs H. AMMAR/Kh. MNASSRI/S. BEN ABDALLAH

Nom : -------------------------------- Prénom : ------------------------------------ Classe : -----------

Code :

Code :

………………………

Soignez votre écriture et votre traçage des schémas. Encadrez la réponse obtenue pour chaque question.

Exercice 1 (5 pts) :

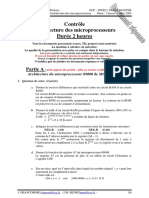

1. âblage du circuit (1pt).

VCC VCC

16 16

10 10

Données D

D0

Données D

D0 A0 A0

D1 12 D1 12 A1

A1

13

Entrées de mise en cascade

D2 13 A2 7485 D2 A2 7485

Entrées de mise en cascade

+5V D3 15 +5V D3 15 A3

A3

Q

2 5 2 A>B A>B 5

A>B A>B

Sorties

Sorties

3 6 3 A=B A=B 6

A=B A=B

4 7 4 A<B A<B 7

A<B A<B

9 9 B0

B0

11 11 2

B1 B1

14 14

B2 B2

1 1

B3 B3

8 8

>>> 1/6 <<<

2. La forme canonique de la sortie Q (1pt).

Q D3D2D1D0 D3D2DD

1 0 D3D2DD

1 0 D3D2DD

1 0 D3D2D1D0 D3D2DD

1 0

m0 m1 m2 m3 m4 m5 1

1 0 D3D2DD

D3D2DD 1 0 D3D2DD

1 0 DD

3 2D1D0 DD 1 0 DD

3 2DD 1 0

3 2DD

m9 m10 m11 m12 m13 m14

DD

3 2DD

1 0

m15

3. La fonction Q par le tableau de Karnaugh (2 pts).

D1D0

00 01 11 10

D3D2

00 1 1 1 1 1

01 1 1 0 0

11 1 1 1 1

10 0 1 1 1

Q

Q D3D2 DD

3 2 D3D1 DD

3 1 DD

3 0

QD2 D3 D3 D0 D1D1D3

1

̅ ̅ ̅ ; ̅ ̅ ̅ ̅

Exercice 2 (6 pts):

On considère le montage de la figure suivante (X étant un nombre binaire codé sur quatre bits, tel que :

X= ( d c b a )2 avec « a » le bit de poids le plus faible (LSB) et « d » le bit MSB.

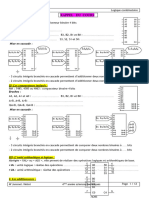

1. Etablissement des équations à la sortie de chaque porte logique (1 pt).

X

d c b a

1

ac

a c b d

bd F a c b d a c b d

ac

a c b d

bd

2. La fonction logique F (1 pt).

F abad cbcd abd cbd 1

>>> 2/6 <<<

3. La forme canonique de F de plus faible au plus fort poids (1 pt).

F abcd abcd abcd abcd abcd abcd abcd abcd abcd abcd 1

m2 m3 m6 m8 m9 m10 m11 m12 m13 m14

4. Trouver l’équation simplifiée de la sortie F (par Karnaugh ou par méthode algébrique) (2 pts).

5.

ba

00 01 11 10

dc

00 0 0 1 1 1

01 0 0 0 1

11 1 1 0 1

10 1 1 1 1

F

F cd abbd bc F cbd abbd 1

5. Réalisation de la fonction F par l’utilisation d’un multiplexeur 16 vers 1 (1 pt).

+Vcc

A0

A1

A2

A3

A4

A5

A6

A7

Mux

A8 S F

A9 16 vers 1

A10

A11

A12 1

A13

A14

A15

d c b a

Exercice 3 (9 pts):

1. Equations de sorties des trois multiplexeurs en fonction des entrées A, B, C et D. (1,5 pt)

S1 AB AB AB 0,5

S2 CD 0,5

S3 AB AB A B 0,5

2. Expression logique de la sortie S3 sous la 1ère forme canonique de plus faible au plus fort poids. (1 pt)

S3 m , m , m , m , m , m , m , m

0 3 4 7 8 12 13 15

S3 ABCD ABCD ABCD ABCD ABCD ABCD ABCD ABCD 1

m0 m3 m4 m7 m8 m11 m12 m15

>>> 3/6 <<<

3. La table de vérité des trois sorties S1, S2 et S3. (3 pts).

0,5 0,5 1

1

mi D C B A S1 S2 S3

m0 0 0 0 0 0 1 1

m1 0 0 0 1 1 1 0

m2 0 0 1 0 1 1 0

m3 0 0 1 1 0 1 1

m4 0 1 0 0 0 0 1

m5 0 1 0 1 1 0 0

m6 0 1 1 0 1 0 0

m7 0 1 1 1 0 0 1

m8 1 0 0 0 0 0 1

m9 1 0 0 1 1 0 0

m10 1 0 1 0 1 0 0

m11 1 0 1 1 0 0 1

m12 1 1 0 0 0 0 1

m13 1 1 0 1 1 0 0

m14 1 1 1 0 1 0 0

m15 1 1 1 1 0 0 1

4. Réalisation de la fonction S3 à base de deux décodeurs 1 parmi 8 (74138 - Annexe B), d'un inverseur et

d'une porte logique "OU" et de deux portes logiques "NAND" à plusieurs entrées. (1 pt)

1

O0 O0

A A0 O1 A0 O1

B A1 O2 A1 O2

C A2 Décodeur A2 Décodeur

74138 O3 74138 O3

O4 O4 S3

E1 1 parmi 8 E1 1 parmi 8

E2 O5 E2 O5

O6 O6

D E3 E3

O7 O7

>>> 4/6 <<<

5. Etablissement des logigrammes de S3 à base des multiplexeurs suivants :

a. d’un seul multiplexeur 16 vers 1. (1 pt) b. d’un multiplexeur 8 vers 1. (0,5 pt)

Puisque la sortie S3 ne dépond que des entrées A

Par l’utilisation d’un multiplexeur 16 vers 1

et B, on peut réaliser alors la fonction par

dont il possède quatre bits d’adressage, les

l’utilisation d’un simple multiplexeur 8 vers 1 dont

mintermes ne se multiplient qu’avec 1 (qui

il possède deux bits d’adressage. Les mintermes

correspond à Vcc) ou 0 (qui correspond à la

seront multiplient dans ce cas par 1 (c.à.d. Vcc) ou

masse).

par 0 (c.à.d. la masse).

+Vcc

+Vcc

A0 0,5

A1 1 A0

A2

A3 A1

A4

A5 A2

A6

A7

Mux A3 Mux

A8 S S3 S

A9 16 vers 1 A4 S3

A10 8 vers 1

A11 A5

A12 A6

A13

A14 A7

A15

D C B A D C B A

c. D’un seul multiplexeur 4 vers 1. (0,5 pt) d. uniquement de trois multiplexeurs 2 vers

Puisque les mintermes du multiplexeur 8 vers 1. (0,5 pt)

1 m0=m4, m1=m5, m2=m6 et m 3=m7, il peut Tout multiplexeur 4 vers 1 peut être remplacé

être remplacé par un seul multiplexeur 4 vers par trois multiplexeurs 2 vers 1.

1. Les entrées ne seront connectées qu’avec 0L

+Vcc

ou 1L.

0,5

+Vcc 0,5

A0 Mux

S

A1 2 vers 1

A0

A0 Mux

A1 Mux S S S3

A2

S3 B A1 2 vers 1

4 vers 1

A3

A0 Mux

S

A1 2 vers 1 A

D C B A D C B

>>> 5/6 <<<

Annexes

Annexe A : Comparateur 4 bits (7485) :

Le schéma de principe du comparateur la table de vérité du comparateur 4 bits (7485) :

VCC

16

10 A0

12 A1

13 A2 7485

15 A3

Entrées de mise

en cascade

2 A>B A>B 5

Sorties

3 A=B A=B 6

4 A<B A<B 7

9 B0

11

B1

14

B2

1

B3

Annexe B : Décodeur 1 parmi 8 (74138) :

B.1 Le schéma de principe du décodeur 1 parmi 8 (74138) :

O0

A A0 O1

B A1 O2

6 entrées

8 sorties

C A2 Décodeur

74138 O3

O4

E1 1 parmi 8

E2 O5

D E3 O6

O7

B.2 La table de vérité du décodeur 1 parmi 8 (74138) :

>>> 6/6 <<<

Vous aimerez peut-être aussi

- Exercice Sur Le Transcodeur GRAY-binaire-corrigeDocument1 pageExercice Sur Le Transcodeur GRAY-binaire-corrigeChichi HachemiPas encore d'évaluation

- Rapport Electronique NumeriqueDocument4 pagesRapport Electronique NumeriqueBIENVENU KANGNI100% (1)

- Add SOUSDocument9 pagesAdd SOUSNabil KhPas encore d'évaluation

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaPas encore d'évaluation

- Abdou. Initiation API Millenium 3Document21 pagesAbdou. Initiation API Millenium 3sethabdellahPas encore d'évaluation

- Chapitre V - Mise en Oeuvre Des Automatismes Sur APIDocument10 pagesChapitre V - Mise en Oeuvre Des Automatismes Sur APIdallagi mohamedPas encore d'évaluation

- TD Porte NANDDocument2 pagesTD Porte NANDUnPLatDeSpaghettisPas encore d'évaluation

- Serie Exo AutomatismesDocument8 pagesSerie Exo AutomatismesSalimMalekPas encore d'évaluation

- DSC2 2ste 2019 2020Document8 pagesDSC2 2ste 2019 2020ismail elmoufakirPas encore d'évaluation

- Mikro CDocument23 pagesMikro COUSKRIPas encore d'évaluation

- Dsc1 2ste Atc 2014 2015 ÉolienneDocument6 pagesDsc1 2ste Atc 2014 2015 Éolienneismail elmoufakirPas encore d'évaluation

- 2015 2016 Graphe TD6 OptimationDocument5 pages2015 2016 Graphe TD6 OptimationSa LimPas encore d'évaluation

- LesmemoiresDocument44 pagesLesmemoiresouissemPas encore d'évaluation

- ch4 CircuitscombinatoiresDocument8 pagesch4 CircuitscombinatoiresKais BouzraraPas encore d'évaluation

- Préparation Du TP 4Document4 pagesPréparation Du TP 4BENYOUSSEF ANISPas encore d'évaluation

- Chapiiiiiiitre 3Document7 pagesChapiiiiiiitre 3haknmPas encore d'évaluation

- Polycopie TPs Circuits & Signaux GE1 ESTADocument21 pagesPolycopie TPs Circuits & Signaux GE1 ESTASimo FidoudiPas encore d'évaluation

- Geii 1a Logique TP 2Document11 pagesGeii 1a Logique TP 2Thibaud BouzyPas encore d'évaluation

- TD CodeurDocument4 pagesTD CodeurMüheb BoudhraaPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique Système de Triage Automatique - 3ème Technique (2011-2012) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Génie Électrique Système de Triage Automatique - 3ème Technique (2011-2012) MR Abdallah Raouafiibrahim abdelaliPas encore d'évaluation

- Exam-Microprocesseur 8086-2020-2021-11 Fevrier 2021Document3 pagesExam-Microprocesseur 8086-2020-2021-11 Fevrier 2021oussama sahliPas encore d'évaluation

- 1-AOP Cours2007-3iemeDocument5 pages1-AOP Cours2007-3iemeAhmed BelhadjPas encore d'évaluation

- Ratt Corrig Type 24 06 2017Document8 pagesRatt Corrig Type 24 06 2017عرعار يوسفPas encore d'évaluation

- TP Sur Le Multivibrateur AstableDocument10 pagesTP Sur Le Multivibrateur AstableShehabPas encore d'évaluation

- Séquentiel - ENSA - Synthese Asynchrone HuffmanDocument40 pagesSéquentiel - ENSA - Synthese Asynchrone HuffmanAicha LahnoukiPas encore d'évaluation

- 2 Prog AssembleurDocument5 pages2 Prog AssembleurAnonymous Cr8uWCWxu100% (1)

- TD Prepa Ana 2elt2Document2 pagesTD Prepa Ana 2elt2Phenix PhenixPas encore d'évaluation

- Dossier CorrigeDocument29 pagesDossier CorrigeMohammed Amine ChafikiPas encore d'évaluation

- Automatismes Et Nformatique Industrielle L2: S3/ S4 L3: S5/ S6Document42 pagesAutomatismes Et Nformatique Industrielle L2: S3/ S4 L3: S5/ S6Lotfi AbidiPas encore d'évaluation

- TP 1 RegistreDocument4 pagesTP 1 Registrellahn64Pas encore d'évaluation

- Iugetchapitre 1 PDFDocument10 pagesIugetchapitre 1 PDFFabrice FotsoPas encore d'évaluation

- Logique Combinatoire PDFDocument7 pagesLogique Combinatoire PDFAmatou ArrahmenPas encore d'évaluation

- ComparateurDocument4 pagesComparateurخالد محمد السقنيPas encore d'évaluation

- Cours Lycée Pilote - Technologie Fonctions Logiques Universelles - 2ème Sciences (2014-2015) MR Rafik Ben Amor PDFDocument7 pagesCours Lycée Pilote - Technologie Fonctions Logiques Universelles - 2ème Sciences (2014-2015) MR Rafik Ben Amor PDFchida OussamaPas encore d'évaluation

- Épreuve de Synthèse D'automatique 2002-2003Document7 pagesÉpreuve de Synthèse D'automatique 2002-2003Nourallah AouinaPas encore d'évaluation

- TDChapitre 3Document3 pagesTDChapitre 3Karim Naidja100% (1)

- Technique Rapports Realisation D Un Robot Teleguide Par InfrarougeDocument18 pagesTechnique Rapports Realisation D Un Robot Teleguide Par InfrarougeThe geek Cuesta100% (1)

- Rapport Tap Univ BBA Partie 1Document25 pagesRapport Tap Univ BBA Partie 1Emy ImenePas encore d'évaluation

- TD3-EN-Elements de Reponse, Seance 9 (Ex3+Ex4), Amari AzizDocument3 pagesTD3-EN-Elements de Reponse, Seance 9 (Ex3+Ex4), Amari AzizMahdi Lahdili100% (1)

- ECE 2004-Corrige PDFDocument6 pagesECE 2004-Corrige PDFbaydiPas encore d'évaluation

- Rapport de 1er StageDocument23 pagesRapport de 1er Stageabderrahim meksiPas encore d'évaluation

- Lecon3-0 Fonction UniverselleDocument4 pagesLecon3-0 Fonction Universellefehmi001Pas encore d'évaluation

- Corrigé Du TD2: N-1barDocument3 pagesCorrigé Du TD2: N-1barELMEHDI CHOUINEPas encore d'évaluation

- TP 4Document12 pagesTP 4boufakri abdelmounaimPas encore d'évaluation

- Using ADC of PIC MicrocontrollerDocument7 pagesUsing ADC of PIC MicrocontrollernawzatPas encore d'évaluation

- Cours Labview 09Document66 pagesCours Labview 09hassenbb100% (1)

- Ci13 TD 3 Can eDocument3 pagesCi13 TD 3 Can eCapteurs InstrumentationPas encore d'évaluation

- Le RedressementDocument22 pagesLe Redressementanes bendjemaiPas encore d'évaluation

- Chapitre 4 SLDocument12 pagesChapitre 4 SLHENSCHEL ShadracPas encore d'évaluation

- SaadDocument12 pagesSaadBoukdir Saad Din0% (1)

- Exercices Gracets CoordonnesDocument5 pagesExercices Gracets CoordonnessaulnierPas encore d'évaluation

- 02-De La Porte Logique Au Chemin de DonnéesDocument14 pages02-De La Porte Logique Au Chemin de DonnéesfaouziiiPas encore d'évaluation

- TD Avec 1corrigé - Nov-2020 - Application Du Théorème de NortonDocument5 pagesTD Avec 1corrigé - Nov-2020 - Application Du Théorème de NortonRaja BenabdallahPas encore d'évaluation

- Les Bascules Bistables CorrectionDocument9 pagesLes Bascules Bistables CorrectionTopina RahimPas encore d'évaluation

- CR AytomgneDocument13 pagesCR AytomgneMhB SaAdPas encore d'évaluation

- Epreuve Micro 2Document9 pagesEpreuve Micro 2Takam TchudzoPas encore d'évaluation

- Série #1-1ère Partie - Logique CombinatoireDocument12 pagesSérie #1-1ère Partie - Logique CombinatoireNejib JallouliPas encore d'évaluation

- Lecon A2-3 - Circuits CombinatoiresDocument7 pagesLecon A2-3 - Circuits CombinatoiresAhmed BelhadjPas encore d'évaluation

- DC1 4T Dpe 17 CorrectionDocument4 pagesDC1 4T Dpe 17 Correctiontakecoin767Pas encore d'évaluation