Académique Documents

Professionnel Documents

Culture Documents

Examen AO 2021 2022

Transféré par

ghostninja745Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Examen AO 2021 2022

Transféré par

ghostninja745Droits d'auteur :

Formats disponibles

EXAMEN FINAL

Département TI Date 14/01/22

Matière ARCHITECTURE DES ORDINATEURS Durée 01h30

Enseignantes R.BELLAZREG, A.GHACHEM, I. KAROUIA & A.TRIKI Doc. Autorisés NON

Calculat. Autorisée NON

Classes TI 101, 102, 103, 104, 105, 106, 107, 108 Nombre de pages 8+annexe

Nom :………………………………… Prénom : ……………………….……

CIN :……………………………………….……… Classe : TI……

Matière : ARCHITECTURE DES ORDINATEURS

Classes : TI 101, 102, 103, 104, 105, 106, 107, 108

Date : 14/01/2022

Exercice 1 3.5 Pts

Encerclez la ou les bonnes réponses

1. Afin d’améliorer les performances d’un micro-processeur, on peut :

a. Augmenter nombre des bus internes et le nombre de registres.

b. Diminuer la vitesse des microprocesseurs en augmentant leur fréquence.

c. Paralléliser l’exécution des instructions.

d. bénéficier d’un parallélisme au niveau des processeurs.

2. Lors d’une exécution en mode pipeline, si une instruction de branchement est exécutée

en modifiant le compteur ordinal, on appelle ce type de problème :

a. Aléa structurel

b. Aléa de contrôle

c. Aléa de données

3. Un processeur doté d’une architecture CISC :

a. Admet un format d’instruction variable.

b. A un compilateur simple.

c. Admet des instructions complexes prenant plusieurs cycles machines.

d. Utilise peu de modes d’adressage.

4. Lors du cycle d’exécution d’une instruction, le compteur ordinal se positionne sur

l’adresse de la prochaine instruction à exécuter :

a. A la fin de la recherche d’instruction.

b. A la fin du décodage de l’instruction.

c. A la fin de l’exécution de l’instruction.

d. Avant l’exécution de l’instruction.

5. Le pipelining consiste à :

a. Segmenter une opération en séquentiel.

b. Segmenter une opération en une séquence d’actions plus simples.

c. Segmenter une opération en une séquence d’actions plus complexes.

A.U. 2021/2022 – Sem. 1 Page 1/8

6. Dans les architectures multi-cœurs actuelles, comment sont les mémoires cache niveau

1 (L1) et niveau 3 (L3) :

a. L1 est partagée et L3 est dédiée

b. L1 est dédiée et L3 est partagée

c. L1 est dédiée et L3 est dédiée

d. L1 est partagée et L3 est partagée

7. Soit un processeur de fréquence 2.6 GHz où, en moyenne, l’exécution des instructions

nécessite 20 cycles machine. Quelle est la puissance de ce microprocesseur ?

a. 520

b. 0.13

c. 52

d. 130

e. 7.69

8. Dans un mode d’exécution en pipeline :

a. Le débit d’exécution des instructions est réduit.

b. Le temps d’exécution d’une instruction n’est pas réduit

c. Le débit d’exécution des instructions est considérablement augmenté.

d. Le temps d’exécution d’une instruction est réduit.

A.U. 2021/2022 – Sem. 1 Page 2/8

Exercice 2 5.5 Pts

Partie 1 :

On considère une machine composée d’un processeur ayant un seul coeur. Chaque instruction est

décomposée en sept (07) étapes. Chaque étape occupe un seul cycle machine.

En justifiant votre réponse.

1) Quel est la durée d’exécution (nombre de cycles machine) de 3 instructions en exécution séquentielle ?

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

2) Si cette machine fonctionne en mode pipeline, quel est le nombre d’étages de ce pipeline?

……..………………………………………………………………………………..…………...............

3) Représenter l’exécution de 3 instructions en mode pipeline (Vous pouvez noter les étages du pipeline

avec des lettres de l’alphabet : A, B, C, …)

4) Calculer le gain en performance pour l’exécution de 3 instructions

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

A.U. 2021/2022 – Sem. 1 Page 3/8

Partie 2 :

Pour améliorer les performances de la machine, nous avons remplacé le microprocesseur par un

microprocesseur Dual core.

1) Quelle est la durée d’exécution de 14 instructions indépendantes les unes des autres en mode pipeline

de 6 étages ?

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

2) Quel est le gain de performance de la machine Dual Core pour l’exécution de ces 14 instructions

telles que décrites en pipeline par rapport à leur exécution en séquentiel

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

On suppose, maintenant, que les 14 instructions sont liées les unes aux autres de sorte que chaque

instruction ne peut s’exécuter qu’une fois celle d’avant terminée.

3) Est-ce que le temps d’exécution d’une machine Dual Core serait pareil ? Expliquer.

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

……..………………………………………………………………………………..…………...............

Problème 11 Pts

Soit une machine dotée de :

un microprocesseur ayant des instructions de taille et de format fixes :

- L’annexe présente les registres, des modes d’adressage, le format et le jeu d’instructions

- Le tableau 1 présente le contenu des différents registres avant l’exécution des différentes

instructions

une mémoire adressable par mot où chaque mot mémoire occupe 1 octet

- La figure 1 représente le contenu de la mémoire qui contient un bloc d’instructions et un

bloc de données

- On considère que chaque donnée occupe 2 mots mémoire

A.U. 2021/2022 – Sem. 1 Page 4/8

EXAMEN FINAL

Département TI Date 14/01/22

Matière ARCHITECTURE DES ORDINATEURS Durée 01h30

Enseignantes R.BELLAZREG, A.GHACHEM, I. KAROUIA & A.TRIKI Doc. Autorisés NON

Calculat. Autorisée NON

Classes TI 101, 102, 103, 104, 105, 106, 107, 108 Nombre de pages 8+annexe

Nom :………………………………… Prénom : ……………………….……

CIN :……………………………………….……… Classe : TI……

Matière : ARCHITECTURE DES ORDINATEURS

Suite du problème

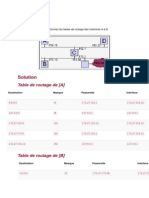

Adresse Tableau 1: Contenu des différents registres

mémoire en

Instructions

hexadécimal ... Registre Contenu

B3CA0 0000 1100 I1 KK 1010 0000 0000 0000 0000 0000 0000 1010

B3CA1 0000 0000 LL 0000 1100 0000 0000 0001 0011 0111 1111

B3CA2 1111 0000

NN 1000 0000 0000 0000 0000 0000 0000 1111

B3CA3 1100 1111

B3CA4 .... I2 SS 1111 0000 0000 0000 1010 1110 0101 0101

B3CA5 .... ZZ 1100 0000 1001 0000 1010 1111 0000 0000

0001 0010 I3

0000 1010

0110 1100

1101 1100

... Données

C0A11 0000 0011

C0A12 0000 0010

C0A13 0000 0000

...

Figure 1: Contenu de la mémoire

Travail demandé :

Toutes les réponses doivent être justifiées

Partie 1 : (4.5 points)

On suppose que le microprocesseur est en train de décoder l’instruction I1 suivante située à l’adresse

B3CA0 :

1100 1111 1111 0000 0000 0000 0000 1100

A.U. 2021/2022 – Sem. 1 Page 5/8

1) Quelle est la taille de l’instruction ?

………………………………………………………………………………………………………....

2) Sur combien de mots mémoire s’écrit une instruction ?

………………………………………………………………………………………………………....

3) Quelle est la taille du code instruction ?

………………………………………………………………………………………………………....

4) Quelle est la taille du code opérande ?

………………………………………………………………………………………………………....

5) Par combien d’instructions est formé le jeu d’instructions au maximum ?

………………………………………………………………………………………………………....

6) De quelle opération il s’agit (donner la mnémonique correspondante) ?

……..………………………………………………………………………………..……………….....

7) Quel est le mode d’adressage de l’instruction I1 ?

……..………………………………………………………………………………..……………….....

8) Donner l’équivalent de l’instruction I1 en langage assembleur du microprocesseur tel que défini

……..………………………………………………………………………………..……………….....

9) Quel est le contenu du registre d’instruction ?

……..………………………………………………………………………………..……………….....

10) Quel est le contenu du registre d’adresse en hexadécimal ?

……..………………………………………………………………………………..……………….....

11) Quel est le contenu du compteur ordinal en hexadécimal ?

……..………………………………………………………………………………..……………….....

12) Quel est le contenu de l’accumulateur, à cette étape, en binaire ?

………………………………………………………………………………………………………....

A.U. 2021/2022 – Sem. 1 Page 6/8

Partie 2 : (2 points)

On considère que l’instruction I1 a été exécutée et que le microprocesseur est, maintenant, dans la phase

d’exécution de l’instruction I2 située à l’adresse B3CA4. L’instruction peut être décrite en ass0embleur

comme suit :

INF KK, LL

1) Quel est le mode d’adressage de l’instruction I2 ?

……..………………………………………………………………………………..……………….....

2) Donner l’équivalent binaire de l’instruction I2

……..………………………………………………………………………………..……………….....

3) Quel est le contenu du registre d’instruction ?

……..………………………………………………………………………………..……………….....

4) Quel est le contenu du Compteur Ordinal ? Justifier

……..………………………………………………………………………………..……………….....

……..………………………………………………………………………………..……………….....

Partie 3 : (2.5 points)

Nous sommes actuellement à la phase de recherche de l’instruction I3 placée à l’adresse B3CA8 dont le

code est:

1101 1100 0110 1100 0000 1010 0001 0010

1) Donner l’équivalent de l’instruction I3 en langage assembleur du microprocesseur tel que défini

……………………………………………………………………………………………………….....

2) Quel est le contenu du registre d’adresse en hexadécimal ?

……………………………………………………………………………………………………….....

3) Quel est le contenu du compteur ordinal en hexadécimal ?

……………………………………………………………………………………………………….....

4) Quel est le contenu de l’accumulateur en binaire ?

………………………………………………………………………………………………………....

A.U. 2021/2022 – Sem. 1 Page 7/8

Partie 4 : (2 points)

On suppose que l’exécution de l’instruction I3 est terminée.

Quel est le contenu des différents registres tenant compte de l’exécution successive des instructions I1,

I2 et I3 ?

KK= …………………………………………………………………………………………………...

LL =…………………………………………...………………………………...……………………...

NN =…………………………………………….………………………...…………………………...

SS =…………………………………………………………………………………………...………...

ZZ = …………………………………………………………………………………………………...

Bon TRAVAIL !

../..

A.U. 2021/2022 – Sem. 1 Page 8/8

Vous aimerez peut-être aussi

- Cours de Bases de Données: SGBD Relationnels Aspects Système - ExercicesDocument29 pagesCours de Bases de Données: SGBD Relationnels Aspects Système - Exercicesromuald LanePas encore d'évaluation

- L' Injection électronique: Tutoriel et GuideD'EverandL' Injection électronique: Tutoriel et GuideÉvaluation : 5 sur 5 étoiles5/5 (1)

- Correction Examen AO 2021 2022Document4 pagesCorrection Examen AO 2021 2022ghostninja745Pas encore d'évaluation

- TDs ArchitectureDocument5 pagesTDs Architectureben houria yassine100% (1)

- Traité d'économétrie financière: Modélisation financièreD'EverandTraité d'économétrie financière: Modélisation financièrePas encore d'évaluation

- Examen Archi 2017 - 2018Document3 pagesExamen Archi 2017 - 2018Anas MaghrebiPas encore d'évaluation

- Le développement de systèmes d'information (Le): Une méthode intégrée à la transformation des processus, 4e éditionD'EverandLe développement de systèmes d'information (Le): Une méthode intégrée à la transformation des processus, 4e éditionPas encore d'évaluation

- Exam 2020Document7 pagesExam 2020Mamadou Korka KantéPas encore d'évaluation

- Corrigé Série de TD N° 3Document5 pagesCorrigé Série de TD N° 3Alaa MessaoudPas encore d'évaluation

- Grain 5Document5 pagesGrain 5Elo TarikPas encore d'évaluation

- Travaux Dirigés-Microprocesseur MicrocontroleurDocument18 pagesTravaux Dirigés-Microprocesseur MicrocontroleurFatima BettayebPas encore d'évaluation

- Architecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Document204 pagesArchitecture Et Maintenance Des Ordinateurs Sc3a9curisc3a9Kam ZegPas encore d'évaluation

- Cours Systemes A MicroprocesseursDocument134 pagesCours Systemes A MicroprocesseursKam ZegPas encore d'évaluation

- Cours UnixDocument22 pagesCours UnixHarouna CoulibalyPas encore d'évaluation

- Examen Session 1 - 2022Document7 pagesExamen Session 1 - 2022Mamadou Korka KantéPas encore d'évaluation

- Série de TD N° 3: Nommez Les Composants D'ordinateur SuivantsDocument4 pagesSérie de TD N° 3: Nommez Les Composants D'ordinateur SuivantsAlaa MessaoudPas encore d'évaluation

- Circuit LP EPACDocument38 pagesCircuit LP EPACSouk Malinga100% (1)

- Examen Switched Networks S2-CorrectionDocument7 pagesExamen Switched Networks S2-CorrectionRania khadraoui100% (1)

- DS19 20Document7 pagesDS19 20baklouti lindaPas encore d'évaluation

- Cours Programmation en Assembleur C6713Document22 pagesCours Programmation en Assembleur C6713Ikram Serhane100% (1)

- Efm Tmsir IteDocument2 pagesEfm Tmsir IteAmina Benjelouaja100% (1)

- Poly ArchiDocument107 pagesPoly ArchiFadwa Zed100% (1)

- Poly - Micro 2023 2024Document56 pagesPoly - Micro 2023 2024kaoutar saadaouiPas encore d'évaluation

- TP1Document4 pagesTP1Cesar MalkiPas encore d'évaluation

- DS2016Document6 pagesDS2016Heythem DhaouadiPas encore d'évaluation

- Examen1+Solution Architecture Des OrdinateursDocument7 pagesExamen1+Solution Architecture Des Ordinateursihadjkaddour7Pas encore d'évaluation

- TP ProjetDocument25 pagesTP ProjetMayna LamemPas encore d'évaluation

- Examen L3 SI, S51 Architecture III Session 2: Exercice 1: (5 Points)Document33 pagesExamen L3 SI, S51 Architecture III Session 2: Exercice 1: (5 Points)Sira NdiayePas encore d'évaluation

- TD Serie N2-2022Document4 pagesTD Serie N2-2022yoannaffantodji750Pas encore d'évaluation

- TP Eln1 POLY 2011 08 29 PDFDocument10 pagesTP Eln1 POLY 2011 08 29 PDFDaoud MarhoumePas encore d'évaluation

- Buisson Concevoir Son Microprocesseur - Structure Des Systèmes Logiques (Ellipses)Document251 pagesBuisson Concevoir Son Microprocesseur - Structure Des Systèmes Logiques (Ellipses)alalim060% (1)

- Cours 10 IntallerDocument5 pagesCours 10 Intallerهداية مسلمةPas encore d'évaluation

- Exercices Aaog TH1Document5 pagesExercices Aaog TH1abdeelhamideelkourchiePas encore d'évaluation

- DS STMDocument5 pagesDS STMMeryemHmouriPas encore d'évaluation

- Série2 2021Document2 pagesSérie2 2021CAMPUS TIZI OUZOUPas encore d'évaluation

- ExamanDocument5 pagesExamanbrahmi ademPas encore d'évaluation

- Noyau FasciculeDocument90 pagesNoyau FasciculemickadoPas encore d'évaluation

- DownloadfileDocument4 pagesDownloadfiletagnePas encore d'évaluation

- Examen Logique 2022 PrincipalDocument4 pagesExamen Logique 2022 PrincipalaliPas encore d'évaluation

- Support Microprocesseurs PDFDocument64 pagesSupport Microprocesseurs PDFRidhaNommanePas encore d'évaluation

- AssembleurDocument44 pagesAssembleurGoku SonPas encore d'évaluation

- SN - Architecture - 2063 CorDocument3 pagesSN - Architecture - 2063 CorMarc AzemkouPas encore d'évaluation

- Examen Systemes Logiques: DC BADocument4 pagesExamen Systemes Logiques: DC BAakremfPas encore d'évaluation

- Cours - Microprocesseurs Et Microcontroleurs - Internet PDFDocument105 pagesCours - Microprocesseurs Et Microcontroleurs - Internet PDFsoukaina100% (4)

- ALMODocument91 pagesALMObeckytom75100% (1)

- Examen DBA 2018 Licence RABATDocument3 pagesExamen DBA 2018 Licence RABATsaidaPas encore d'évaluation

- Syllabus TpsDocument28 pagesSyllabus Tpsbjbjl3adimPas encore d'évaluation

- TD N°2: Fonctionnement D'un Pipeline: Exercice 1: Opérations ArithmétiquesDocument3 pagesTD N°2: Fonctionnement D'un Pipeline: Exercice 1: Opérations ArithmétiquesMouad JaouhariPas encore d'évaluation

- Devoir LFSJG11 2024Document3 pagesDevoir LFSJG11 2024Faïza TabbanaPas encore d'évaluation

- Examen IIT Archi Des Ordi Principale2020Document4 pagesExamen IIT Archi Des Ordi Principale2020slim yaichPas encore d'évaluation

- Exécution de Processus en MultiprogrammationDocument10 pagesExécution de Processus en Multiprogrammationyahia ilyesPas encore d'évaluation

- 18.6 NTIC TMSIR Ex Passage Synthèse V2Document8 pages18.6 NTIC TMSIR Ex Passage Synthèse V2khalid maarifaPas encore d'évaluation

- Cahier D ExercicesDocument25 pagesCahier D Exercicesmlbb fannyPas encore d'évaluation

- Cahier D ExercicesDocument25 pagesCahier D ExercicesMehdi BenhimaPas encore d'évaluation

- Sujet Architecture Des Ordinateurs Et Systeme D'exploitationDocument3 pagesSujet Architecture Des Ordinateurs Et Systeme D'exploitationAye ScottPas encore d'évaluation

- Odulation DE Argeur D' Mpulsion: Rojet 1999Document79 pagesOdulation DE Argeur D' Mpulsion: Rojet 1999Youcef Diaf100% (2)

- Devoir Microcontrôleurs 2012-2013Document5 pagesDevoir Microcontrôleurs 2012-2013Énō ŁāPas encore d'évaluation

- Devoir de Synthese N3 - Technologie - 2eme Sciences (2007-2008) Mme Toumi Imen-Systeme de Chargement de Sable de MoulageDocument6 pagesDevoir de Synthese N3 - Technologie - 2eme Sciences (2007-2008) Mme Toumi Imen-Systeme de Chargement de Sable de MoulageKamel Tayahi100% (1)

- Export DeclarationDocument3 pagesExport DeclarationKhadija AbbasPas encore d'évaluation

- Toyota Corolla VersoDocument38 pagesToyota Corolla Versokains5467% (3)

- GuideTechnique LCPC SUIVIDIMDocument64 pagesGuideTechnique LCPC SUIVIDIMIroukoura AlexPas encore d'évaluation

- Conception Et Realisation D Un Prototype PDFDocument126 pagesConception Et Realisation D Un Prototype PDFChouichi Ghada100% (1)

- Routage 1Document24 pagesRoutage 1Hamid El BouabidiPas encore d'évaluation

- TP 04 Planification de Réseau 2G-GSM Et DCS 1800Document25 pagesTP 04 Planification de Réseau 2G-GSM Et DCS 1800BOUZANA ElaminePas encore d'évaluation

- Att 1436900235833 Att 1436897005248 Information Rotary Club InternationalDocument7 pagesAtt 1436900235833 Att 1436897005248 Information Rotary Club InternationalAkimBiPas encore d'évaluation

- 10-Notice Concours - G2E - Notice-Dinscription-2022Document16 pages10-Notice Concours - G2E - Notice-Dinscription-2022BAÏ NGUIRA-APas encore d'évaluation

- Ait Boulahcen Hamza RademDocument1 pageAit Boulahcen Hamza RademAIT BOULAHCENPas encore d'évaluation

- FR Acs800-01 HW K A4 ScreenDocument176 pagesFR Acs800-01 HW K A4 ScreenBounaji LotfallahPas encore d'évaluation

- Architécture Dun SmartphoneDocument15 pagesArchitécture Dun SmartphoneKirk Ben Hammet100% (1)

- MarketingDocument5 pagesMarketingNejla AnanePas encore d'évaluation

- Projet Linux-1Document7 pagesProjet Linux-1Lamine DiengPas encore d'évaluation

- Article Technologie Et EnseignementDocument2 pagesArticle Technologie Et EnseignementJulia ClaptonPas encore d'évaluation

- BAC 2022 - Spé SES - JOUR 1Document14 pagesBAC 2022 - Spé SES - JOUR 1LETUDIANT67% (3)

- Langage SQL LCDDocument121 pagesLangage SQL LCDOmar Berraho100% (1)

- TP9 SambaDocument2 pagesTP9 SambakassimiPas encore d'évaluation

- Regulation l634cDocument56 pagesRegulation l634cCheval AlainPas encore d'évaluation

- SIGMA SD900 - French - Manuel de L'utilisateur PDFDocument90 pagesSIGMA SD900 - French - Manuel de L'utilisateur PDFfakhourimia souPas encore d'évaluation

- Amn 20220915161851.pdfamnDocument2 pagesAmn 20220915161851.pdfamnflorian delebecquePas encore d'évaluation

- La Process ComDocument27 pagesLa Process ComTREVOR100% (2)

- CV ProfDocument1 pageCV Profforever273Pas encore d'évaluation

- Dba SRDocument5 pagesDba SRGhofrane FerchichiPas encore d'évaluation

- Plan Etude GCR 2022-2023Document5 pagesPlan Etude GCR 2022-2023Siri ?Pas encore d'évaluation

- OuiiiDocument1 pageOuiiiOussama MonirPas encore d'évaluation

- Manuel GoPro HERO 6Document53 pagesManuel GoPro HERO 6Arnaud BlanchardPas encore d'évaluation

- 4 - Gestion Des DisquesDocument34 pages4 - Gestion Des DisquesMohamed AnnaniPas encore d'évaluation

- Correction Partie2 TP3 (Lien Physique Et Lien Symbolique)Document3 pagesCorrection Partie2 TP3 (Lien Physique Et Lien Symbolique)Rahma Ben YounesPas encore d'évaluation

- AQ, Assurance Qualité, CQ, Vérifier Et Valider DonnéesDocument3 pagesAQ, Assurance Qualité, CQ, Vérifier Et Valider DonnéeslecouveyPas encore d'évaluation

- Les Fonctions de L'entreprise Rappel. Les Systemes D'information Et Les PGIDocument10 pagesLes Fonctions de L'entreprise Rappel. Les Systemes D'information Et Les PGIKidrissi Karim,idrissiPas encore d'évaluation

- Secrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)D'EverandSecrets du Marketing des Médias Sociaux 2021: Conseils et Stratégies Extrêmement Efficaces votre Facebook (Stimulez votre Engagement et Gagnez des Clients Fidèles)Évaluation : 4 sur 5 étoiles4/5 (2)

- Wireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.D'EverandWireshark pour les débutants : Le guide ultime du débutant pour apprendre les bases de l’analyse réseau avec Wireshark.Pas encore d'évaluation

- Technologie automobile: Les Grands Articles d'UniversalisD'EverandTechnologie automobile: Les Grands Articles d'UniversalisPas encore d'évaluation

- Dark Python : Apprenez à créer vos outils de hacking.D'EverandDark Python : Apprenez à créer vos outils de hacking.Évaluation : 3 sur 5 étoiles3/5 (1)

- Wi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserD'EverandWi-Fi Hacking avec kali linux Guide étape par étape : apprenez à pénétrer les réseaux Wifi et les meilleures stratégies pour les sécuriserPas encore d'évaluation

- Python | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationD'EverandPython | Programmer pas à pas: Le guide du débutant pour une initiation simple & rapide à la programmationPas encore d'évaluation

- Comment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.D'EverandComment analyser les gens : Introduction à l’analyse du langage corporel et les types de personnalité.Pas encore d'évaluation

- Piraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéD'EverandPiraté: Guide Ultime De Kali Linux Et De Piratage Sans Fil Avec Des Outils De Test De SécuritéPas encore d'évaluation

- Apprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationD'EverandApprendre Python rapidement: Le guide du débutant pour apprendre tout ce que vous devez savoir sur Python, même si vous êtes nouveau dans la programmationPas encore d'évaluation

- Le trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsD'EverandLe trading en ligne facile à apprendre: Comment devenir un trader en ligne et apprendre à investir avec succèsÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Hacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxD'EverandHacking pour débutants : Le guide complet du débutant pour apprendre les bases du hacking avec Kali LinuxÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- L'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésD'EverandL'analyse fondamentale facile à apprendre: Le guide d'introduction aux techniques et stratégies d'analyse fondamentale pour anticiper les événements qui font bouger les marchésÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- L'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.D'EverandL'analyse technique facile à apprendre: Comment construire et interpréter des graphiques d'analyse technique pour améliorer votre activité de trading en ligne.Évaluation : 3.5 sur 5 étoiles3.5/5 (6)

- La communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseD'EverandLa communication professionnelle facile à apprendre: Le guide pratique de la communication professionnelle et des meilleures stratégies de communication d'entrepriseÉvaluation : 5 sur 5 étoiles5/5 (1)

- Le marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentD'EverandLe marketing d'affiliation en 4 étapes: Comment gagner de l'argent avec des affiliés en créant des systèmes commerciaux qui fonctionnentPas encore d'évaluation

- Conception & Modélisation CAO: Le guide ultime du débutantD'EverandConception & Modélisation CAO: Le guide ultime du débutantPas encore d'évaluation

- WiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxD'EverandWiFi Hacking : Le guide simplifié du débutant pour apprendre le hacking des réseaux WiFi avec Kali LinuxÉvaluation : 3 sur 5 étoiles3/5 (1)

- Le Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsD'EverandLe Bon Accord avec le Bon Fournisseur: Comment Mobiliser Toute la Puissance de vos Partenaires Commerciaux pour Réaliser vos ObjectifsÉvaluation : 4 sur 5 étoiles4/5 (2)

- Hacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersD'EverandHacking pour débutant Le guide ultime du débutant pour apprendre les bases du hacking avec Kali Linux et comment se protéger des hackersPas encore d'évaluation

- Explication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumD'EverandExplication De La Technologie Blockchain: Guide Ultime Du Débutant Au Sujet Du Portefeuille Blockchain, Mines, Bitcoin, Ripple, EthereumPas encore d'évaluation

- NFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueD'EverandNFT et Cryptoart: Le guide complet pour investir, créer et vendre avec succès des jetons non fongibles sur le marché de l'art numériqueÉvaluation : 5 sur 5 étoiles5/5 (5)

- La psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsD'EverandLa psychologie du travail facile à apprendre: Le guide d'introduction à l'utilisation des connaissances psychologiques dans le domaine du travail et des organisationsPas encore d'évaluation

- Guide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxD'EverandGuide Pour Les Débutants En Matière De Piratage Informatique: Comment Pirater Un Réseau Sans Fil, Sécurité De Base Et Test De Pénétration, Kali LinuxÉvaluation : 1 sur 5 étoiles1/5 (1)

- Gestion de projet : outils pour la vie quotidienneD'EverandGestion de projet : outils pour la vie quotidienneÉvaluation : 5 sur 5 étoiles5/5 (2)

- Création d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileD'EverandCréation d'une start-up à succès de A à Z: Réussir votre Start-up 2.0 Web et MobileÉvaluation : 3.5 sur 5 étoiles3.5/5 (4)

- Le trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsD'EverandLe trading des bandes de bollinger facile à apprendre: Comment apprendre à utiliser les bandes de bollinger pour faire du commerce en ligne avec succèsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Créer Son Propre Site Internet Et Son Blog GratuitementD'EverandCréer Son Propre Site Internet Et Son Blog GratuitementÉvaluation : 5 sur 5 étoiles5/5 (1)