Académique Documents

Professionnel Documents

Culture Documents

Compte Rendu VHDL

Compte Rendu VHDL

Transféré par

eyabouraoui0Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Compte Rendu VHDL

Compte Rendu VHDL

Transféré par

eyabouraoui0Droits d'auteur :

Formats disponibles

Ecole Supérieur des Sciences et de la Technologie

De Hammam Sousse

Compte Rendu : Tp1 Description VHDL et Simulation

Classe 2émé année Système Embarqué

Travail élaboré par : Seif khemiri

Eya Bouraoi

Maymoun Jabnouni

Lundi 12 février 2024 Page 1

Objectifs du TP

Prise en main de l’outil ModelSim : Création d’un projet , Compilation et

Simulation d’une description VHDL .

Utiliser un banc de test pour générer les stimuli .

Organisation d’un projet en différents fichiers pour la simulation (

séparation du design et du Test-bench).

Initiation à la description hiérarchique en VHDL (utilisation des

ccomposants).

Manipulation d’une description structurelle d’un opérateur arithmétique

d’addition et utilisation des instructions en flot de données pour les

opérateurs logiques.

Travail demandé :

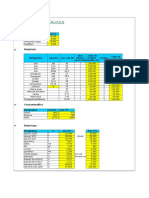

1. Demi-additionneur :

Table de verité :

A B C S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Shéma électronique en portes logique du circuit :

Lundi 12 février 2024 Page 2

Création d’un projet sous ModelSim pour la simulation du demi_additionneur :

Lundi 12 février 2024 Page 3

2. Additionneur complet 1 bit :

3. Multiplexeur 4 vers 1 :

Rappeler les équations de S en fonction de Cmd,A,B ,C et D :

S<=a and not(s1) and not(s0)) or(b and (s1) and not (s0)) or(c and

(s1) and not (s0))or(d and (s1) and (s0))

Déscription en VHDL d’un Multiplexeur avec 2 architecture :

o Comportementale :

Lundi 12 février 2024 Page 4

Lundi 12 février 2024 Page 5

o Float de données :

Lundi 12 février 2024 Page 6

4. Démultiplexeur 1 vers 4 :

Rappeler les équations de A,B,Cet D en fonction de Cmd :

Déscription en vhdl :

Lundi 12 février 2024 Page 7

Déscription VHDL structuelle le circuit présenté par la figure ci_dessous:

Lundi 12 février 2024 Page 8

Vous aimerez peut-être aussi

- ISO 45001 Version 2018Document58 pagesISO 45001 Version 2018foorter fifi100% (4)

- conformidadMTKD S1Document2 pagesconformidadMTKD S1Jair VillaverdePas encore d'évaluation

- Seance - IDocument37 pagesSeance - Itgp5j5a9u52ek0hnyk0Pas encore d'évaluation

- TP N°2 Conception Numérique VHDL ObjectifDocument4 pagesTP N°2 Conception Numérique VHDL Objectifر' حيلPas encore d'évaluation

- Rapport Mécatronique Mini ProjetDocument9 pagesRapport Mécatronique Mini ProjetAyoub Bahtat0% (1)

- Rapport Mécatronique Mini Projet PDFDocument9 pagesRapport Mécatronique Mini Projet PDFAyoub BahtatPas encore d'évaluation

- CHOUGDALI CoursAngularDocument154 pagesCHOUGDALI CoursAngularanas bougaiouarPas encore d'évaluation

- Stic b505 Enonce ProjetDocument2 pagesStic b505 Enonce ProjetPacoPas encore d'évaluation

- Examen Session RattrapageDocument1 pageExamen Session Rattrapagedanykihoulou2018Pas encore d'évaluation

- TD Avec CorrigéDocument9 pagesTD Avec Corrigéaziz123100% (1)

- Examen ArchitectureDocument3 pagesExamen ArchitectureSana Souai100% (1)

- Rapport TP Matlab MasDocument8 pagesRapport TP Matlab Mashoussam_atifPas encore d'évaluation

- Chapitre02 - Cours - LabView - 2master - EM - 2023Document47 pagesChapitre02 - Cours - LabView - 2master - EM - 2023Ramadhan BoulbairPas encore d'évaluation

- VHDL Chap 1Document47 pagesVHDL Chap 1AdrianaPas encore d'évaluation

- D412INF10SDocument15 pagesD412INF10SOtia ObaPas encore d'évaluation

- E4 Sirfi 2Document2 pagesE4 Sirfi 2Sirfi DannePas encore d'évaluation

- PFA2Document20 pagesPFA2Firas KACHROUDIPas encore d'évaluation

- Cimasi 2002 CHAMIDocument8 pagesCimasi 2002 CHAMIIssam SteitPas encore d'évaluation

- Rapport PfeDocument23 pagesRapport PfeOussama BourasPas encore d'évaluation

- TP 5Document2 pagesTP 5Ilias HaboubiPas encore d'évaluation

- Mini-Projet - Ecoul. en Cavité - M2 - Installation - CFD Et Logiciels - 2022-2023-1Document17 pagesMini-Projet - Ecoul. en Cavité - M2 - Installation - CFD Et Logiciels - 2022-2023-1Noor MalakPas encore d'évaluation

- Web Bac1 IsteDocument126 pagesWeb Bac1 IsteAntonio SANTOSPas encore d'évaluation

- Corrigé DEVOWFS-V1Document10 pagesCorrigé DEVOWFS-V1anwarsbr2004Pas encore d'évaluation

- helabenghorbelL2SEM OdtDocument17 pageshelabenghorbelL2SEM OdtHela Ben GhorbelPas encore d'évaluation

- Chap 0Document6 pagesChap 0Louis PouchepadassPas encore d'évaluation

- Examen CAR 20092010Document2 pagesExamen CAR 20092010Noureddine HaouariPas encore d'évaluation

- Cahier Des TP Capteurs-GESI-1Document17 pagesCahier Des TP Capteurs-GESI-1chaimae ouarsalPas encore d'évaluation

- VHDL LearningDocument9 pagesVHDL LearningAZEDDINEPas encore d'évaluation

- TP N°1 Résolution NumériqueDocument9 pagesTP N°1 Résolution NumériqueEmmanuel MaxPas encore d'évaluation

- Chapitre IV. COURS-Parie 1Document15 pagesChapitre IV. COURS-Parie 1Ouail oulhassiPas encore d'évaluation

- LOG2410 Final1 A2008 QSDocument15 pagesLOG2410 Final1 A2008 QSMANAÏ BelighPas encore d'évaluation

- VlsiDocument13 pagesVlsiyassine_naciri5127100% (1)

- PPW - TD DIAGRAMME DE Séquence - SolutionDocument9 pagesPPW - TD DIAGRAMME DE Séquence - SolutionMarwan Rguibi100% (1)

- TP OciDocument26 pagesTP OciMoahmed Amine SadiqPas encore d'évaluation

- 01 Projet NOTÉ BigData DataSciencesDocument4 pages01 Projet NOTÉ BigData DataSciencesNancy DobéPas encore d'évaluation

- Projet MSI 2023 2024Document2 pagesProjet MSI 2023 2024Nouha NakotiPas encore d'évaluation

- Compte Rendu TP Registre Universel (ZENDOUI LMOURADI)Document7 pagesCompte Rendu TP Registre Universel (ZENDOUI LMOURADI)Mehdi ZendaouiPas encore d'évaluation

- VHDL AMS Chapitre 1Document17 pagesVHDL AMS Chapitre 1Hossam El KhiariPas encore d'évaluation

- Cahier Des Charges FinaleDocument2 pagesCahier Des Charges FinaleWafa HbPas encore d'évaluation

- Informatique Baccalaureat - Blanc CD 2022Document3 pagesInformatique Baccalaureat - Blanc CD 2022kofane yakanaPas encore d'évaluation

- Chapitre IDocument27 pagesChapitre Iyes i canPas encore d'évaluation

- Memoire Master Conduite de Projets InformatiquesDocument109 pagesMemoire Master Conduite de Projets InformatiquesChristian BibouePas encore d'évaluation

- SQL Injection Analysis Detection and Prevention FRDocument88 pagesSQL Injection Analysis Detection and Prevention FROussama IsmailiPas encore d'évaluation

- Module 06 Connaissance Des Mathematiques BTP TCCTPDocument91 pagesModule 06 Connaissance Des Mathematiques BTP TCCTPBENSAAOUDPas encore d'évaluation

- Initiation A La Simulation Par Matlab/Simulink: Module: Machines Electriques TP 01Document2 pagesInitiation A La Simulation Par Matlab/Simulink: Module: Machines Electriques TP 01yasser GuendouzPas encore d'évaluation

- COURvdvdfDocument41 pagesCOURvdvdfSidi Mohamed Ag BilalPas encore d'évaluation

- TP Dspace Buck Boost InverseurDocument5 pagesTP Dspace Buck Boost Inverseursami debbachePas encore d'évaluation

- Cours Csharp Ado NetDocument38 pagesCours Csharp Ado NetFrançois-Xavier TekoudjouPas encore d'évaluation

- Examen Corrigé GL2 2020Document3 pagesExamen Corrigé GL2 2020traore falyPas encore d'évaluation

- Formation Developpeur .GhezzaDocument10 pagesFormation Developpeur .GhezzaMontassarDaagiPas encore d'évaluation

- 19ade-Jee TPDocument21 pages19ade-Jee TPfab fabPas encore d'évaluation

- TP1 Soc - CodesingDocument13 pagesTP1 Soc - CodesingAhmed TriguiPas encore d'évaluation

- Serie N3Document4 pagesSerie N3Mostafa ChamouriPas encore d'évaluation

- TP2 Webservices SOAP BasicetAxisDocument3 pagesTP2 Webservices SOAP BasicetAxisSara ChahPas encore d'évaluation

- RapportDocument16 pagesRapportBrahim MoumouPas encore d'évaluation

- Modules VHDLDocument109 pagesModules VHDLSidali Zelazel100% (1)

- Exercice 1Document1 pageExercice 1wahbi yassinePas encore d'évaluation

- TP CAO ElectroniqueDocument18 pagesTP CAO ElectroniqueboukariPas encore d'évaluation

- Eii 2021 2022 FRDocument139 pagesEii 2021 2022 FRHugues YoudaPas encore d'évaluation

- JEE Spring MVCDocument23 pagesJEE Spring MVCSabati Abdo100% (1)

- Detection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013D'EverandDetection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013Pas encore d'évaluation

- Livret 2 - Dossier validation VAE - Responsable de travaux Réseaux télécoms Très Haut Débit: 2023, #62D'EverandLivret 2 - Dossier validation VAE - Responsable de travaux Réseaux télécoms Très Haut Débit: 2023, #62Pas encore d'évaluation

- Ift2505 Dualite SyntheseDocument14 pagesIft2505 Dualite SyntheseNeras BlacknPas encore d'évaluation

- Livre Blanc Mise À Blanc Et DSVA1Document5 pagesLivre Blanc Mise À Blanc Et DSVA1Azeddine LAPas encore d'évaluation

- Les Céramiques Industrielles - CarmaDocument122 pagesLes Céramiques Industrielles - CarmaRhimi NajahPas encore d'évaluation

- Rapport de Stagee (BENALDJIA BADREDDINE)Document30 pagesRapport de Stagee (BENALDJIA BADREDDINE)William ويليام TMPas encore d'évaluation

- Demarrage MoteurDocument15 pagesDemarrage MoteurIsmael ZerboPas encore d'évaluation

- Cause Du Défaut: Les I Origine La La Le LaDocument5 pagesCause Du Défaut: Les I Origine La La Le LaLionel Dimitri ATANGANA EDZISNAPas encore d'évaluation

- Panoramah En+frDocument21 pagesPanoramah En+frIrina Ivan-TureanPas encore d'évaluation

- Admission Variable PDFDocument5 pagesAdmission Variable PDFberjarry5938Pas encore d'évaluation

- 1-Auscultation Diagnostic Oa-Cahier InteractifDocument44 pages1-Auscultation Diagnostic Oa-Cahier InteractifJulia Nguem100% (1)

- Manuel de Vol F-16Document244 pagesManuel de Vol F-16LE GOFFPas encore d'évaluation

- BrochureDocument88 pagesBrochureSyd Bristow67% (3)

- Colloque L'intime Et L'inconnu Lyon 2019Document17 pagesColloque L'intime Et L'inconnu Lyon 2019RenePas encore d'évaluation

- FT SmartPos S58Document1 pageFT SmartPos S58fadila fadilaPas encore d'évaluation

- SD - Chap - 3 - Partie - 5 - Gestion Des InterblocagesDocument17 pagesSD - Chap - 3 - Partie - 5 - Gestion Des InterblocagesAbdelwahed ZouaouiPas encore d'évaluation

- 112 4 10 td4 Statique M.A.M.Document2 pages112 4 10 td4 Statique M.A.M.Bilane SergePas encore d'évaluation

- Kpis LogistiqueDocument6 pagesKpis LogistiqueManar HaddadPas encore d'évaluation

- Radio Mobile FR v1 2 NotesDocument27 pagesRadio Mobile FR v1 2 Notesmermoz konanPas encore d'évaluation

- Description de Poste Directeur en Ressources HumainesDocument2 pagesDescription de Poste Directeur en Ressources HumainesouialPas encore d'évaluation

- Repertoire Des Filieres 2019 FRDocument33 pagesRepertoire Des Filieres 2019 FRSSFEP DFEPPas encore d'évaluation

- Referentiel Des Competences Informationnelles AdbuDocument76 pagesReferentiel Des Competences Informationnelles Adbuhakim.hanidaPas encore d'évaluation

- Love Me, Don't Leave Me (FR) 1Document10 pagesLove Me, Don't Leave Me (FR) 1robitaille491Pas encore d'évaluation

- Modele Notice de Poste Septembre2018Document2 pagesModele Notice de Poste Septembre2018Corinne BERNARD0% (1)

- Structure Et Composants Fondamentaux Des Applications Mobiles - PPSXDocument30 pagesStructure Et Composants Fondamentaux Des Applications Mobiles - PPSXأم أحمدPas encore d'évaluation

- Exemples de DemandesDocument11 pagesExemples de DemandesAbderrahim El IdrissiPas encore d'évaluation

- Required Protocoles For PackagingDocument36 pagesRequired Protocoles For PackagingTonyPas encore d'évaluation

- Ch5 Cours MS 2013Document38 pagesCh5 Cours MS 2013Àçh RêfPas encore d'évaluation

- Programme Sous Détail de Prix TFE KangaDocument8 pagesProgramme Sous Détail de Prix TFE KangaKANGAPas encore d'évaluation

- AlgorithmeDocument12 pagesAlgorithmeMohamed FerchichiPas encore d'évaluation