Académique Documents

Professionnel Documents

Culture Documents

TD1 Fpga Aii 2015

Transféré par

Smart Classe67%(3)67% ont trouvé ce document utile (3 votes)

579 vues2 pagesTitre original

TD1_FPGA_AII_2015

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

67%(3)67% ont trouvé ce document utile (3 votes)

579 vues2 pagesTD1 Fpga Aii 2015

Transféré par

Smart ClasseDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

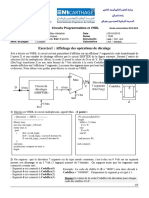

ISET DE GABES AU 2015/2016 sem 1

LAII N5

TD 1

FPGA

Exercice 1: Faire le schéma de l'additionneur complet à l'aide d'un circuit PAL.

Exercice 2: Réaliser un Multiplexeur de 8 vers 1 à l’aide d’un PAL.

Exercice 3: Soit le circuit décrit par le schéma suivant :

Question : Réaliser les mêmes fonctions à l’aide d’un PAL

Exercice 4: Réaliser un générateur de parité (sur 4 bits) avec un FPLA

Exercice 5: Donner les équations logiques des sorties S3, S2, S1, S0 du circuit PAL suivant :

M TAYARI.L Page 1/2 TD1

FPGA LAII51 ISET GABES AU: 2015/2016 Sem 1

Exercice 6: Soit le circuit de la figure suivante représentant une Unité Logique élémentaire.

Ai et Bi sont sur 1bit

C : permet de sélectionner une opération parmi les 4 fonctions que peut effectuer l’Unité logique.

F1 = Ai Xor Bi ; F2 = Ai And Bi

F3 = Ai Nand Bi ; F4 = Ai Nor Bi

Question : Faire le schéma de l’unité en utilisant un FPLA.

Exercice 7: Réaliser les fonctions suivantes à l'aide d'un FPLA.

F1 (A,B,C) = 1 si ( ABC )2 est impair; F1 (A,B,C) = 0 sinon.

F2 (A,B,C) = 1 si ( ABC )2 comporte un nombre impair de " 1 "; F2 (A,B,C) = 0 sinon.

F3 = A2 (Avec A, un nombre sur 2 bits).

Exercice 8: Réaliser un compteur modulo 8 à l’aide d’un PAL séquentiel.

Exercice 9: On désire réaliser 8 signaux d’horloge h0, h1, ….., h7 à partir d’un seul signal h.

Réaliser ce circuit à l’aide de PAL séquentiel.

Exercice10: On dispose d’un PAL séquentiel défini par le schéma suivant :

Questions :

1./ Donner les équations des sorties Si.

2./ Donner les équations des bascules D0 et D1.

3./ Donner la séquence formée par le circuit composé par les deux bascules initialisées à « 0 »

3./ Quel peut être l’utilité de ce circuit.

M TAYARI.L Page 2/2 TD1

Vous aimerez peut-être aussi

- TD1 Fpga 1 1 2Document6 pagesTD1 Fpga 1 1 2saviorPas encore d'évaluation

- Travaux Pratique stm32 tp2Document11 pagesTravaux Pratique stm32 tp2lola itta100% (2)

- TD Fpga Cs 2015Document5 pagesTD Fpga Cs 2015hakim100% (1)

- Corrigé Devoir N°1Document3 pagesCorrigé Devoir N°1Colmain Nassiri100% (1)

- Nizar ProgrammeDocument29 pagesNizar Programmeiramole med100% (1)

- TD - N°2 - EN - Systèmes À MicroprocesseurDocument7 pagesTD - N°2 - EN - Systèmes À MicroprocesseurTimble Puteur100% (2)

- TP1Document5 pagesTP1Mohamed ZarboubiPas encore d'évaluation

- TD 1 S.VHDL 2sticDocument5 pagesTD 1 S.VHDL 2sticIheb ihebPas encore d'évaluation

- TD 10Document2 pagesTD 10Wided MaghraouiPas encore d'évaluation

- Ch6 Pal FplaDocument33 pagesCh6 Pal Fplahassna ait aliPas encore d'évaluation

- Ch6 Pal FplaDocument6 pagesCh6 Pal Fplanoubis100% (2)

- TD1 - Circuit ProgrammablebisDocument4 pagesTD1 - Circuit ProgrammablebisMouhcine Zianee100% (2)

- TD N 1 FpgaDocument3 pagesTD N 1 FpgaLE BARON100% (1)

- TD5 CNDocument4 pagesTD5 CNPapeCheikh SYLLAPas encore d'évaluation

- Examen-Circuits Logiques Programmables L3EEA PDFDocument1 pageExamen-Circuits Logiques Programmables L3EEA PDFOumarou HamissouPas encore d'évaluation

- Corrigé TD5 CNDocument11 pagesCorrigé TD5 CNPapeCheikh SYLLA100% (1)

- On Donne La Description VHDL SuivanteDocument6 pagesOn Donne La Description VHDL Suivantelarbi kfPas encore d'évaluation

- 1-Modes D'adressage: S ° J ' P I 8086Document4 pages1-Modes D'adressage: S ° J ' P I 8086Sara Benseba67% (3)

- TD 03 CorrigeDocument14 pagesTD 03 CorrigerabehPas encore d'évaluation

- Correction TD N°3 CN RegistresDocument4 pagesCorrection TD N°3 CN RegistresKhalil Frikha100% (1)

- Série 3 - Bis - Programmation Assembleur 8085Document3 pagesSérie 3 - Bis - Programmation Assembleur 8085Rottina RossyPas encore d'évaluation

- TD 05 CorrigeeeDocument6 pagesTD 05 CorrigeeeNadhir Mehellou100% (2)

- TD1: Les Circuits Programmables: Exercice 1Document2 pagesTD1: Les Circuits Programmables: Exercice 1Dhouha Benzina100% (1)

- Examens, Exercices, Astuces Tous Ce Que Vous Voulez Les Circuits Combinatoires-multiplexeur-Démultiplexeur-Comparateur-décodeur PDFDocument12 pagesExamens, Exercices, Astuces Tous Ce Que Vous Voulez Les Circuits Combinatoires-multiplexeur-Démultiplexeur-Comparateur-décodeur PDFBabacarDiago50% (6)

- TD 2Document6 pagesTD 2ESIPas encore d'évaluation

- École Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielDocument383 pagesÉcole Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielMahmoud CherfaouiPas encore d'évaluation

- TD-Logique SéquentielleDocument8 pagesTD-Logique SéquentielleFabrice leonel Toukam PoualeuPas encore d'évaluation

- Exo Ensl CoDocument14 pagesExo Ensl CoAnonymous DZg1vCRdj50% (2)

- Série 3Document8 pagesSérie 3Blidi AymenPas encore d'évaluation

- TD4Document1 pageTD4Mounira Tarhouni100% (1)

- Temporisation - Les Variables en AssembleurDocument16 pagesTemporisation - Les Variables en AssembleurMolka ABIDPas encore d'évaluation

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- TD N 2Document4 pagesTD N 2Cesar Malki100% (1)

- Série de TD N°03Document1 pageSérie de TD N°03sarah wiwi100% (1)

- Examen VHDLDocument5 pagesExamen VHDLAnonymous opSQda100% (3)

- Corrigé TD 154Document3 pagesCorrigé TD 154MBADJOUN Daniel100% (1)

- TD Transformée en ZDocument20 pagesTD Transformée en ZamaniPas encore d'évaluation

- TD1 Correction PDFDocument19 pagesTD1 Correction PDFAhmed LakhalPas encore d'évaluation

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- TP1feux Doc 1Document10 pagesTP1feux Doc 1Ahmed TriguiPas encore d'évaluation

- DS VHDL Nov 2015 CORRDocument5 pagesDS VHDL Nov 2015 CORRHadi Ben SaïdPas encore d'évaluation

- tp3 Ing 2015 PDFDocument7 pagestp3 Ing 2015 PDFDorian GreyPas encore d'évaluation

- TD3 Mémoire CorrDocument37 pagesTD3 Mémoire CorrNadia Ben NjimaPas encore d'évaluation

- Devoir VHDL 2Document34 pagesDevoir VHDL 2Simi NePas encore d'évaluation

- TD 1 MicrocontroleurDocument5 pagesTD 1 MicrocontroleursilonePas encore d'évaluation

- VhdlexDocument10 pagesVhdlexRiyadh Ben AbdallahPas encore d'évaluation

- TD MicrocontroleurDocument20 pagesTD MicrocontroleurMed100% (3)

- Correction Du td1 ArmDocument2 pagesCorrection Du td1 Armazza memmi100% (1)

- tp1 Additionneur-Soustracteur CompletDocument10 pagestp1 Additionneur-Soustracteur Completapi-272374810Pas encore d'évaluation

- Série 5Document3 pagesSérie 5Blidi AymenPas encore d'évaluation

- 1-STM32 GPIO RegDocument59 pages1-STM32 GPIO RegSoumri IchrakPas encore d'évaluation

- TIMER0Document78 pagesTIMER0Brahim Attia100% (1)

- Serie TD1Document5 pagesSerie TD1Sarah NourPas encore d'évaluation

- Document Formation Mikroc FinaleDocument133 pagesDocument Formation Mikroc FinaleGaddour TriguiPas encore d'évaluation

- Projets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadD'EverandProjets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadPas encore d'évaluation

- td1 ENADocument2 pagestd1 ENAwafa wafaPas encore d'évaluation

- TD 01 FPGA CorrectionDocument2 pagesTD 01 FPGA CorrectionAmal BarhoumPas encore d'évaluation

- TD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence InformatiqueDocument4 pagesTD 1: Systèmes Logiques Et Architecture Des Ordinateurs: Filière: 1 Année Licence Informatique4qh5xx7g6vPas encore d'évaluation

- TP1 CCDocument2 pagesTP1 CCRania Ben AmmarPas encore d'évaluation

- B2 BDump LoadDocument15 pagesB2 BDump LoadOmar ChPas encore d'évaluation

- Mosquitto Installation Utilisation SBDocument7 pagesMosquitto Installation Utilisation SBSmart ClassePas encore d'évaluation

- ATELIER IoTDocument6 pagesATELIER IoTSmart ClassePas encore d'évaluation

- Insa Lora Esp8266Document6 pagesInsa Lora Esp8266Smart ClassePas encore d'évaluation

- Plan Temps Reel Embarqué Master ProDocument3 pagesPlan Temps Reel Embarqué Master ProSmart ClassePas encore d'évaluation

- MASTER PRO de Genie ElectriqueDocument39 pagesMASTER PRO de Genie ElectriqueSmart ClassePas encore d'évaluation

- Page de Garde COURS - LINUXDocument1 pagePage de Garde COURS - LINUXSmart ClassePas encore d'évaluation

- 08 PSOC Fiche UART MATLABDocument15 pages08 PSOC Fiche UART MATLABSmart ClassePas encore d'évaluation

- Formation - PDF - Conception de Cartes - Circuits ImprimésDocument2 pagesFormation - PDF - Conception de Cartes - Circuits ImprimésSmart ClassePas encore d'évaluation

- InterruptionsDocument25 pagesInterruptionsImaneKarkabaPas encore d'évaluation

- Mini Projet Thermometre 3leds-2Document4 pagesMini Projet Thermometre 3leds-2Smart ClassePas encore d'évaluation

- Lorawan Virtualisation Bertrand Degeldt 2019Document17 pagesLorawan Virtualisation Bertrand Degeldt 2019Smart ClassePas encore d'évaluation

- ArduinoDocument6 pagesArduinoSmart ClassePas encore d'évaluation

- Programmation Système: IFT-17584 Semaine 03Document68 pagesProgrammation Système: IFT-17584 Semaine 03Smart ClassePas encore d'évaluation

- Internet Des Objets, Synthèse: Séminaire de 2 Jours Réf: IOB - Prix 2021: 2 030 HTDocument3 pagesInternet Des Objets, Synthèse: Séminaire de 2 Jours Réf: IOB - Prix 2021: 2 030 HTSmart ClassePas encore d'évaluation

- Assembleur CompilateurDocument8 pagesAssembleur CompilateurSmart ClassePas encore d'évaluation

- administrationReseauWeb PDFDocument79 pagesadministrationReseauWeb PDFYassine SabekPas encore d'évaluation

- Chap 1Document19 pagesChap 1Houty KarimPas encore d'évaluation

- TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Document15 pagesTP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Smart ClassePas encore d'évaluation

- TP GSMDocument9 pagesTP GSMSmart ClassePas encore d'évaluation

- TRACSOLDocument1 pageTRACSOLSmart ClassePas encore d'évaluation

- Programmation Systeme ghbnvc765Document80 pagesProgrammation Systeme ghbnvc765Trop FreshloïcPas encore d'évaluation

- AscenseurDocument16 pagesAscenseurSmart ClassePas encore d'évaluation

- TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Document15 pagesTP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Smart ClassePas encore d'évaluation

- DSP1Document28 pagesDSP1Boubaker HarhatiPas encore d'évaluation

- Linux 2Document4 pagesLinux 2Smart ClassePas encore d'évaluation

- Compteur Par 4 Décodeur 1 Parmi 4 Affichage Reset: TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Document29 pagesCompteur Par 4 Décodeur 1 Parmi 4 Affichage Reset: TP Systeme Numerique Embarque: Tutorial Xilinx Zybo Vivado 09/08/2015Smart ClassePas encore d'évaluation

- ZYNQDocument13 pagesZYNQSmart ClassePas encore d'évaluation

- Circuits Numeriques Et Synthese Logique, Un Outil - VHDLDocument178 pagesCircuits Numeriques Et Synthese Logique, Un Outil - VHDLMahmoud DoughanPas encore d'évaluation

- Linux 1Document7 pagesLinux 1Smart ClassePas encore d'évaluation