Académique Documents

Professionnel Documents

Culture Documents

On Donne La Description VHDL Suivante

Transféré par

larbi kfTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

On Donne La Description VHDL Suivante

Transféré par

larbi kfDroits d'auteur :

Formats disponibles

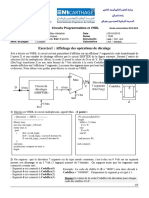

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

Série TD n°1 (Circuits combinatoires)

Exercice 1

On donne la description VHDL suivante :

Library ieee ;

Use ieee.std_logic_1164.all;

Use work.std_arith.all;

Entity Portes is

Port (A, B: in std_logic;

Y1, Y2, Y3, Y4, Y5, Y6, Y7: out std_logic);

end Portes ;

Architecture Arch_Portes of Portes is

begin

Y1<= A and B;

Y2<= A or B;

Y3<= A xor B;

Y4<= not A;

Y5<= A nand B;

Y6<= A nor B;

Y7<= not (A xor B);

end Arch_Portes;

1) A partir du fichier donner les noms des bibliothèques utilisées.

2) Quel est le nom de l’entité ? Quel est le nom de l’architecture ?

3) Représenter le schéma fonctionnel de la fonction. On placera naturellement les

entrées à gauche et les sorties à droites.

Exercice 2

B A S

0 0 1

0 1 1

1 0 1

1 1 0

1) Faire la description VHDL de ce circuit ?

2) De quel circuit s’agit-il ?

3) Dessiner le schéma bloc de ce circuit ?

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

71

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

Exercice 3

Entrées Sorties

A3 A2 A1 A0 S1 S0

0 1 0 1 1 1

0 1 1 0 0 1

1 1 0 1 1 0

1) Faire la description VHDL de ce circuit ?

On peut passer de std_logic vers std_logic_vector en présentant les entrées et les sorties

comme des vecteurs respectivement.

2) Ecrire une description VHDL qui utilise les entrées et les sorties en vecteurs dans

une entité et plusieurs architectures qui contiennent différentes descriptions :

✓ Affectation sélective (with… select… when) ?

✓ Affectation conditionnelle (when… else) ?

✓ Structure de test (if… then… else)?

✓ Structure de choix (case… is… when) ?

Exercice 4

Soit la description VHDL suivante :

Library ieee ;

Use ieee.std_logic_1164.all;

Entity Fonction_mystere is

Port (e0, e1: in std_logic;

sel: in std_logic;

Sort: out std_logic);

end Fonction_mystere ;

Architecture V0 of Fonction_mystere is

begin

Sort <= e0 when sel= '0' else e1;

end V0;

1) Quelle est la fonction réalisée par cette architecture ?

2) Réécrire la même fonction avec la structure de test ?

3) Pour cette architecture, recopier le chronogramme suivant et complétez le avec la

trace du signal « sort » :

sel

e0

e1

sort

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

72

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

Solution de la série TD n°1 (Circuits combinatoires)

Exercice 1

1) les noms des bibliothèques utilisées.

✓ La bibliothèque IEEE du standard VHDL,

✓ Le paquetage standard pour ieee.Std_logic_1164 pour typé les entrées/ sorties et les

signaux internes,

✓ Le paquetage personnalisé par l’utilisateur pour work.std_arith pour spécifié les

fonctions utilisées dans le programme VHDL.

2) Quel est le nom de l’entité ? Portes

Quel est le nom de l’architecture ? Arch_Portes

3) Représenter le schéma fonctionnel de la fonction.

A Y1

AND

B

Y5

NOT

Y2

OR

NOT Y6

XOR

Y3

NOT Y7

NOT Y4

Exercice 2

1) Faire la description VHDL de ce circuit ?

Library ieee ;

Use ieee.std_logic_1164.all ;

Use ieee.std_logic_arith.all ;

Entity Ex_2 is

Port (A, B: in std_logic;

S: out std_logic);

end Ex_2 ;

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

73

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

Architecture arch_ex2 of Ex_2 is

begin

S <= '0' when A= '1' and B='1' else S <= '1';

end arch_ex2;

2) De quel circuit s’agit-il ? Il s’agit du circuit NAND

3) Le schéma bloc de ce circuit :

A

NAND

S

B

Exercice 3

1) Faire la description VHDL de ce circuit ?

Library ieee ;

Use ieee.std_logic_1164.all ;

Use ieee.std_logic_arith.all ;

Entity Ex_3 is

Port (A0, A1, A2, A3: in std_logic;

S0, S1: out std_logic);

end Ex_3 ;

Architecture arch_ex3 of Ex_3 is

begin

process (A0, A1, A2, A3)

begin

if (A0='1' and A1='0' and A2='1' and A3='0') then S0<= '1'; S1<='1' ;

else if (A0='0' and A1='1' and A2='1' and A3='0') then S0<= '1'; S1<='0' ;

else if (A0='1' and A1='0' and A2='1' and A3='1') then S0<= '0'; S1<='1' ;

end if;

end if;

end if;

end process;

end arch_ex2;

2) Ecrire une description VHDL qui utilise les entrées et les sorties en vecteurs dans

une entité et plusieurs architectures qui contiennent différentes descriptions :

✓ Affectation sélective (with… select… when) ?

✓ Affectation conditionnelle (when… else) ?

✓ Structure de test (if… then… else)?

✓ Structure de choix (case… is… when) ?

Library ieee ;

Use ieee.std_logic_1164.all ;

Use ieee.std_logic_arith.all ;

Entity vecteur is

Port (A: in std_logic_vector (3 downto 0);

S: out std_logic_vector (1 downto 0));

end vecteur;

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

74

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

✓ Architecture with_select of vecteur is

begin

with A select

S<= ''11'' when ''0101'',

''01'' when ''0110'',

''10'' when ''1101'',

''00'' when others;

end with_select;

✓ Architecture when_else of vecteur is

begin

S<= ''11'' when A=''0101'' else

''01'' when A=''0110'' else

''10'' when A=''1101'';

end when_else;

✓ Architecture if_then of vecteur is

begin

process (A)

begin

if A=''0101'' then S<= ''11'' ;

else if A=''0110'' then S<= ''01'' ;

else if A=''1101'' then S<= ''10'' ;

end if;

end if;

end if;

end process;

end if_then;

✓ Architecture case_is of vecteur is

begin

process (A)

begin

case A is

when ''0101'' => S<= ''11'' ;

when ''0110'' => S<= ''01'' ;

when ''1101'' => S<= ''10'' ;

when others => S<= ''00'' ;

end case;

end process;

end case_is;

Exercice 4

1) Quelle est la fonction réalisée par cette architecture ?

e0 Sel Sort

MUX

e1 0 E0

sort 1 E1

sel

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

75

Université Abou-Bekr Belkaid Tlemcen M1 ST Télécommunication

Faculté de Technologie Circuits programmables FPGA

Département de Télécommunication

E1 E0 sel sort

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

Donc c’est un Multiplexeur à 2 entrées, une entrée de sélection et une sortie.

2) Réécrire la même fonction avec la structure de test ?

Library ieee ;

Use ieee.std_logic_1164.all;

Entity Fonction_mystere is

Port (e0, e1: in std_logic;

sel: in std_logic;

Sort: out std_logic);

end Fonction_mystere ;

Architecture structure_de_test of Fonction_mystere is

begin

process (e0, e1, sel)

begin

if sel= '0' then Sort <= e0; else Sort <= e1;

end if;

end process;

end structure_de_test;

3) complétez le chronogramme suivant avec la trace du signal « sort » :

sel

e0

e1

sort

Circuits programmable FPGA Dr. MOHAMMED ZAKARYA BABA-AHMED

76

Vous aimerez peut-être aussi

- CHAPITRE 2 Système de ProtectionDocument37 pagesCHAPITRE 2 Système de ProtectionMinyar Rezgui100% (1)

- Corrigé Partiel VHDL FPGA M1 ELN SE 2020Document6 pagesCorrigé Partiel VHDL FPGA M1 ELN SE 2020yasmine hmn100% (1)

- Ch6 Pal FplaDocument33 pagesCh6 Pal Fplahassna ait aliPas encore d'évaluation

- Technical Description For Urban Outdoor V5 SFR - 1door FP2 Rev 2 (B-380049Document24 pagesTechnical Description For Urban Outdoor V5 SFR - 1door FP2 Rev 2 (B-380049Stephane VILETTEPas encore d'évaluation

- Chap2 Conditionnement Électronique Des CapteursDocument53 pagesChap2 Conditionnement Électronique Des CapteursCoc Caine100% (1)

- VHDL Code For Flipflop - D, JK, SR, T PDFDocument7 pagesVHDL Code For Flipflop - D, JK, SR, T PDFBrahim LakridPas encore d'évaluation

- Examen VHDLDocument5 pagesExamen VHDLAnonymous opSQda100% (4)

- Devoir VHDL 2Document34 pagesDevoir VHDL 2Simi NePas encore d'évaluation

- Examen VHDL 2eme Session 2008 Mondir PDFDocument20 pagesExamen VHDL 2eme Session 2008 Mondir PDFIman El Hilah100% (1)

- TTL Et CmosDocument5 pagesTTL Et Cmosgirl Tech100% (3)

- Examen SE 2018 - 2019Document2 pagesExamen SE 2018 - 2019aymen balaPas encore d'évaluation

- École Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielDocument383 pagesÉcole Polytechnique de Montréal Page 1/12 Département de Génie Informatique Et Génie LogicielMahmoud CherfaouiPas encore d'évaluation

- Serie01 SemiconducteurDocument5 pagesSerie01 SemiconducteurGoldFreind100% (2)

- TD5 CNDocument4 pagesTD5 CNPapeCheikh SYLLAPas encore d'évaluation

- GSET3 Cours Machines A Etats 1Document13 pagesGSET3 Cours Machines A Etats 1raafatePas encore d'évaluation

- Devoir Dmoicile CorrectionDocument8 pagesDevoir Dmoicile CorrectionSimo Light100% (1)

- Examen VHDL Janv 2016 - CorrDocument8 pagesExamen VHDL Janv 2016 - CorrHadi Ben SaïdPas encore d'évaluation

- TD1 - Circuit ProgrammablebisDocument4 pagesTD1 - Circuit ProgrammablebisMouhcine Zianee100% (2)

- Corrigé TD5 CNDocument11 pagesCorrigé TD5 CNPapeCheikh SYLLA100% (1)

- TD Fpga Cs 2015Document5 pagesTD Fpga Cs 2015hakim100% (1)

- TD3 VHDL Compteurs Et RegistresDocument12 pagesTD3 VHDL Compteurs Et RegistresKais Bahrouni100% (1)

- TD N 3 FpgaDocument2 pagesTD N 3 FpgaLE BARON100% (1)

- Travaux Dirigés FPGA & VHDLDocument28 pagesTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- tp1 Additionneur-Soustracteur CompletDocument10 pagestp1 Additionneur-Soustracteur Completapi-272374810Pas encore d'évaluation

- TD1: Les Circuits Programmables: Exercice 1Document2 pagesTD1: Les Circuits Programmables: Exercice 1Dhouha Benzina100% (1)

- l2 en TDDocument36 pagesl2 en TDSissi Dadi100% (2)

- Exercices VHDLDocument3 pagesExercices VHDLKamel Sahraoui100% (1)

- Correction VHDLDocument5 pagesCorrection VHDLReal MadridPas encore d'évaluation

- VhdlexDocument10 pagesVhdlexRiyadh Ben AbdallahPas encore d'évaluation

- DS VHDL Nov 2015 CORRDocument5 pagesDS VHDL Nov 2015 CORRHadi Ben SaïdPas encore d'évaluation

- Corigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique NumériqueDocument5 pagesCorigé Type Eln.-num.-Av.-fpgAVHDL M1-InST Électronique Numériques240% (1)

- Serie TD1Document5 pagesSerie TD1Sarah NourPas encore d'évaluation

- TD2018Document21 pagesTD2018David SalahPas encore d'évaluation

- Ch6 Pal FplaDocument6 pagesCh6 Pal Fplanoubis100% (2)

- Examen VHDL +correction 1ere Session 2009Document12 pagesExamen VHDL +correction 1ere Session 2009Walid LELLOUCHIPas encore d'évaluation

- Serie TD5Document9 pagesSerie TD5Sarah NourPas encore d'évaluation

- TD 1 S.VHDL 2sticDocument5 pagesTD 1 S.VHDL 2sticIheb ihebPas encore d'évaluation

- Correction TD1 Programmation DSPDocument5 pagesCorrection TD1 Programmation DSPmohamedPas encore d'évaluation

- Examen VHDL +correction 1ere Session 2008Document5 pagesExamen VHDL +correction 1ere Session 2008nesrine ninaPas encore d'évaluation

- TD3: Synthèse VHDL: Exercice 1Document5 pagesTD3: Synthèse VHDL: Exercice 1Mohamed Aziz Ben RomdhanePas encore d'évaluation

- TD 10Document2 pagesTD 10Wided MaghraouiPas encore d'évaluation

- m1 Instrumentation - TD Fpga-VhdlDocument6 pagesm1 Instrumentation - TD Fpga-VhdlazedPas encore d'évaluation

- Les Circuits Logiques Programmables FPGADocument29 pagesLes Circuits Logiques Programmables FPGAOUSSAMA ELHJOUJI0% (1)

- TD2 VHDL Mars 2019Document2 pagesTD2 VHDL Mars 2019Belkhiri MohammedPas encore d'évaluation

- Examen-Circuits Logiques Programmables L3EEA PDFDocument1 pageExamen-Circuits Logiques Programmables L3EEA PDFOumarou HamissouPas encore d'évaluation

- Cours VHDL 10 Partie8 Test BenchesDocument14 pagesCours VHDL 10 Partie8 Test BenchesSalahe LaouarPas encore d'évaluation

- TD 01 FPGA CorrectionDocument2 pagesTD 01 FPGA CorrectionAmal BarhoumPas encore d'évaluation

- TD 2Document6 pagesTD 2ESIPas encore d'évaluation

- Fascicule de TP FpgaDocument32 pagesFascicule de TP FpgaHichem HamdiPas encore d'évaluation

- TP 1Document2 pagesTP 1Khaled LahianiPas encore d'évaluation

- TD1 Fpga Aii 2015Document2 pagesTD1 Fpga Aii 2015Smart Classe67% (3)

- TD-Logique SéquentielleDocument8 pagesTD-Logique SéquentielleFabrice leonel Toukam PoualeuPas encore d'évaluation

- 04 Microprocesseur 8086Document18 pages04 Microprocesseur 8086nesrine ninaPas encore d'évaluation

- Cours VHDLDocument62 pagesCours VHDLBrice Albin Fotso GhomdimPas encore d'évaluation

- TD N 1 FpgaDocument3 pagesTD N 1 FpgaLE BARON100% (1)

- Exam 2017Document2 pagesExam 2017Mohamed Hmamouch100% (2)

- TD1 Fpga 1 1 2Document6 pagesTD1 Fpga 1 1 2saviorPas encore d'évaluation

- Cours Co-DesignDocument34 pagesCours Co-DesignFatima100% (1)

- Familiarisation Avec Le Simulateur "8085 Simulator"Document15 pagesFamiliarisation Avec Le Simulateur "8085 Simulator"Med Djameleddine BougrinePas encore d'évaluation

- Chap3 Circuitscombinatoires M1 2023Document14 pagesChap3 Circuitscombinatoires M1 2023Sãhãzà RandriamaharavoPas encore d'évaluation

- Chap5 VHDL UnlockedDocument21 pagesChap5 VHDL UnlockedilyPas encore d'évaluation

- VHDL Instructions Concurrentes - Intressant - CoursDocument28 pagesVHDL Instructions Concurrentes - Intressant - CoursDr. Chekir AmiraPas encore d'évaluation

- Les Bascules Et Registres: A.LebrunDocument30 pagesLes Bascules Et Registres: A.LebrunMouhcine ZianeePas encore d'évaluation

- Devoir de Synthèse N°1 - Technologie CHAINE D'EMBALLAGE DES FEUILLES DE PAPIER - Bac Technique (2012-2013) MR Hadjkacem AbdelkarimDocument11 pagesDevoir de Synthèse N°1 - Technologie CHAINE D'EMBALLAGE DES FEUILLES DE PAPIER - Bac Technique (2012-2013) MR Hadjkacem Abdelkarimيس المباركيPas encore d'évaluation

- Circuits ProgrammablesDocument95 pagesCircuits ProgrammablesRyheb B'MRzPas encore d'évaluation

- Serie Derivation Court CircuitDocument2 pagesSerie Derivation Court CircuitOubey MadaniPas encore d'évaluation

- Dépliant STRDocument2 pagesDépliant STRSid lefouPas encore d'évaluation

- Formation ARDUINO 1-2 - 2020Document34 pagesFormation ARDUINO 1-2 - 2020walid benghenaiaPas encore d'évaluation

- Série D'exercices N°3 Lycée Pilote - Physique - Dipole RC - Bac Toutes Sections (2018-2019) MR Mabrouki SalahDocument23 pagesSérie D'exercices N°3 Lycée Pilote - Physique - Dipole RC - Bac Toutes Sections (2018-2019) MR Mabrouki SalahWiem Benchahboun0% (1)

- 2ste - Tapis de Course Interactif - EleveDocument76 pages2ste - Tapis de Course Interactif - EleveRachid anknafPas encore d'évaluation

- Exer Solutions TelecommDocument30 pagesExer Solutions TelecommAbdelfatah FerhatPas encore d'évaluation

- 4ème Dangers Du Courant Du SecteurDocument8 pages4ème Dangers Du Courant Du SecteurCamille YaoPas encore d'évaluation

- 039 Électricité FiniDocument4 pages039 Électricité FiniAnae GlamportPas encore d'évaluation

- XENS MP PhysSI 2014 EmissionLumiere SujetDocument12 pagesXENS MP PhysSI 2014 EmissionLumiere SujetLucas ImrenPas encore d'évaluation

- Iec 61000-2-11-1999Document40 pagesIec 61000-2-11-1999Venkataramanan SPas encore d'évaluation

- Theme: Option: ElectromecaniqueDocument103 pagesTheme: Option: ElectromecaniqueAimen PicaroPas encore d'évaluation

- Fiche Métier Technicien de Maintenance ÉlectriqueDocument3 pagesFiche Métier Technicien de Maintenance ÉlectriqueOuaamar RachaPas encore d'évaluation

- TP Caracthéristique AOPDocument13 pagesTP Caracthéristique AOPBrahim ELGBPas encore d'évaluation

- Nouveau Document Microsoft WordDocument11 pagesNouveau Document Microsoft Wordadel moulahouPas encore d'évaluation

- Devoir de Contrôle N°1 2ème D7Document2 pagesDevoir de Contrôle N°1 2ème D7Jridette Walid100% (2)

- ManuscritTheseFinal Maria TIMOFEEVADocument233 pagesManuscritTheseFinal Maria TIMOFEEVACoc CainePas encore d'évaluation

- Memoire 26 PDFDocument22 pagesMemoire 26 PDFThe geek CuestaPas encore d'évaluation

- PDF Projet de Realisation de L'additionneur Soustracteur, Du Comparateur Et de La Conception de Compteurs Synchrones Et AsynchronesDocument38 pagesPDF Projet de Realisation de L'additionneur Soustracteur, Du Comparateur Et de La Conception de Compteurs Synchrones Et Asynchronesappro soseterPas encore d'évaluation

- TD 2 BisDocument2 pagesTD 2 BisDJEMAI OumimaPas encore d'évaluation

- Johnny II Asc FR en Es deDocument52 pagesJohnny II Asc FR en Es deIonescu BogdanPas encore d'évaluation

- Devoir de Synthèse N°1 2009 2010 (Abidi Bacem)Document2 pagesDevoir de Synthèse N°1 2009 2010 (Abidi Bacem)oussema guenichiPas encore d'évaluation

- Sony Pvm-8042q Pvm-8045q Pvm-9042qm Pvm-9045qm Pvm-9045pm Chassis S Mic SMDocument108 pagesSony Pvm-8042q Pvm-8045q Pvm-9042qm Pvm-9045qm Pvm-9045pm Chassis S Mic SMtongshadowPas encore d'évaluation

- Soutenance Du Rapport de Stage OpérateurDocument26 pagesSoutenance Du Rapport de Stage Opérateursage blanqui nzaouPas encore d'évaluation