Académique Documents

Professionnel Documents

Culture Documents

TD 1 Fpga

Transféré par

amira0 évaluation0% ont trouvé ce document utile (0 vote)

55 vues1 pageTitre original

TD 1 FPGA

Copyright

© © All Rights Reserved

Formats disponibles

DOCX, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

55 vues1 pageTD 1 Fpga

Transféré par

amiraDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOCX, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 1

M1 ST/ESE TD4 FPGA

EX 1 :

A) Soit à décrire en VHDL un additionneur 1 bit schématisé par le bloc suivant :

A et B sont les entrées binaires.

S : résultat de l’addition

C : bit de retenue (carry)

1) Etablir la table de vérité de l’additionneur 1 bit.

2) Décrire en VHDL, l’entité de l’additionneur qu’on appellera add1.

3) Décrire en VHDL, l’architecture flot de données de l’entité add1 avec portes logiques.

4) Décrire en VHDL, l’architecture structurelle de l’entité add1.

B) L’additionneur précédent est appelé un demi-additionneur.

1) Pourquoi ?

2) Montrer comment peut-on construire un additionneur complet à 1 bit en utilisant

un/des demi-additionneur(s).

3) Décrire en VHDL, l’entité et l’architecture structurelle de l’additionneur complet.

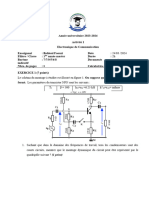

EX 2 :

Décrire en VHDL le circuit combinatoire suivant avec une architecture structurelle tout en

décrivant les différents composants avec des architectures comportementales.

Vous aimerez peut-être aussi

- VHDL Travaux2TP20180701ABDEL1Document8 pagesVHDL Travaux2TP20180701ABDEL1Tarek BouazzaPas encore d'évaluation

- TD1 Electronique Numerique 2023Document3 pagesTD1 Electronique Numerique 2023wjdj832Pas encore d'évaluation

- 19 VHDLDocument15 pages19 VHDLAmina GhardallouPas encore d'évaluation

- TD1 VHDLDocument3 pagesTD1 VHDLbejaoui yosrPas encore d'évaluation

- tp2 VHDLDocument4 pagestp2 VHDLAya BchiniPas encore d'évaluation

- Serie TD1Document5 pagesSerie TD1Sarah NourPas encore d'évaluation

- Exo Ensl CoDocument14 pagesExo Ensl CoAnonymous DZg1vCRdj50% (2)

- TP Mezouari Master-FpgaDocument4 pagesTP Mezouari Master-FpgaSalma OualikPas encore d'évaluation

- TD 2022-23Document3 pagesTD 2022-23elhaoudar.nassimaPas encore d'évaluation

- TD1 VHDLLDocument5 pagesTD1 VHDLLMontaha Ben SalemPas encore d'évaluation

- AB Cours Automatisme Chap 2 Et 3Document17 pagesAB Cours Automatisme Chap 2 Et 3MhB SaAdPas encore d'évaluation

- TDVHDLDocument5 pagesTDVHDLar ijPas encore d'évaluation

- Exo EnslDocument14 pagesExo EnslDhiaeddine AtiPas encore d'évaluation

- TD N 3 FpgaDocument2 pagesTD N 3 FpgaLE BARON100% (1)

- TD N 4 (Supplemetaire) FpgaDocument2 pagesTD N 4 (Supplemetaire) FpgaLE BARONPas encore d'évaluation

- VHDL ExercicesDocument6 pagesVHDL ExercicesHazem HaPas encore d'évaluation

- TP N°2 Conception Numérique VHDL ObjectifDocument4 pagesTP N°2 Conception Numérique VHDL Objectifر' حيلPas encore d'évaluation

- Travaux Dirigés 2 Les Circuits Logiques CombinatoiresDocument3 pagesTravaux Dirigés 2 Les Circuits Logiques CombinatoiresLassaad AKROUTPas encore d'évaluation

- Recueil D Exercices Logique ProgrammableDocument19 pagesRecueil D Exercices Logique ProgrammableEl hanif SaadPas encore d'évaluation

- CH34 QuestionsDocument12 pagesCH34 QuestionsaminePas encore d'évaluation

- TP1 Conception Circuits Num ProgrammablesDocument2 pagesTP1 Conception Circuits Num ProgrammablesGhofran NeiliPas encore d'évaluation

- TD Technologie ElectroniqueDocument2 pagesTD Technologie ElectroniqueMouna Ben SmidaPas encore d'évaluation

- Correction Travaux Dirigés 2 Les Circuits Logiques CombinatoiresDocument7 pagesCorrection Travaux Dirigés 2 Les Circuits Logiques CombinatoiresLassaad AKROUTPas encore d'évaluation

- TD Systeme ElectroniqueDocument9 pagesTD Systeme ElectroniquePëgüÿ CräqüäntPas encore d'évaluation

- TD TP2Document2 pagesTD TP2mahdi ben aliPas encore d'évaluation

- TD5 - 2021Document1 pageTD5 - 2021scar lightPas encore d'évaluation

- TP 2Document1 pageTP 2kaouPas encore d'évaluation

- TPno3 CircuitscombinatoiresAdditionneurbinaireDocument2 pagesTPno3 CircuitscombinatoiresAdditionneurbinairehassina5kertPas encore d'évaluation

- Chapitreiicircuitscombinatoires 140116153409 Phpapp02 PDFDocument70 pagesChapitreiicircuitscombinatoires 140116153409 Phpapp02 PDFHatim AnasPas encore d'évaluation

- td3 31 3 2020 Avec SolutionDocument8 pagestd3 31 3 2020 Avec Solutionibrahim sghouPas encore d'évaluation

- Activit 2Document5 pagesActivit 2mwinkeudelrioPas encore d'évaluation

- TD2 VHDLDocument2 pagesTD2 VHDLImen SaidiPas encore d'évaluation

- TP1Document5 pagesTP1Mohamed ZarboubiPas encore d'évaluation

- tp2 Ing 2015Document3 pagestp2 Ing 2015abderaouf sakhraouiPas encore d'évaluation

- Le Langage VHDL ELKARIDocument112 pagesLe Langage VHDL ELKARIAhmed DoghmiPas encore d'évaluation

- QCM QuestionsDocument4 pagesQCM Questionshamzaaouni79Pas encore d'évaluation

- VHDLDocument133 pagesVHDLlarbi100% (1)

- TD 2021Document4 pagesTD 2021elhaoudar.nassima100% (1)

- TD 2Document2 pagesTD 2kousseila kouukouPas encore d'évaluation

- TP3 Electr NumériqueDocument7 pagesTP3 Electr NumériqueYoucef BoukhalfaPas encore d'évaluation

- Le Langage VHDL A.elkari PDFDocument122 pagesLe Langage VHDL A.elkari PDFAhmed DoghmiPas encore d'évaluation

- tp1 Ing 2015 PDFDocument3 pagestp1 Ing 2015 PDFyapPas encore d'évaluation

- 04 Doc - Ressource - Instructions - PIC PDFDocument2 pages04 Doc - Ressource - Instructions - PIC PDFAttou MedPas encore d'évaluation

- TP VHDLDocument8 pagesTP VHDLdalel bouaziziPas encore d'évaluation

- 2016 Examen Elec1 EIDD CorrigeDocument7 pages2016 Examen Elec1 EIDD CorrigeAlex FezeuPas encore d'évaluation

- Travaux Dirigés D'electronique Numérique Licence2Document6 pagesTravaux Dirigés D'electronique Numérique Licence2Timble Puteur100% (1)

- Serie 1Document4 pagesSerie 1souha ben abdessalemPas encore d'évaluation

- Cours - Chapitre1 TunDocument61 pagesCours - Chapitre1 TunHoucem B HsnPas encore d'évaluation

- TP01 PDFDocument11 pagesTP01 PDFMed Mohamed100% (1)

- Lecon N - 1 - Les Circuits Integrés CombinatoiresDocument15 pagesLecon N - 1 - Les Circuits Integrés CombinatoiresLabossef LabossefchedlyPas encore d'évaluation

- TD 1Document3 pagesTD 1mahmoud01 ayachiPas encore d'évaluation

- TD1 2Document2 pagesTD1 2Nidal Laatab100% (1)

- TD0: Initiation À La Conception Matérielle Par Schéma Travail DemandéDocument2 pagesTD0: Initiation À La Conception Matérielle Par Schéma Travail DemandéAhmed GanouniPas encore d'évaluation

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble PuteurPas encore d'évaluation

- Chpitre1 Circuit Combinatoires2Document7 pagesChpitre1 Circuit Combinatoires2N El kechaiPas encore d'évaluation

- TP 4filtre PDFDocument4 pagesTP 4filtre PDFManuel ArzolaPas encore d'évaluation

- Administration ServiceDocument55 pagesAdministration Serviceamira100% (1)

- TD 1 - Paramètres - de - Orbite - SatellitaireDocument2 pagesTD 1 - Paramètres - de - Orbite - SatellitaireamiraPas encore d'évaluation

- SwitchDocument9 pagesSwitchamiraPas encore d'évaluation

- Examen VHDLDocument1 pageExamen VHDLamiraPas encore d'évaluation

- Examen C++Document3 pagesExamen C++amiraPas encore d'évaluation

- DocementDocument2 pagesDocementamiraPas encore d'évaluation