Académique Documents

Professionnel Documents

Culture Documents

TD TP2

Transféré par

mahdi ben aliTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TD TP2

Transféré par

mahdi ben aliDroits d'auteur :

Formats disponibles

Architectures reconigurables et VHDL

TD_TP N°2 : Concepts VHDL

Exercice

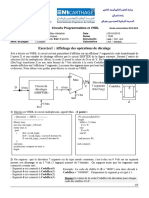

Soit à décrire en VHDL le circuit suivant permettant d’afficher sur un afficheur 7 segments le

code hexadécimal de l’entrée D et son résultat de décalage effectué par le circuit SHIFTER de la

figure ci-après.

Suivant l’entrée de sélection Sel du multiplexeur (Mux), la sortie Z prend la valeur de D ou de Y.

Par la suite le transcodeur 7 segments (Dec7seg) transforme Z en une suite binaire de 7 bits

affectée à la sortie CodeHex du décodeur. Cette suite sera ensuite affichée sur l’afficheur 7

segments. Les noms des signaux ainsi que leurs tailles sont spécifiés dans la figure ci-après. Nous

allons vous guider pour décrire ce circuit en VHDL.

1) Décrire en VHDL le circuit multiplexeur, appelé Mux.

2) On suppose que le transcodeur 7 segments est de type activé à l’état bas, c'est-à-

dire un 0 logique sur un segment permet son allumage et un 1 logique permet de l’éteindre.

On suppose aussi que les segments sont connectés comme suit :

- Segment a est connecté à CodeHex(0)

- Segment b est connecté à CodeHex(1)

- Segment c est connecté à CodeHex(2)

- Segment d est connecté à CodeHex(3)

- Segment e est connecté à CodeHex(4)

- Segment f est connecté à CodeHex(5)

- Segment g est connecté à CodeHex(6)

Donner la valeur de la sortie CodeHex du transcodeur pour chaque code des

chiffres 0 à F.

3) Décrire en VHDL le transcodeur 7 segments, appelé Dec7seg en utilisant un

processus et l’instruction case du VHDL.

4) Le circuit SHIFTER présenté sur la figure précédente permet 5 fonctions de

décalage en fonction de l’entrée Fct codée sur trois bits. Ces 5 fonctions sont résumées

dans le tableau ci-après.

Donner le code VHDL de ce circuit en utilisant un processus et l’instruction case.

5) Le circuit global aura comme entrées (Fct, D et sel) et comme sortie (CodeHex)

comme présenté dans figure précédente. Donner la description VHDL structurelle du

circuit global qui réutilise des instances des circuits décrits dans les questions précédentes.

6) Coder en VHDL un testbench qui pour la valeur de D égale à "0101", permet de

stimuler toutes les fonctions de décalage et d’afficher le résultat Y sur l’afficheur 7

segments.

Travaux pratiques

L’exercice précédent fera l’objet d’un TP sous modelsim intitulé «projet_TP2 ». Effectuer les

implémentations et simulations adéquates.

Vous aimerez peut-être aussi

- TP1 VHDLDocument9 pagesTP1 VHDLID AbdelPas encore d'évaluation

- TD1 Electronique Numerique 2023Document3 pagesTD1 Electronique Numerique 2023wjdj832Pas encore d'évaluation

- 19 VHDLDocument15 pages19 VHDLAmina GhardallouPas encore d'évaluation

- Rapport Projet AMOUSSE-IHAM-1Document14 pagesRapport Projet AMOUSSE-IHAM-1ackfatiPas encore d'évaluation

- DS VHDL Nov 2015 CORRDocument5 pagesDS VHDL Nov 2015 CORRHadi Ben SaïdPas encore d'évaluation

- SerieN1 VHDL 2022Document3 pagesSerieN1 VHDL 2022Mohamed Bou KhouPas encore d'évaluation

- TD 2021Document4 pagesTD 2021elhaoudar.nassima100% (1)

- td3 31 3 2020 Avec SolutionDocument8 pagestd3 31 3 2020 Avec Solutionibrahim sghouPas encore d'évaluation

- TD N 3 FpgaDocument2 pagesTD N 3 FpgaLE BARON100% (1)

- Le Langage VHDL ELKARIDocument112 pagesLe Langage VHDL ELKARIAhmed DoghmiPas encore d'évaluation

- Le Langage VHDL A.elkari PDFDocument122 pagesLe Langage VHDL A.elkari PDFAhmed DoghmiPas encore d'évaluation

- 06 - TP2 - PROJET QuartusDocument11 pages06 - TP2 - PROJET Quartusmohamed.saidi212001Pas encore d'évaluation

- Application Des Multiplexeurs Et Des DemultiplexeursDocument8 pagesApplication Des Multiplexeurs Et Des DemultiplexeursSaid EchPas encore d'évaluation

- TD N3 VHDLDocument20 pagesTD N3 VHDLHanane AIT SAIDPas encore d'évaluation

- VHDLDocument45 pagesVHDLAmineMohamed100% (1)

- Examens Conception NumériqueDocument45 pagesExamens Conception NumériqueBELKACEMPas encore d'évaluation

- TD1 VHDLLDocument5 pagesTD1 VHDLLMontaha Ben SalemPas encore d'évaluation

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihPas encore d'évaluation

- TD BlocDocument3 pagesTD BlocmeedstartPas encore d'évaluation

- Examen VHDL 2018-19Document2 pagesExamen VHDL 2018-19elhaoudar.nassimaPas encore d'évaluation

- VhdlexDocument10 pagesVhdlexSoukaina NJPas encore d'évaluation

- VHDL ExercicesDocument6 pagesVHDL ExercicesHazem HaPas encore d'évaluation

- TD1 VHDLDocument3 pagesTD1 VHDLbejaoui yosrPas encore d'évaluation

- TD2 VHDL Et Logique ProgrammableDocument17 pagesTD2 VHDL Et Logique ProgrammableKais BahrouniPas encore d'évaluation

- VHDL Travaux2TP20180701ABDEL1Document8 pagesVHDL Travaux2TP20180701ABDEL1Tarek BouazzaPas encore d'évaluation

- SysLog1 06 ConversionCodesTransfertsDonnéesDocument21 pagesSysLog1 06 ConversionCodesTransfertsDonnéesJunior DADJINPas encore d'évaluation

- VHDL Exercices Du CoursDocument16 pagesVHDL Exercices Du CoursNourallah Aouina57% (14)

- Chapitre 4 - Cours - VHDL - SystèmesCombinatoiresSéquentielsDocument30 pagesChapitre 4 - Cours - VHDL - SystèmesCombinatoiresSéquentielsdd dddPas encore d'évaluation

- TD2 VHDLDocument2 pagesTD2 VHDLImen SaidiPas encore d'évaluation

- Exercices SupplDocument2 pagesExercices SupplNa CerPas encore d'évaluation

- Compte Rendu TP1 VHDLDocument8 pagesCompte Rendu TP1 VHDLboussaoud.oualidPas encore d'évaluation

- Cours Codes Convolutifs IC5 - 2023-2024Document36 pagesCours Codes Convolutifs IC5 - 2023-2024Abby AbbyPas encore d'évaluation

- TP Integration Num FPGA V1.7Document22 pagesTP Integration Num FPGA V1.7Ouma ImaaPas encore d'évaluation

- Devoir VHDLDocument3 pagesDevoir VHDLImen SaidiPas encore d'évaluation

- TP Fpga Cyclone2Document3 pagesTP Fpga Cyclone2red-allPas encore d'évaluation

- Analyses VH DDocument10 pagesAnalyses VH DMustapha El IdrissiPas encore d'évaluation

- VHDL - SBIHIDocument19 pagesVHDL - SBIHIaminefoura6Pas encore d'évaluation

- Serie TD2Document6 pagesSerie TD2Sarah NourPas encore d'évaluation

- CF VHDL 2021Document1 pageCF VHDL 2021Ayman LamzouriPas encore d'évaluation

- TP5 Asp GBM3-LMDDocument8 pagesTP5 Asp GBM3-LMDDONIA JBELIPas encore d'évaluation

- TD 4Document4 pagesTD 4Mohammed BabaPas encore d'évaluation

- Chap5 VHDL UnlockedDocument21 pagesChap5 VHDL UnlockedilyPas encore d'évaluation

- Rapport de TP en VHDL Xilinx PDFDocument9 pagesRapport de TP en VHDL Xilinx PDFWalid AmriPas encore d'évaluation

- Licence SRT VHDLDocument38 pagesLicence SRT VHDLsanokho ndiayePas encore d'évaluation

- Controle 2018Document3 pagesControle 2018elhaoudar.nassimaPas encore d'évaluation

- TD VHDL 1Document5 pagesTD VHDL 1Zakaria ZinePas encore d'évaluation

- TD1 VHDL GM2 22-23Document2 pagesTD1 VHDL GM2 22-23mariam.ouaaabedPas encore d'évaluation

- Réaliser Par:: Mini-Projet 1Document32 pagesRéaliser Par:: Mini-Projet 1Chahla EssounniPas encore d'évaluation

- Chap3 Circuitscombinatoires M1 2023Document14 pagesChap3 Circuitscombinatoires M1 2023Sãhãzà RandriamaharavoPas encore d'évaluation

- Filière D'Ingénieurs: Systèmes Intelligents Module: Théorie de L'Information Codage Source, Canal Vidéo Et Parole Exercices de TdsDocument6 pagesFilière D'Ingénieurs: Systèmes Intelligents Module: Théorie de L'Information Codage Source, Canal Vidéo Et Parole Exercices de TdsHamza MhalPas encore d'évaluation

- CHAPITRE 4CN (Prof)Document39 pagesCHAPITRE 4CN (Prof)khaoula malehPas encore d'évaluation

- L'Interface Parallele 8255ADocument30 pagesL'Interface Parallele 8255ARima ChemloulPas encore d'évaluation

- TP Decoudeur 4v16Document2 pagesTP Decoudeur 4v16Mahmoud HMILAPas encore d'évaluation

- TP3 Systemes LogiquesDocument2 pagesTP3 Systemes Logiquessoumaya benahmedPas encore d'évaluation

- TP3 Electr NumériqueDocument7 pagesTP3 Electr NumériqueYoucef BoukhalfaPas encore d'évaluation

- SynthDocument16 pagesSynthAZEDDINEPas encore d'évaluation

- Interface MAX7219 Avec Affichage 7 Segments À 8 Chiffres Et PIC16F877ADocument6 pagesInterface MAX7219 Avec Affichage 7 Segments À 8 Chiffres Et PIC16F877Azied houanebPas encore d'évaluation

- Detection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013D'EverandDetection des collisions dans les jeux video 2D: avec C#5, WPF et Visual Studio 2013Pas encore d'évaluation

- 04 Microprocesseur 8086Document21 pages04 Microprocesseur 8086Rafik OuchenePas encore d'évaluation

- Logique Séquentielle: Compteurs Intégrés AsynchronesDocument16 pagesLogique Séquentielle: Compteurs Intégrés AsynchronesbejaouiPas encore d'évaluation

- 07 Analsye de Circuits SequentielsDocument7 pages07 Analsye de Circuits SequentielsABDELAZIZ HAMDAOUIPas encore d'évaluation

- Ch6 Pal FplaDocument33 pagesCh6 Pal FplaAnonymous kIoMGEPas encore d'évaluation

- Cours Up Beguenane 5Document16 pagesCours Up Beguenane 5zied houanebPas encore d'évaluation

- Chapitre 3 - Hiérarchie MémoireDocument61 pagesChapitre 3 - Hiérarchie MémoireidemPas encore d'évaluation

- Chapitre 2 2 Les RegistresDocument5 pagesChapitre 2 2 Les RegistresIddir YuderPas encore d'évaluation

- TD1 ArmDocument4 pagesTD1 Armazza memmiPas encore d'évaluation

- VHDL TP 0506Document5 pagesVHDL TP 0506Haythem ChaouedPas encore d'évaluation

- TD2 - P APIDocument2 pagesTD2 - P APIMohammed ALMUSHIAAPas encore d'évaluation

- Rapport de Mini Projet WordDocument13 pagesRapport de Mini Projet WordHind BahemPas encore d'évaluation

- OutputDocument134 pagesOutputDouar AymenPas encore d'évaluation

- Chapitre1 - Licence MicroprocesseurDocument19 pagesChapitre1 - Licence MicroprocesseurAbdallah RehabPas encore d'évaluation

- Présentation Pfe Principale - PPTX (Autosaved)Document52 pagesPrésentation Pfe Principale - PPTX (Autosaved)Taha Chergui MouanePas encore d'évaluation

- Fonctions Electroniques en CommutationDocument35 pagesFonctions Electroniques en CommutationmaliPas encore d'évaluation

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaPas encore d'évaluation

- Synthèse 1Document10 pagesSynthèse 1Media SharkPas encore d'évaluation

- Série de TD N° 3: Nommez Les Composants D'ordinateur SuivantsDocument4 pagesSérie de TD N° 3: Nommez Les Composants D'ordinateur SuivantsAlaa MessaoudPas encore d'évaluation

- Chapitre2 - Circuits LogiquesDocument18 pagesChapitre2 - Circuits LogiquesMuding BkPas encore d'évaluation

- VHDLDocument121 pagesVHDLRafik OudaoudPas encore d'évaluation

- 2 Serie TravauxDocument4 pages2 Serie TravauxHoussam LhmiriPas encore d'évaluation

- Chapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - CopieDocument18 pagesChapitre 3 Mise en Œuvre Des Microcontrôleurs AVR - Copiejulio KetchaPas encore d'évaluation

- Gel 625 - Cours - VHDL1Document44 pagesGel 625 - Cours - VHDL1Ismael AdjinilePas encore d'évaluation

- GE MP16bDocument98 pagesGE MP16bSafaa BelagounPas encore d'évaluation

- LES CIRCUITS LOGIQUE ProgrammableDocument71 pagesLES CIRCUITS LOGIQUE ProgrammableAhmed DoghmiPas encore d'évaluation

- Chap 3 Les BasculesDocument20 pagesChap 3 Les BasculesAhmed BelhadjPas encore d'évaluation

- Hadj Said DjamelDocument92 pagesHadj Said DjamelSarah MessaouiPas encore d'évaluation

- Microcontrôleurs À Signaux Mixtes MSP430G2553 - TI - DigiKeyDocument4 pagesMicrocontrôleurs À Signaux Mixtes MSP430G2553 - TI - DigiKeynonoPas encore d'évaluation

- Chapitre VI ConceptionDocument17 pagesChapitre VI ConceptionAlouani KacemPas encore d'évaluation