Académique Documents

Professionnel Documents

Culture Documents

Chpitre1 Circuit Combinatoires2

Transféré par

N El kechaiTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Chpitre1 Circuit Combinatoires2

Transféré par

N El kechaiDroits d'auteur :

Formats disponibles

Chapitre1/p2: Circuits combinatoires

Université de Bouira Faculté des sciences

Cours Module Structure Machine

Chapitre1/p2: Circuits combinatoires Filière MI 1ère Année S2

Les circuits combinatoires

Objectifs

• Apprendre la structure de quelques circuits combinatoires souvent utilisés ( demi additionneur ,

additionneur complet,……..).

• Apprendre comment utiliser des circuits combinatoires pour concevoir d’autres circuits plus complexes.

Définition

• Un circuit combinatoire est un circuit numérique dont les

sorties dépendent uniquement des entrées.

• Si=F(Ei)

• Si=F(E1,E2,….,En)

Les circuits combinatoires particuliers

• Multiplexeur

• Demultiplexeur

• Demi Additionneur

• Additionneur complet

• Comparateur

• Encodeur

• Décodeur

• Transcodeur

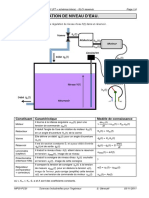

Principe du Multiplexage et Démultiplexage :

Le multiplexage consiste à faire transiter sur une ligne unique des informations Va, Vb, Vc, Vd en

provenance des émetteurs A, B, C et D. La sélection de l'information est faite par des lignes d'adresses (A0 ,

A1 dans l'exemple ci-dessus).

Le démultiplexage est l'opération inverse : les informations en provenance de la ligne de transmission série

sont aiguillées vers l'un des récepteurs (A' , B', C', D') . La sélection du récepteur est faite par des lignes

d'adresse (A0 , A1) via une logique de contrôle (décodage d'adresse)

Fevrier 2014 1/7

Chapitre1/p2: Circuits combinatoires

Multiplexeur

Un multiplexeur (abréviation: MUX) est un circuit permettant de concentrer sur une même voie de

transmission différents types de liaisons (informatique, télécopie, téléphonie, télétex) en sélectionnant une

entrée parmi N. Il possèdera donc N entrées, une seconde entrée de log2 N bits permettant de choisir quelle

entrée sera sélectionnée, et une sortie.

Applications: Il sert d'accès aux réseaux de transmission de données.

Table de vérité Schéma logique d'un multiplexeur

L'entrée A ou B est propagée sur la sortie Z

suivant la valeur de S0.

S0 Z

0 A

1 B

Schéma d'un multiplexeur 4 vers 1 basé sur des portes NON, ET, OU. Le code 10 sélectionne la troisième

entrée (C). Le code 11 aurait sélectionné la dernière entrée (D).

Démultiplexeur

Un démultiplexeur est un circuit combinatoire à N+1 entrées et 2N sorties. N entrées, appelées entrées

d'adressage, permettent d'envoyer sur l'une des sorties la dernière entrée, appelée l'entrée donnée.

Fevrier 2014 2/7

Chapitre1/p2: Circuits combinatoires

Table de Vérité Schéma logique

Table de vérité d'un décodeur 2 vers Ci dessous, un démultiplexeur à 2 entrées et 4 sorties. La

4, les entrées sont C1C0 et les sorties construction (voir les entrées des portes ET) suit la progression

S1, S2, S3, S4. binaire : 00, 01, 10, 11.

Table de vérité

C1 C0 S1 S2 S3 S4

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

Un démultiplexeur de 2 vers 4, montré dans les 4 états possibles

Additionneur

Un additionneur est un circuit logique permettant de réaliser une addition. Ce circuit est très présent dans

les ordinateurs pour le calcul arithmétique mais également pour le calcul d'adresses, d'indice de tableau dans

le processeur.

On dénombre deux types d'additionneurs : parallèle (circuit combinatoire) et série (circuit séquentiel). Dans

la classe des additionneurs parallèles, nous décrirons ici ceux à propagation de retenue et ceux à retenue

anticipée.

Additionneur parallèle

Codée sur un bit, la table de vérité de l'addition est :

A B A + B Retenue

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Remarquons dans le tableau ci-dessus que A+B représente le poids faible tandis que Retenue représente le

poids fort.

Demi-additionneur

À partir de cette table de vérité on peut par exemple construire le circuit suivant, appelé « demi-

additionneur » :

Fevrier 2014 3/7

Chapitre1/p2: Circuits combinatoires

Demi-additionneur (1 bit) où A et B sont les entrées, S la somme A + B et C la retenue.

Additionneur complet

Un additionneur complet nécessite une entrée supplémentaire : une retenue L'intérêt de celle-ci est de

permettre le chaînage des circuits.

A B REntrée S RSortie La table de vérité d'un Le circuit correspondant, l'additionneur complet, est

additionneur complet est composé de deux demi-additionneurs en série

0 0 0 0 0 accompagnés d'une logique pour calculer la retenue

(un OU entre les deux retenues générables par

0 0 1 1 0 chacun des demi-additionneurs) :

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Un additionneur complet 1 bit.

Additionneur parallèle à propagation de retenue

Il est possible de chaîner plusieurs additionneurs un bit pour en fabriquer un capable de traiter des mots de

longueurs arbitraires :

Fevrier 2014 4/7

Chapitre1/p2: Circuits combinatoires

Quatre additionneurs 1 bit chaînés pour former un additionneur 4 bits.

L'inconvénient de ce circuit est sa lenteur car il dépend du temps de propagation de la retenue de module en

module. Cette conception ne peut être choisie pour des circuits dépassant quelques bits, à moins de n'avoir

aucune contrainte de temps : le temps nécessaire pour calculer le résultat augmente linéairement avec la

taille des entrées.

Comparaison binaire

Un comparateur binaire compare deux mots A et B et affecte ses trois sorties en fonction du résultat de la

comparaison.

Si A est strictement supérieur à B, alors la sortie « A>B » passe à 1 (et les deux autres sont mises à zéro)

Si A égal B, alors la sortie « A=B » est mise à 1. De même si A inférieur strict à B, la sortie « A<B » est

mise à 1.

Les entrées de mise en cascade permettent de connecter d’autre comparateurs afin de pouvoir comparer des

mots plus grands (8 bits, 12 bits …). Si elles ne sont pas utilisées, il faut mettre A=B et A>B au niveau 1, et

A<B au niveau 0 pour un fonctionnement correct du comparateur.

Les circuits combinatoires de transcodage

Les circuits combinatoires de transcodage (appelés aussi convertisseurs de code), se répartissent en 3

catégories. Tous ces circuits logiques transforment une information présente à leurs entrées sous une forme

donnée (code 1) en la même information présente à leurs sorties sous une forme différente (code 2). On

appelle :

Fevrier 2014 5/7

Chapitre1/p2: Circuits combinatoires

• CODEUR un circuit à 2n entrées et n sorties

• DECODEUR un circuit à n entrées et 2n sorties dont une seule est validée à la fois

• TRANSCODEUR tout autre circuit convertisseur de code différent des précédents, à p

entrées et à k sorties.

Les Codeurs (Encodeurs)

Un CODEUR est un circuit qui comporte 2n. en entrée et n lignes en sortie. A chaque ligne d'entrée

correspond un code unique en sortie :

Table de vérité du CODEUR ::

ENTREES SORTIES

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 A A1 A0

2

1 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 1 0 0

0 0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 0 1 1 1 1

Les Décodeurs

Un DECODEUR est un circuit qui comporte n lignes d'entrée et .........lignes en sortie. Il sélectionne une

sortie unique en fonction du mot binaire en entrée.

Table de vérité du DECODEUR

ENTREES SORTIES

A2 A1 A0 Y Y1 Y2 Y3 Y4 Y5 Y6 Y7

0

0 0 0 1 0 0 0 0 0 0 0

0 0 1 0 1 0 0 0 0 0 0

0 1 0 0 0 1 0 0 0 0 0

0 1 1 0 0 0 1 0 0 0 0

1 0 0 0 0 0 0 1 0 0 0

1 0 1 0 0 0 0 0 1 0 0

1 1 0 0 0 0 0 0 0 1 0

1 1 1 0 0 0 0 0 0 0 1

Les transcodeurs

Un transcodeur (ou convertisseur de codes) est un dispositif permettant de passer du nombre N écrit dans le

code C1 au même nombre N écrit dans le code C2.

Il n'existe pas un code binaire meilleur que tous les autres : aussi en utilise-t-on plusieurs avec des

transcodeurs pour passer de l'un à l'autre. Leurs utilisations en nombres relativement limités expliquent qu'on

Fevrier 2014 6/7

Chapitre1/p2: Circuits combinatoires

ne les trouve pas tous sous forme de circuits intégrés : il faut alors les réaliser à l'aide de portes logiques ET-

NON , OU-NON ... etc. Comme nous l’avons vu dans le paragraphe II, la réalisation pratique d’un

transcodeur passe par l’écriture de sa table de vérité, puis par la recherche des équations de sorties avec les

tableaux de Karnaugh.

Parmi les transcodeurs on peut citer :

• les transcodeurs décimal / BCD

• les transcodeurs BCD / décimal

• les transcodeurs XS 3 / décimal

• les transcodeurs Gray excédant 3

• les transcodeurs DCB / afficheur 7 segments

• les transcodeurs binaire 5 bits / DCB

• les transcodeurs DCB / binaire 5 bits

Dans la désignation d’un transcodeur, le code « décimal » signifie une seule entrée (ou sortie) active à la fois

parmi 10.

Symbole du transcodeur BCD / XS 3 :

E 0 (LSB) S 0 (LSB)

Même

Chiffre entre 0 E1 S1

Transcodeur chiffre codé en

et 9 codé en E2 S2

BCD / XS 3 code à excès

BCD E 3 (MSB) S 3 (MSB)

de trois

Fevrier 2014 7/7

Vous aimerez peut-être aussi

- Compte Rendu TP1 AutomatismeDocument19 pagesCompte Rendu TP1 AutomatismeGOUAL Sara100% (3)

- Rapport de Stage À MajorelleDocument71 pagesRapport de Stage À MajorelleWissal SakhiPas encore d'évaluation

- TP LcsDocument10 pagesTP LcsBelarbi Issam100% (2)

- TD ArchitectureDocument2 pagesTD ArchitectureYassine EdahbiPas encore d'évaluation

- Exercice TypesDocument14 pagesExercice Typesimed4everPas encore d'évaluation

- Chap5-Circuits de Decodage Et de MultiplexageDocument6 pagesChap5-Circuits de Decodage Et de MultiplexageAhmed GourinePas encore d'évaluation

- Circuits Logiques - 20Document13 pagesCircuits Logiques - 20Omar OdgPas encore d'évaluation

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble Puteur100% (1)

- CHAPITRE I Circuits Logiq Combinatoires PDFDocument28 pagesCHAPITRE I Circuits Logiq Combinatoires PDFTimble PuteurPas encore d'évaluation

- Electronique Numerique Logique CombDocument24 pagesElectronique Numerique Logique CombKhalid SalmiPas encore d'évaluation

- Chapitre V CombinatoireDocument18 pagesChapitre V CombinatoireOussama ElkaissiPas encore d'évaluation

- TP Log 02.5Document9 pagesTP Log 02.5abdoumoumena02Pas encore d'évaluation

- Électronique NumeriqueDocument152 pagesÉlectronique NumeriqueSîdïMôhâmèdBënPas encore d'évaluation

- TP 04 Logique CombinatoireDocument6 pagesTP 04 Logique CombinatoireNardjes BenPas encore d'évaluation

- Chapitre 3Document15 pagesChapitre 3amenmhedhbiiPas encore d'évaluation

- Chapitre 3 Circuits Logiques CombinatoiresDocument23 pagesChapitre 3 Circuits Logiques CombinatoiressoukainaPas encore d'évaluation

- Les Circuits Logiques Combinatoires 1. Objectifs:: 2.1.2 L'Additionneur Complet (2bits)Document14 pagesLes Circuits Logiques Combinatoires 1. Objectifs:: 2.1.2 L'Additionneur Complet (2bits)Asma Hedfi TakrouniPas encore d'évaluation

- Les Circuits Logiques CombinatoiresDocument10 pagesLes Circuits Logiques Combinatoiresmouheb selmiPas encore d'évaluation

- CHAPITRE 4CN (Prof)Document39 pagesCHAPITRE 4CN (Prof)khaoula malehPas encore d'évaluation

- Cours Architecture Ordinateurs Chapitre5Document20 pagesCours Architecture Ordinateurs Chapitre5Will AzanguePas encore d'évaluation

- Conception Des Circuits Logiques CombinatoiresDocument23 pagesConception Des Circuits Logiques CombinatoiresNGOUNE86% (7)

- Architecture Des Ordinateurs TD1 - Portes Logiques Et Premiers CircuitsDocument13 pagesArchitecture Des Ordinateurs TD1 - Portes Logiques Et Premiers Circuitswafa wafaPas encore d'évaluation

- Document Sans TitreDocument10 pagesDocument Sans TitrealicherifbouzaidaPas encore d'évaluation

- Cours - S1 - EI - LogiqueCombinatoire - Chapitre IIIDocument10 pagesCours - S1 - EI - LogiqueCombinatoire - Chapitre IIIoudjouadjPas encore d'évaluation

- tp2 VHDLDocument7 pagestp2 VHDLabdousewagerPas encore d'évaluation

- Logique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Document37 pagesLogique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Soufiane El AoufiPas encore d'évaluation

- Chapitre 4 Logique Combinatoire Partie 2Document17 pagesChapitre 4 Logique Combinatoire Partie 2Fahmawi HakimPas encore d'évaluation

- AB Cours Automatisme Chap 2 Et 3Document17 pagesAB Cours Automatisme Chap 2 Et 3MhB SaAdPas encore d'évaluation

- TD 3.logique Combinatoire - BéjaiaDocument4 pagesTD 3.logique Combinatoire - BéjaiabigPas encore d'évaluation

- Logique Combinatoire PDFDocument7 pagesLogique Combinatoire PDFAmatou ArrahmenPas encore d'évaluation

- Travaux Pratiques Electronique NumériqueDocument10 pagesTravaux Pratiques Electronique NumériqueOumaima RhayaPas encore d'évaluation

- 3-Electronique Numerique - Les Circuits CombinatoiresDocument20 pages3-Electronique Numerique - Les Circuits Combinatoiresziko9172Pas encore d'évaluation

- 01 - Logique CombinatoireDocument34 pages01 - Logique CombinatoireouissemPas encore d'évaluation

- Correction 10Document8 pagesCorrection 10ayoub2704Pas encore d'évaluation

- Archi td5Document2 pagesArchi td5Saad AudiPas encore d'évaluation

- Portes Log I QuesDocument7 pagesPortes Log I QuesGerard MarcelPas encore d'évaluation

- NL CM9 PDFDocument11 pagesNL CM9 PDFCesar MalkiPas encore d'évaluation

- Algèbre Et Logique CombinatoireDocument34 pagesAlgèbre Et Logique CombinatoireNihal DakkounePas encore d'évaluation

- Corrig TD1 2Document5 pagesCorrig TD1 2Amine Aissaoui100% (1)

- Chapitre 3 - Circuits Logiques CombinatoiresDocument10 pagesChapitre 3 - Circuits Logiques CombinatoiresDouaa GhazouaniPas encore d'évaluation

- CHapitre 4Document11 pagesCHapitre 4RABAB MASDOURPas encore d'évaluation

- Logique CombinatoireDocument11 pagesLogique CombinatoireNejib JallouliPas encore d'évaluation

- Corrige TD04Document7 pagesCorrige TD04Hicham WaynePas encore d'évaluation

- Cours 1 Architectures Des CalculateursDocument12 pagesCours 1 Architectures Des CalculateursmezghaniPas encore d'évaluation

- Annoukhaili AmlalDocument10 pagesAnnoukhaili AmlalAmine MalihPas encore d'évaluation

- Chapitre3 PDFDocument44 pagesChapitre3 PDFYasmine GuerbaiPas encore d'évaluation

- Cours Syst Logiques ISET Chap4Document9 pagesCours Syst Logiques ISET Chap4Mahdi JouiniPas encore d'évaluation

- Cours Systèmes Logiques 2020Document32 pagesCours Systèmes Logiques 2020ferielPas encore d'évaluation

- CH3 Convertisseur AnalogiqueDocument12 pagesCH3 Convertisseur AnalogiqueMohammed AbdiPas encore d'évaluation

- Polycopié - TP-Elect - SMP - S6-2023-2024Document25 pagesPolycopié - TP-Elect - SMP - S6-2023-2024azizaziz21212121212121Pas encore d'évaluation

- MicrpDocument4 pagesMicrpRiadh CrbPas encore d'évaluation

- Chap 4 Synthèse Des Circuits CombinDocument12 pagesChap 4 Synthèse Des Circuits CombinAyoub FakihiPas encore d'évaluation

- Systemes Logiques Chapitre5Document5 pagesSystemes Logiques Chapitre5OussamaHePas encore d'évaluation

- Leçon A23-Circuits Combinatoires 2016Document7 pagesLeçon A23-Circuits Combinatoires 2016Aissa IsmailPas encore d'évaluation

- CIRCUIT ELECTRONIQUE 1ère F3 PDFDocument88 pagesCIRCUIT ELECTRONIQUE 1ère F3 PDFanita89% (27)

- Circuit Logiques CombinatoiresDocument28 pagesCircuit Logiques CombinatoiresBăýŕęm Bęn100% (1)

- Electronique NumeriqueDocument20 pagesElectronique NumeriqueMycompte HukkersPas encore d'évaluation

- Chapitre 3 Logiques CombinatoiresDocument20 pagesChapitre 3 Logiques Combinatoireslilian camillePas encore d'évaluation

- A propos du Digital!: Le digital pour tous! Le numérique en questions/réponses pour le modélisme ferroviaireD'EverandA propos du Digital!: Le digital pour tous! Le numérique en questions/réponses pour le modélisme ferroviaireÉvaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Interpolation bilinéaire: Amélioration de la résolution et de la clarté de l'image grâce à l'interpolation bilinéaireD'EverandInterpolation bilinéaire: Amélioration de la résolution et de la clarté de l'image grâce à l'interpolation bilinéairePas encore d'évaluation

- La Memeoire CentraleDocument14 pagesLa Memeoire CentraleN El kechaiPas encore d'évaluation

- Intro Archi2Document74 pagesIntro Archi2N El kechaiPas encore d'évaluation

- CH MemoiresDocument71 pagesCH MemoiresN El kechaiPas encore d'évaluation

- Presentation InformationDocument6 pagesPresentation InformationN El kechaiPas encore d'évaluation

- Esi1an Lessons Archi-Vue Ensemble Oridnateur SmahatDocument25 pagesEsi1an Lessons Archi-Vue Ensemble Oridnateur SmahatN El kechaiPas encore d'évaluation

- Esi Historique OrdinateurDocument60 pagesEsi Historique OrdinateurN El kechaiPas encore d'évaluation

- Esi1an Lessons Archi-Algebre Boole SmahatDocument37 pagesEsi1an Lessons Archi-Algebre Boole SmahatN El kechaiPas encore d'évaluation

- Formulaire Ok Demarrage InjectionDocument1 pageFormulaire Ok Demarrage Injectiongiordano100% (3)

- TD 04 - Représentation Des SLCI (FT + Schémas Blocs) - SLCI AsservisDocument4 pagesTD 04 - Représentation Des SLCI (FT + Schémas Blocs) - SLCI AsservisMohamed AbaakilPas encore d'évaluation

- Chariots Elevateurs en Porte A FauxDocument6 pagesChariots Elevateurs en Porte A FauxAZIPas encore d'évaluation

- Publication 39Document1 pagePublication 39zanazePas encore d'évaluation

- Exercice ERP - 2020Document3 pagesExercice ERP - 2020Mariane LinganiPas encore d'évaluation

- 8.2.1.4 Packet Tracer - Designing and Implementing A VLSM Addressing SchemeDocument4 pages8.2.1.4 Packet Tracer - Designing and Implementing A VLSM Addressing SchemeHichemHichemPas encore d'évaluation

- Presentation Du Projet: BTS - Session 2021Document4 pagesPresentation Du Projet: BTS - Session 2021Loan BéchuPas encore d'évaluation

- Présentation D'une Boutique de Quartier Au Cameroun Dans La Ville de YaoundéDocument22 pagesPrésentation D'une Boutique de Quartier Au Cameroun Dans La Ville de YaoundéGabriel MonsieurPas encore d'évaluation

- Chap3 - Composants Et Indicateurs de La SDF (Partie2 - Maintenabilité-Disponibilité)Document22 pagesChap3 - Composants Et Indicateurs de La SDF (Partie2 - Maintenabilité-Disponibilité)BOUDOUNIT YounesPas encore d'évaluation

- Série 01Document1 pageSérie 01bousbia laiche HacenePas encore d'évaluation

- Cinematique Graphique CorrigeDocument11 pagesCinematique Graphique Corrigemoez.abdenadherPas encore d'évaluation

- Plaquette AWF FRDocument12 pagesPlaquette AWF FRValentin DelahaysPas encore d'évaluation

- Projet Professionnel: Intégrer Un Master 1 en Information CommunicationDocument2 pagesProjet Professionnel: Intégrer Un Master 1 en Information CommunicationPrudence SALANONPas encore d'évaluation

- La Maintenance de La Station de Pompage N°3Document2 pagesLa Maintenance de La Station de Pompage N°3Benziane LarbiPas encore d'évaluation

- Solution Menke Et SteingassDocument3 pagesSolution Menke Et Steingassjabri jihénePas encore d'évaluation

- Montage Et Dimensionnement Des Projets en Energies RenouvelablesDocument6 pagesMontage Et Dimensionnement Des Projets en Energies Renouvelablessatar AmranePas encore d'évaluation

- Guide Installation Antenne Parabole 8 2018Document7 pagesGuide Installation Antenne Parabole 8 2018medPas encore d'évaluation

- Etapes de La Démarche Générale D'auditDocument13 pagesEtapes de La Démarche Générale D'auditEmin AlewiPas encore d'évaluation

- Manuel FormateurDocument14 pagesManuel FormateurSoumia ElhaddPas encore d'évaluation

- Etat AvancementDocument21 pagesEtat Avancementhouda amzinePas encore d'évaluation

- Chapitre IV Commande Numérique Des Systèmes DiscretsDocument20 pagesChapitre IV Commande Numérique Des Systèmes Discretscours important100% (2)

- Echantillange - SupcomDocument30 pagesEchantillange - SupcomFiras KACHROUDIPas encore d'évaluation

- Les Consoles de Mixage V2Document5 pagesLes Consoles de Mixage V2Matilda MacPhersonPas encore d'évaluation

- Standardisation Des AMDEC Proc - BABASSI Akram - 3013Document3 pagesStandardisation Des AMDEC Proc - BABASSI Akram - 3013ETTIEN AFFRO SIM2ON100% (1)

- Rapport de PFE-version FinaleDocument83 pagesRapport de PFE-version FinaleHAMZA YAICH100% (1)

- Les RésistancesDocument17 pagesLes RésistancesHamami AymenPas encore d'évaluation

- Les MatérielsDocument6 pagesLes MatérielsArbia BsiliPas encore d'évaluation

- Chef Chaine 4Document3 pagesChef Chaine 4zaydPas encore d'évaluation