Académique Documents

Professionnel Documents

Culture Documents

Cours Assembleur

Transféré par

MAGNANGOUCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cours Assembleur

Transféré par

MAGNANGOUDroits d'auteur :

Formats disponibles

PROGRAMMATION EN ASSEMBLEUR

DR KODJO Mawugno Rigobert Page 1

Programmation en Assembleur

SOMMAIRE

I – LE COMPOSANT MICROPROCESSEUR......................................................................... 3

II – L’ENVIRONNEMENT MINIMAL (Fig.1) ........................................................................ 3

III – FONCTIONS ..................................................................................................................... 5

1 Le microprocesseur : ................................................................................................... 5

2- Unité de traitement ................................................................................................... 6

IV - STRUCTURE LOGICIELLE ...................................................................................... 7

1- Généralités ............................................................................................................... 7

2 Données de logiciel ..................................................................................................... 8

3 Jeu d’instructions ......................................................................................................... 8

4- Gestion de la pile (SP) ........................................................................................... 11

5- Mode d’adressage .................................................................................................. 11

6- Comportement des indicateurs d’état ..................................................................... 14

7 Traitement des interruptions ...................................................................................... 16

V – L’INTERFACES (PIA) ..................................................................................................... 17

1- Nombre d’interfaces nécessaires ............................................................................ 17

2- Conditionnement des ports du PIA ........................................................................ 17

3- Programmation des ports ....................................................................................... 17

DR KODJO Mawugno Rigobert Page 2

Programmation en Assembleur

I – LE COMPOSANT MICROPROCESSEUR

Le microprocesseur est un circuit intégré (CI) Complexe caractérisé par une haute intégration et

doté des facultés fonctionnelles d’interprétation et d’exécution des instructions d’un programme

comme dans tout circuit intégré, la technologie de fabrication impose au microprocesseur des

caractéristiques :

- de temps de réponse qui se traduit par une plus ou moins grande vitesse d’exécution des

instructions du programme (en nano-seconde)

- et de consommation énergétique (0,5 W pour Intel 8086, Motorola 6802, Zilog Z80, Russe

KP OIK80)

- leur capacité de traitement : format du mot qui peut être traité (4 bits, 8 bits, 16 bits)

- leur organisation logicielle qui est l’ensemble des possibilités d’exploitation et de

programmation offerte au concepteur de système à partir de leur architecture matérielle. (un

ou deux registres d’index ; un ou deux registres accumulateur ; avec ou sans registres

auxiliaires)

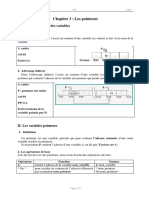

II – L’ENVIRONNEMENT MINIMAL (Fig.1)

Le microprocesseur ne peut fonctionner sans un environnement minimal comportant :

- une zone de mémoire vive pour les données et les résultats ;

- une zone de mémoire morte pour l’aptitude du processeur ;

- une ou plusieurs interfaces pour les périphériques.

Chaque système comprend :

- un bus de données : (Data bus) bidirectionnel qui assure le transfert des informations entre

le microprocesseur et son environnement et inversement. Son nombre de lignes est égal à

la capacité de traitement du microprocesseur

- un bus des adresses : (Adress bus) unidirectionnel qui permet la sélection des informations

à traiter dans un espace mémoire qui peut avoir 2n emplacements, avec n égale au nombre

de conducteurs du bus des adresses

- un bus de commande : (Control bus), constitué par quelques conducteurs qui assurent la

synchronisation des flux d’information sur les bus des données et des adresses.

Sur les deux premiers bus la transmission de l’information s’effectue en mode parallèle.

DR KODJO Mawugno Rigobert Page 3

Programmation en Assembleur

Fig. 1 : Environnement minimal d’un microprocesseur

DR KODJO Mawugno Rigobert Page 4

Programmation en Assembleur

III – FONCTIONS

1 Le microprocesseur: la partie commande

- organise l’encadrement des tâches précisés dans la mémoire programme (ROM)

*soit par une exploitation séquentielle des instructions situées aux adresses

successives de la mémoire

*soit avec des ruptures de séquence en fonction des sauts programmés

- rythme de l’exécution de ces tâches

- analyse le contenu du programme, sélectionne, gère et commande les circuits nécessaires

à l’exécution de chaque tâche

- prend en compte les interventions et les données extérieures en provenance de l’opérateur,

ou générées par les capteurs de la partie opérative.

COMPTEUR ORDINAL ou COMPTEUR PROGRAMME (PC : Programm Counter) : il est

constitué par un registre dont le contenu est initialisé avec l’adresse de la première instruction

du programme.

Dès le lancement du programme ce compteur contient l’adresse de la prochaine instruction à

exécuter :

- soit par INCREMENTATION AUTOMATIQUE dans le cas où les adresses des instructions

se suivent

- soit par CHARGEMENT DE L’ADRESSE DE BRANCHEMENT dans le cas de sauts

programmés

La capacité de ce registre est de 16 bits, son contenu est transféré dans le registre adresses.

REGISTRE D’INSTRUCTION ET DE CODEUR D’INSTRUCTION :

Chacune des instructions à exécuter est rangée dans le REGISTRE D’INSTRUCTION dont le

format est 24 bits (3 octets).

Le premier octet est toujours le code de l’opération que le décodeur d’instruction doit identifier.

Ce décodeur à 8 entrées et 256 (28) sortie qui correspondent chacune à la valeur décimale du

code opération machine exploité par l’unité de commande et de contrôle.

REGISTRE DES ADRESSES : Ce registre de 16 bits est un REGISTRE TAMPON qui assure

l’interfaçage entre le microprocesseur et son environnement. Il conditionne le bus externe des

adresses.

DR KODJO Mawugno Rigobert Page 5

Programmation en Assembleur

REGISTRE DES DONNEES : Ce registre de 8 bits est un REGISTRE TAMPON qui assure

l’interfaçage entre le microprocesseur et son environnement ou inversement. Il conditionne le

bus externe ou le bus interne des données.

BLOC LOGIQUE DE SEQUENCEMENT, DE COMMANDE ET DE CONTRÔLE

Il organise l’exécution des instructions à partir d’un système de microprogrammes. Il associe à

chaque instruction à traiter, un microprogramme.

Cette exécution est séquencée par un oscillateur pilote qui génère un ou deux signaux

d’horloge ou signaux de référence (cas de 6802 de MOTOROLA et du KP50IK83 de RIGA

ELECTRONIC)

POINTEUR DE PILE (PP) ou STACK POINTER (SP) :

C’est un registre compteur de 16 bits qui contient l’adresse du sommet de la pile. La pile est

externe au microprocesseur, c’est une certaine partie de la mémoire RAM utilisée pour

sauvegarder les contenus des différents registres, lors de l’appel à un sous programme ou lors

de la gestion d’une interruption, par exemple : la pile se gère comme un registre à l’empilement

LIFO (Last In – First Out)

REGISTRES AUXILIAIRES OU REGISTRES GENERAUX :

Certains microprocesseurs sont dotés d’un certain nombre de registres « bloc-notes » qui

permettent un stockage temporaire de données.

2- Unité de traitement

Cette partie regroupe les circuits qui assurent les traitements nécessaires à l’exécution des

instructions.

UNITE ARITHMETIQUE ET LOGIQUE (ALU)

C’est un circuit complexe qui assure les fonctions :

- Arithmétique : addition et soustraction

- Logique : ET (AND) ; ou (OR) ; ou exclusif (EXOR)

- comparaison, décalage à droite, décalage à gauche, incrémentation, décrémentation, mise

à un ou à zéro d’un bit, test de bit.

DR KODJO Mawugno Rigobert Page 6

Programmation en Assembleur

Une ALU est constitué par un certain nombre de circuits tels que : Complémentation à deux,

registre à décalage, générateur de parité, portes logiques etc.

ACCUMULATEUR :

Un accumulateur est un REGISTRE DE TRAVAIL de 8 bits qui sert :

- à stocker un opérande au début d’une opération arithmétique et le résultat à la fin de

l’opération ;

- à stocker temporairement des données en provenance de l’extérieur du microprocesseur,

avant leur reprise pour être rangées en mémoire ;

- à stocker des données provenant de la mémoire ou de l’ALU (résultat) pour les présenter

vers l’extérieur du microprocesseur.

On peut disposer de deux accumulateurs sur un microprocesseur (cas du 6802 de

MOTOROLA)

REGISTRE DES INDICATEURS D’ETAT OU REGISTRE DES CODES DE CONDITION :

Les bits de ce registre de 8 bits associé à l’ALU sont à considérer individuellement. Chacun de

ces bits est un indicateur dont l’état dépend du registre et de la dernière opération effectuée.

Dans un programme le résultat du test ou l’état des bits, conditionnent souvent le déroulement

et la suite du programme.

REGISTRE D’INDEX

Le contenu de ce registre de 16 bits est une adresse. Il et utilisé dans le mode d’adressage

indexé.

IV - STRUCTURE LOGICIELLE

1- Généralités

Pour l’utilisateur d’un microprocesseur, la structure logicielle se définit par :

- la nature, le nombre et le format des registres internes qui peuvent être lus et écrits

- la nature des indicateurs d’état associés à l’ALU

DR KODJO Mawugno Rigobert Page 7

Programmation en Assembleur

2 Données de logiciel

La conception et la mise en œuvre des programmes, des procédés et des règles qui permettent

une bonne utilisation d’un microprocesseur nécessitent la connaissance :

- du jeu d’instruction, avec leur expression mnémonique, leur code opération, leur relation

fonctionnelle, …

- des procédures de gestion de la pile,

- des modes d’adressage

- du comportement des indicateurs d’état

- du traitement des interruptions.

Si certaines de ces données sont communes à différentes familles de microprocesseurs,

d’autres sont spécifiques à une seule famille.

3 Jeu d’instructions

FORMAT D’UNE INSTRUCTION

Une instruction se divise en deux parties ou champs. Chacun des champs contient une

information spécifique.

1er champ 2ème champ

CODE OPERATION OPERANDE

__________________________ _____________

1 octet 1 ou 2 octet

L’opérande peut être précisé :

- par sa valeur

- ou par son adresse

CLASSIFICATION FONCTIONNELLE DES PRINCIPALES INSTRUCTIONS

Manipulation de l’information

De mémoire à registre avec des instructions qui se traduisent :

- par le chargement d’un registre avec le contenu d’un emplacement mémoire

qui peut être situé:

Dans une zone mémoire programme ou données :

avec une lecture sur un seul octet

avec une lecture sur deux octets (dans ce cas le registre qui est chargé a

une capacité de 16 bits et doit pouvoir accepter le contenu de deux

DR KODJO Mawugno Rigobert Page 8

Programmation en Assembleur

emplacements mémoire de 8 bits chacun. D’où une relation d’ordre entre les

rangs des adresses et les octets du registre)

Dans la zone mémoire affectée à la pile

De registre à mémoire avec des instructions qui se traduisent :

- par le rangement (ou le stockage) du contenu d’un registre dans un emplacement

mémoire qui peut être situé :

dans une zone mémoire programme ou données

dans une zone mémoire affectée à la pile

De registre à registre

Opérations arithmétiques

Addition et soustraction binaire (ABA, ADD, ADC, SBA, SUB …)

Décalage à droite ou à gauche du contenu d’un accumulateur ou du contenu d’un

emplacement mémoire (ROR, ROL, LSR …)

Incrémentation et décrémentation du contenu d’un accumulateur, d’un emplacement

mémoire, de l’index, du pointeur de pile (DEC, INC, DEX, INX, DES, INS.)*

Comparaison entre le contenu d’un accumulateur ou de l’index et le contenu d’un

emplacement mémoire : (CMP, CPX)

Complémentation à 2 du contenu d’un accumulateur ou contenu d’un emplacement

mémoire (NEG.)

Manipulation de bits du registre des codes de condition

Avec mise à un ou à zéro des bits :

- C (Carry – retenue)

- V (Overflow – dépassement – complément à deux)

- Z (Zero)

- N (Negative – bit de signe)

- I (Interrupt-mask, masque d’interruption)

- H (Half-carry – demi retenue)

Branchements et sauts

- Branchements conditionnels :

Ces branchements dépendent d’une condition, état 0 ou 1, d’un indicateur d’état ou d’une

expression booléenne où plusieurs indicateurs d’état sont associés.

Si la condition est remplie le programme se poursuit à l’adresse de branchement

déterminée par l’instruction.

DR KODJO Mawugno Rigobert Page 9

Programmation en Assembleur

Si la condition n’est pas remplie, le programme se poursuit en séquence et traite l’instruction

qui suit celle du branchement

Instruction de branchement suivant l’état d’un des bits Z, C, V et N

BNE pour Z = 0 BEQ pour Z = 1

BCC pour C = 0 BCS pour C = 1

BVC pour V = 0 BVS pour V = 1

BPL pour N = 0 BMI pour N = 1

Instructions de branchement après comparaison du contenu d’un accumulateur (ACCX) et

le contenu d’un emplacement mémoire (M) :

*Les deux contenus sont des nombres non signés :

BEQ si (ACCX) = (M) BNE si (ACCX) ≠ (M)

BLS si (ACCX) ≤ (M) BHI si (ACCX) > (M)

BCS si (ACCX) < (M) BCC si (ACCX) ≥ (M)

*les deux contenus sont des nombres signés et exprimés en complément à 2 s’ils sont

négatifs.

BEQ si (ACCX) = (M) BNE si (ACCX) ≠ (M)

BLE si (ACCX) ≤ (M) BGT si (ACCX) > (M)

BLT si (ACCX) < (M) BGE si (ACCX) ≥ (M)

- sauts et branchements inconditionnels

*à l’intérieur d’un même programme

JMP : avec un adressage direct étendu ou indexé

BRA : avec un adressage relatif

*du programme principal à un sous-programme :

JSR : avec un adressage direct étendu ou indexé

BSR : avec un adressage relatif

*d’un sous programme d’interruption au programme principal

RTI : qui est la dernière instruction du programme

*d’un sous programme au programme principal

RTS : qui est la dernière instruction du sous programme

Instructions spéciales

Elles contrôlent, par exemple, le déroulement du programme :

WAI : interrompt le déroulement du programme jusqu’à l’arrivée d’une demande

d’interruption

DR KODJO Mawugno Rigobert Page 10

Programmation en Assembleur

SWI : interrompt le déroulement d’un programme avec la sauvegarde de l’ensemble des

contenus des registres

NOP : permet l’incrémentation du compteur programme.

4- Gestion de la pile (SP)

La gestion de cette partie de mémoire externe commence toujours par l’initialisation du registre

pointeur de pile avec une adresse prédéterminée.

Toutes les interruptions et toutes les instructions de branchement inconditionnel imposent la

sauvegarde des contenus de l’ensemble des registres ou uniquement du compteur programme.

Le registre pointeur de pile (SP) contient toujours l’adresse du sommet de la pile c’est-à-dire

l’adresse de l’emplacement mémoire où l’on peut écrire. A chaque écriture dans la pile le

contenu de SP est décrémenté (-1) et à chaque lecture il est incrémenté (+1)

5- Mode d’adressage

L’adressage est la technique par laquelle est définie, l’adresse d’origine ou de destination d’une

donnée.

Au niveau d’une instruction dont le premier octet est toujours le code opération, le mode

d’adressage caractérise la façon dont est obtenu l’opérande.

ADRESSAGE IMPLICITE ET ADRESSAGE INHERENT :

Le code opération de l’instruction renferme implicitement le ou les opérandes.

L’instruction ne comporte qu’un seul octet, le code opération

Exemple : CLRA qui consiste à mettre à zéro le contenu de l’accumulateur A pour le

microprocesseur 6802 MOTOROLA

Instructions : Code opération Soit 4F

ADRESSAGE IMMEDIAT :

Au premier octet de l’instruction qui correspond au code opération, est immédiatement associée

la valeur de l’opérande

DR KODJO Mawugno Rigobert Page 11

Programmation en Assembleur

Exemples :

- LDAA # $ 1B qui consiste à charger l’accumulateur A en mode immédiat (#) avec la valeur

hexadécimal ($), 1B, qui se traduit par l’instruction :

Code opération opérande soit 86 1B

- LDS # $ E120 qui consiste à charger le pointeur de pile en mode immédiat, avec l’adresse

hexadécimal E120 qui se traduit par l’instruction :

Code opération opérande soit 8E E1 20

Ce mode d’adressage est intéressant pour initialiser un registre.

ADRESSAGE DIRECT OU ABSOLU

C’est le mode le plus simple pour rechercher une donnée en désignant l’adresse de son

emplacement mémoire :

Expression générale de l’instruction :

Code opération Adresse

- Si l’adresse nécessite une écriture sur deux octets : l’adressage est direct étendu

Exemple :

LDAA $ E480 qui consiste à charger l’accumulateur A avec le contenu de l’adressage

E480 ce qui se traduit par l’instruction :

B6 E4 80 écrite sur trois octets.

- Si l’adresse peut s’écrire sur un seul octet : l’adressage est direct ou dit de page zéro

Exemple

LDAA $ 3F qui consiste à charger l’accumulateur A avec le contenu de l’adresse 3F qui se

traduit par l’instruction :

96 3F écrite sur deux octets

Ce dernier mode d’adressage confère une grande rapidité à l’exécution de l’instruction

DR KODJO Mawugno Rigobert Page 12

Programmation en Assembleur

ADRESSAGE RELATIF

Ce mode d’adressage s’applique aux instructions de branchement. Cette adresse de

branchement n’est pas exprimée en valeur absolue mais en valeur relative par rapport au

contenu du compteur programme, au moment de l’exécution de l’instruction.

Le déplacement associe au code opération est écrit sur un octet. Il peut être positif ou négatif et

compris entre -128 et +127 en valeur décimale pour un microprocesseur de 16 bits. Dans un

octet signé le bit 7 est le bit de signe.

Pour 0 : le nombre est positif

Pour 1 : le nombre est négatif

et les bits 0 à 6 sont les bits de valeur absolue

Instruction : Code opération déplacement écrite sur 2 octets

ADRESSAGE INDEXE

Dans ce mode d’adressage, l’adresse absolue de l’opérande est donnée par la somme :

- du déplacement (offset) associé au code opération

- et du contenu du registre d’index

Ce mode d’adressage est très intéressant pour adresser, l’un après l’autre des emplacements

mémoires adjacents (cas des tables de données) avec les instructions d’incrémentation et

décrémentation de l’index.

Instruction : code opération Déplacement écrite sur 2 octets

Exemple : chargement de l’accumulateur A en mode indexé, l’instruction serait : LDAA $ 05, X

et est traduite par :

A6 05

DR KODJO Mawugno Rigobert Page 13

Programmation en Assembleur

6- Comportement des indicateurs d’état

ORGANSIATION DU REGISTRE DES CODES CONDITION

1 1 H I N Z V C

Seules les instructions suivantes n’ont aucune influence sur un ou plusieurs des bits indicateurs

d’état :

- instruction sur la pile

- instruction de sauts et de branchements

- instruction spéciales

INDICATEUR DE RETENUE OU DE REPORT (Carry – C)

- Cas d’une addition de nombre non signés

Décimal Binaire Hexadécimal

33 00100001 21

+ 67 c + 01000011 + 43

100 0 1100100 64

C = 0 pas de report, le résultat binaire sur 8 bits est bon

208 11010000 D0

+ 67 c + 01000011 + 43

275 1 00010011 113

C = 1 : existence d’un report, le résultat binaire sur 8 bits est mauvais, l’indicateur C prend l’état

1 dès la création de la retenue.

- Test d’un bit

*b7 du contenu d’un accumulateur ou d’un emplacement mémoire par l’instruction ASL pour

6802 MOTOROLA

*b0 du contenu d’un accumulateur ou d’un emplacement mémoire par l’instruction ASR

*ou d’un bit du registre codes condition après avoir transféré son contenu dans

l’accumulateur A par TPA.

DR KODJO Mawugno Rigobert Page 14

Programmation en Assembleur

INDICATEUR DE ZERO Z

Il prend la valeur :

1 : si le résultat d’une opération est nul

0 : dans tous les autres cas

Cet indicateur est intéressant :

- Dans le cas de la comparaison de deux nombres N1 et N2 qui s’opère par

soustraction N1 – N2

si N1 = N2, l’indicateur Z = 1

si N1 ≠ N2, l’indicateur Z = 0

- Dans un test de fin de structure répétitive où la condition de répétition est exprimée

par rapport à la valeur nulle d’une variable ; lorsque cette valeur est atteinte, Z = 1 le

programme se poursuit.

INDICATEUR NEGATIF OU INDICATEUR DE SIGNE N (Négative)

Il prend la valeur :

1 : si le résultat d’une opération est négative

0 : si le résultat d’une opération est positif

Dans un nombre signé le bit 7 est le bit de signe :

bit 7 = 1 le nombre est négatif

bit 7 = 0 le nombre est positif

L’indicateur d’état N prend l’état du bit 7 du résultat de l’opération

INDICATEUR DE DEPASSEMENT DE CAPACITE V (overflow)

Cet indicateur est mis à 1 pour tout dépassement de capacité lors des opérations arithmétiques

avec des nombres signés. Ce dépassement entraîne des résultats erronés.

INDICATEUR DE DEMI-RETENUE H (Half-carry)

Cet indicateur est à tester lors d’opérations portant sur des valeurs écrites en décimal codé

binaire (BCD).

Exemple :

- Soit à additionner les valeurs décimales 59 + 38 = 97

- En BCD

DR KODJO Mawugno Rigobert Page 15

Programmation en Assembleur

59 0101 1001

38 0011 1000

____ _________________

97 1001 0001

Le résultat obtenu est : 91 FAUX

L’erreur provient du fait que le microprocesseur propage sur le quartet de poids fort la retenue

de la somme des bits 3.

L’indicateur H prend l’état 1 dès la création de cette retenue intermédiaire.

INDICATEUR DE MASQUE D’INTERRUPTION I (Interrupt Mask)

Cet indicateur prend l’état 1 lorsque survient une interruption non masquable.

Il doit être à l’état zéro pour autoriser une interruption.

7 Traitement des interruptions

Une demande d’interruption se traduit par un signal extérieur au microprocesseur ou par une

instruction logicielle qui interrompt le traitement du programme en cours avec la sauvegarde du

contenu des registres, et affecte le microprocesseur au traitement du programme d’interruption.

Ces interruptions sont classées suivant un ordre de priorité.

Exemple :

SIGNAUX Mise à l’état initial : RESET

Arrêt du microprocesseur : HALT

Priorité décroissante Interruption non masquable : NMI

Demande d’interruption masquable : IRQ

INSTRUCTION Interruption logicielle : SWI

DR KODJO Mawugno Rigobert Page 16

Programmation en Assembleur

V – L’INTERFACES (PIA)

1- Nombre d’interfaces nécessaires

Il dépend uniquement du nombre des entrées et des sorties de l’application considérée.

L’interface ou PIA (Peripheral Interface Adaptor) met à la disposition de l’utilisateur

généralement deux PORTS comportant chacun huit bornes d’entrées/sorties indifférenciées.

Pour un nombre d’entrées/sorties supérieur à 16, le système doit comporter plusieurs PIA et

prévoir leur sélection.

2- Conditionnement des ports du PIA

Pour une application donnée la fonction de chacun des ports du PIA doit être définie de façon

impérative. Ce conditionnement fonctionnel programmable peut se présenter sous une forme.

HOMOGENE : - PORT A conditionné en ENTREE

- PORT B conditionné en SORTIE

MIXTE : -n bits du PORT A conditionnés en ENTREE et les (8-n) autres bits

conditionnés en SORTIE

-PORT B condition en SORTIE

C’est la structure homogène qui est la plus conseillée .

3- Programmation des ports

Le PIA comporte par PORT trois registres distincts :

- le registre de commande : CRA (ou CRB),

- le registre de ses de transfert des données DDRA (ou DDRB),

- le registre de sortie : ORA (ou ORB).

Le registre CR dispose d’une adresse propre, les registres DDR et OR d’une adresse

commune.

DR KODJO Mawugno Rigobert Page 17

Programmation en Assembleur

Programmer le conditionnement d’un PORT consiste à :

- mettre à l’état logique 0 le bit b2 du registre CR ce qui a pour effet de sélectionner le registre

DDR du PORT considéré,

- mettre à l’état logique 0 ou à l’état logique 1 les bits du registre DDR selon que l’on souhaite

les considérer en ENTREE ou en SORTIE.

L’affectation des données se fait suivant la situation de conditionnement.

A chacune des bornes du port d’entrée (bits b0 à b7) peut correspondre un capteur et un seul.

Toute LECTURE du port c’est-à-dire du contenu du registre OR, se traduit par l’envoi sur le bus

des données d’un mot de 1 octet représentatif, à l’instant de la lecture, des états logiques (0 ou

1) de l’ensemble des capteurs.

La procédure de LECTURE consiste à :

- mettre à l’état logique 1 le bit b2 du registre CR, ce qui a pour effet de sélectionner le

registre OR

- acquérir la donnée (1 octet) présente dans le registre OR

L’affectation des données de sortie consiste à faire correspondre à chacune des bornes du

PORT de sortie (bits b0 à b7) une sortie et une seule. Toute ECRITURE dans ce PORT se

traduit par l’envoi sur la périphérique d’un mot de 1 octet représentatif à cet instant, de

l’ensemble des états logiques (0 ou 1) des éléments récepteurs.

La procédure d’ECRITURE quant à elle, consiste à :

- mettre à l’effet logique 1 et le bit b2 du registre CR ce qui a pour effet de sélectionner le

registre OR

- introduire la donnée (1 octet) dans le registre OR

Le contenu du MOT de SORTIE ou MOT d’ECRITURE conditionne l’ensemble des récepteurs

du système : sa valeur reste constante durant le temps qui s’écoule entre deux phases

successives d’écriture.

DR KODJO Mawugno Rigobert Page 18

Programmation en Assembleur

JEU D’INSTRUCTIONS

DR KODJO Mawugno Rigobert Page 19

Programmation en Assembleur

DR KODJO Mawugno Rigobert Page 20

Programmation en Assembleur

DR KODJO Mawugno Rigobert Page 21

Programmation en Assembleur

DR KODJO Mawugno Rigobert Page 22

Programmation en Assembleur

Vous aimerez peut-être aussi

- Compte RENDU InformatiqueindutrielDocument21 pagesCompte RENDU InformatiqueindutrielOUTMANE FERNOUCHPas encore d'évaluation

- Programmation Des MicrocontroleursDocument108 pagesProgrammation Des MicrocontroleursHors ManPas encore d'évaluation

- Traiter 2 SteDocument50 pagesTraiter 2 SteFadwa GHANIPas encore d'évaluation

- ALMODocument91 pagesALMObeckytom75100% (1)

- Exposé Le MicroprocesseurDocument8 pagesExposé Le MicroprocesseurMamadou Seydou Diallo67% (6)

- Cours Projet Electronique 1Document17 pagesCours Projet Electronique 1ryadhPas encore d'évaluation

- Cours 3A DEE MicroControleur PDFDocument21 pagesCours 3A DEE MicroControleur PDFDiavolo Rossonero del Milan100% (1)

- TPDocument32 pagesTPKain Chi BlanPas encore d'évaluation

- Cours PICDocument5 pagesCours PICTouta MedPas encore d'évaluation

- Cours 04Document2 pagesCours 04jaouad_kerPas encore d'évaluation

- Chapitre 1Document16 pagesChapitre 1YOUCEF BOUHARAOUAPas encore d'évaluation

- TP Info IndusDocument26 pagesTP Info IndusAmine MassawiPas encore d'évaluation

- Introduction Aux Systèmes À Base de MicrocontroleursDocument3 pagesIntroduction Aux Systèmes À Base de Microcontroleursdubonson30Pas encore d'évaluation

- Cours Upge s11Document7 pagesCours Upge s11ufkfkf17Pas encore d'évaluation

- Nouveau Présentation Microsoft PowerPointDocument22 pagesNouveau Présentation Microsoft PowerPointmaiz100% (1)

- Chapitre 4 - Architecture Des Systèmes ProgrammésDocument25 pagesChapitre 4 - Architecture Des Systèmes ProgrammésTtech hackPas encore d'évaluation

- DSP Fpga-1Document43 pagesDSP Fpga-1Chochoo BoumzdPas encore d'évaluation

- Chapitre 2-1Document11 pagesChapitre 2-1bouchenebPas encore d'évaluation

- Chapitre 3 - 090738Document11 pagesChapitre 3 - 090738Rãmï RøÿãlPas encore d'évaluation

- Du Microprocesseur À La Carte de Prototypage Partie 1: Microprocesseur Et MicrocontrôleurDocument4 pagesDu Microprocesseur À La Carte de Prototypage Partie 1: Microprocesseur Et MicrocontrôleurBsusnksPas encore d'évaluation

- Chapitre 1Document45 pagesChapitre 1moumnimeryem2002Pas encore d'évaluation

- MODULE N°09 TLC-BTS MicrocontrôleursDocument28 pagesMODULE N°09 TLC-BTS MicrocontrôleursWalid MahmoudPas encore d'évaluation

- Chap 2 Architecture Et Fonctionnement D'un MicroprocesseurDocument12 pagesChap 2 Architecture Et Fonctionnement D'un MicroprocesseurSamen Lempire100% (1)

- MicrocontroleurDocument12 pagesMicrocontroleurGaddour TriguiPas encore d'évaluation

- Chapitre 3 - Le MicroprocesseurDocument26 pagesChapitre 3 - Le Microprocesseurarbaoui1167% (3)

- Cours SM en Ligne-ConvertiDocument72 pagesCours SM en Ligne-ConvertiAnfel CPas encore d'évaluation

- Chapitre V MicroprocesseurDocument10 pagesChapitre V MicroprocesseurMouhamed MoustaphaPas encore d'évaluation

- Chapitre 1: Introduction Aux MicroprocesseursDocument26 pagesChapitre 1: Introduction Aux MicroprocesseursAbir HammamiPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 32Document37 pagesCours Microcontrôleur Microprocesseur 32Frank EffeuzePas encore d'évaluation

- Partie3 Generalites Sur MicroprocesseursDocument13 pagesPartie3 Generalites Sur MicroprocesseursKhadija HtPas encore d'évaluation

- Chapitre 1 Systemes Micro Programmes A Base de Microprocesseur PDFDocument8 pagesChapitre 1 Systemes Micro Programmes A Base de Microprocesseur PDFloïc wankoPas encore d'évaluation

- Les Microcontroleurs Pic16f84Document28 pagesLes Microcontroleurs Pic16f84badreddinePas encore d'évaluation

- PIC LeçonN°1Document16 pagesPIC LeçonN°1Smart ClassePas encore d'évaluation

- Cours Microprocesseur MicroControleur M1 GI Chap 2Document13 pagesCours Microprocesseur MicroControleur M1 GI Chap 2Hassan MohamedPas encore d'évaluation

- Cours-No-03 Calculateur Et InterfaçageDocument11 pagesCours-No-03 Calculateur Et Interfaçagestone freePas encore d'évaluation

- Presentation Du Pic 16f877 PDFDocument22 pagesPresentation Du Pic 16f877 PDFKiadam Kitou100% (1)

- DSP FpgaDocument43 pagesDSP Fpgachiheb clubistePas encore d'évaluation

- Chapitre 2Document13 pagesChapitre 2Mehdi SellamiPas encore d'évaluation

- Systeme MicroDocument25 pagesSysteme MicroHafsa NouichPas encore d'évaluation

- TH6 1 Aid Act2Document4 pagesTH6 1 Aid Act2fadihamdi75Pas encore d'évaluation

- Presentation Du Pic 16f877 PDFDocument22 pagesPresentation Du Pic 16f877 PDFyoussefPas encore d'évaluation

- Compte Rendu Mooc Semaine 2Document4 pagesCompte Rendu Mooc Semaine 2TanankemPas encore d'évaluation

- Chapitre II Architecture Générale D Un MicrocontroleurDocument22 pagesChapitre II Architecture Générale D Un Microcontroleurfou100% (1)

- Cours 1 ASP GBM3-LMDDocument38 pagesCours 1 ASP GBM3-LMDDONIA JBELI100% (1)

- Projet Montre DigitaleDocument27 pagesProjet Montre DigitaleMalika Hamdi100% (1)

- Systèmes Chap 12 Et 3Document10 pagesSystèmes Chap 12 Et 3Antoine LemlinPas encore d'évaluation

- A - Introduction ElectroniqueDesSysEmbarqués PDFDocument59 pagesA - Introduction ElectroniqueDesSysEmbarqués PDFAnas AsranPas encore d'évaluation

- Ec Gim334 - Dao - CaoDocument47 pagesEc Gim334 - Dao - CaoArmand EssPas encore d'évaluation

- Chapitre1 Architecture - Ordinateurs - 2019 - 2020Document13 pagesChapitre1 Architecture - Ordinateurs - 2019 - 2020Bessem BessemPas encore d'évaluation

- Un Microcontrôleur Est Un Circuit Intégré Rassemblant Dans Un Même Boitier Un MicroprocesseurDocument9 pagesUn Microcontrôleur Est Un Circuit Intégré Rassemblant Dans Un Même Boitier Un MicroprocesseuromarPas encore d'évaluation

- Presentation Du Pic 16f877 PDFDocument22 pagesPresentation Du Pic 16f877 PDFhamzalabbou83% (6)

- CHAPITRE 1 - GéneralitésDocument9 pagesCHAPITRE 1 - GéneralitésZERARKA Mohamed FawziPas encore d'évaluation

- Poly - Micro 2023 2024Document56 pagesPoly - Micro 2023 2024kaoutar saadaouiPas encore d'évaluation

- Electronique Numerique ProgrammeeDocument31 pagesElectronique Numerique ProgrammeeAnass KalaliPas encore d'évaluation

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaPas encore d'évaluation

- Introduction à l’analyse des données de sondage avec SPSS : Guide d’auto-apprentissageD'EverandIntroduction à l’analyse des données de sondage avec SPSS : Guide d’auto-apprentissagePas encore d'évaluation

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasD'EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasPas encore d'évaluation

- Les macros avec OpenOffice CALC: La programmation BASIC pour tousD'EverandLes macros avec OpenOffice CALC: La programmation BASIC pour tousPas encore d'évaluation

- Bien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLD'EverandBien débuter avec SQL: Exercices dans l'interface PhpMyAdmin et MySQLPas encore d'évaluation

- Projets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadD'EverandProjets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadPas encore d'évaluation

- Pays: Togo Année: 2016 Session: Sciences Physiques Série: BAC, Série D Durée: 3 H Coefficient: 3Document3 pagesPays: Togo Année: 2016 Session: Sciences Physiques Série: BAC, Série D Durée: 3 H Coefficient: 3MAGNANGOUPas encore d'évaluation

- Epreuve Bac Mathematiques A4 2019, TogoDocument1 pageEpreuve Bac Mathematiques A4 2019, TogoMAGNANGOUPas encore d'évaluation

- Preuve de Physique-Chimie, BAC Série A4, Année 2016, TogoDocument2 pagesPreuve de Physique-Chimie, BAC Série A4, Année 2016, TogoMAGNANGOUPas encore d'évaluation

- Epreuve Bac A4 2020 SVT TogoDocument3 pagesEpreuve Bac A4 2020 SVT TogoMAGNANGOU100% (2)

- Epreuve Bac A4 2020 Mathematiques TogoDocument3 pagesEpreuve Bac A4 2020 Mathematiques TogoMAGNANGOU67% (3)

- Rapport TP Gel208Document4 pagesRapport TP Gel208MAGNANGOUPas encore d'évaluation

- À Première VueDocument3 pagesÀ Première VueMAGNANGOUPas encore d'évaluation

- Les Postes HTA - BTDocument10 pagesLes Postes HTA - BTcherif yahyaoui100% (4)

- TD Systeme 4 BarresDocument3 pagesTD Systeme 4 BarresMAGNANGOUPas encore d'évaluation

- Expose de Adjavon Post... Reseau ElectrDocument15 pagesExpose de Adjavon Post... Reseau ElectrMAGNANGOUPas encore d'évaluation

- Les Logiciels Libres en Documentation 2Document45 pagesLes Logiciels Libres en Documentation 2MAGNANGOUPas encore d'évaluation

- Accumulateur ÉlectriqueDocument10 pagesAccumulateur ÉlectriqueMAGNANGOUPas encore d'évaluation

- Les Logiciels Libres en Documentation 3Document14 pagesLes Logiciels Libres en Documentation 3MAGNANGOUPas encore d'évaluation

- Les Logiciels Libres en Documentation 4Document13 pagesLes Logiciels Libres en Documentation 4MAGNANGOUPas encore d'évaluation

- Les Logiciels Libres en Documentation 5Document16 pagesLes Logiciels Libres en Documentation 5MAGNANGOUPas encore d'évaluation

- Moulin À Vent Servant À (... ) Agence Rol btv1b53143870pDocument3 pagesMoulin À Vent Servant À (... ) Agence Rol btv1b53143870pMAGNANGOUPas encore d'évaluation

- Les Logiciels Libres en DocumentationDocument115 pagesLes Logiciels Libres en DocumentationMAGNANGOUPas encore d'évaluation

- Postes de Transformsations Ds Les Reseaux ElectDocument14 pagesPostes de Transformsations Ds Les Reseaux ElectMAGNANGOUPas encore d'évaluation

- Chapitre 3 Les PointeursDocument8 pagesChapitre 3 Les PointeursYoussef TayechiPas encore d'évaluation

- 2tup 150523190406 Lva1 App6892Document48 pages2tup 150523190406 Lva1 App6892HassaniPas encore d'évaluation

- 04-55-01-0 DD PDFDocument16 pages04-55-01-0 DD PDFPrakash NandiPas encore d'évaluation

- M2i Formation - WMO-PE - WinDev Mobile 26 - 27 - Programmation AvancéeDocument3 pagesM2i Formation - WMO-PE - WinDev Mobile 26 - 27 - Programmation Avancéeceleste mevanzaPas encore d'évaluation

- Bouakaz 02Document14 pagesBouakaz 02Saad TaibiPas encore d'évaluation

- S7 ProgrammerDocument528 pagesS7 ProgrammercoubardPas encore d'évaluation

- TD Interconnexion ReseauxDocument3 pagesTD Interconnexion ReseauxCecile Pouwams100% (1)

- Seance 3 Cours XML Schema Partie 1 2023 2024Document13 pagesSeance 3 Cours XML Schema Partie 1 2023 2024Rouçadi WafaaPas encore d'évaluation

- QCM InformatiqueDocument26 pagesQCM InformatiqueAnass Abbouch83% (6)

- 11-Operateurs, Constance Et AssertionsDocument11 pages11-Operateurs, Constance Et AssertionsFatima ZahraPas encore d'évaluation

- Groupe KAMOTO. BDocument18 pagesGroupe KAMOTO. BDanPas encore d'évaluation

- Algo12 DiopUTDocument136 pagesAlgo12 DiopUTluqman100% (1)

- Inwi Challenge Kit de Compétition 3edDocument13 pagesInwi Challenge Kit de Compétition 3edjalalPas encore d'évaluation

- Examen9 Systèmes A MicroprocesseursDocument8 pagesExamen9 Systèmes A MicroprocesseursMohamed HebchiPas encore d'évaluation

- Déployer Wazuh Dans Une Organisation PubliqueDocument105 pagesDéployer Wazuh Dans Une Organisation Publiqueeric67% (3)

- Manuel BisonDocument2 pagesManuel BisonWiller CostiganPas encore d'évaluation

- Cours Android FSR Ch2 RevisionDocument8 pagesCours Android FSR Ch2 RevisionZahira LabiadPas encore d'évaluation

- Configuration D'Un Vlan Sur Switch CiscoDocument7 pagesConfiguration D'Un Vlan Sur Switch CiscoCharafeddine ELBAHJAPas encore d'évaluation

- Null 3Document29 pagesNull 3Fabrice FotsoPas encore d'évaluation

- Mémoir RFIDDocument68 pagesMémoir RFIDsih emPas encore d'évaluation

- Initiation 2 TIA Portal MS1Document24 pagesInitiation 2 TIA Portal MS1Anbari MehdiPas encore d'évaluation

- Principe de Contrôle DDocument7 pagesPrincipe de Contrôle DyasinPas encore d'évaluation

- GMAO Utilisation Et Developpement A L ECHODocument23 pagesGMAO Utilisation Et Developpement A L ECHOPortugas D-AcePas encore d'évaluation

- Chapitre 1 POO C++Document50 pagesChapitre 1 POO C++BECHIR BAAZIZPas encore d'évaluation

- RFIDDocument10 pagesRFIDTassadit KessiliPas encore d'évaluation

- Depnnage CTPHDocument3 pagesDepnnage CTPHSanon HensoPas encore d'évaluation

- Manuel 2004 HP-t5000 hstnc-001l-tcDocument32 pagesManuel 2004 HP-t5000 hstnc-001l-tctechinfo64Pas encore d'évaluation

- Chap 8 UML Partie 2Document17 pagesChap 8 UML Partie 2ali toumiPas encore d'évaluation

- Manual Modbus MicrologicDocument36 pagesManual Modbus MicrologicEduardo RamosPas encore d'évaluation

- Rapport IndusDocument16 pagesRapport Indusmouaouya boutadghartPas encore d'évaluation