Académique Documents

Professionnel Documents

Culture Documents

FPGA

Transféré par

Elbahaoui AbdelCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

FPGA

Transféré par

Elbahaoui AbdelDroits d'auteur :

Formats disponibles

Circuits

Logiques

Programmables

PLD

PLAN

Circuits numriques

Prsentation de la logique programme

Classification des PLDs

Oprateurs gnriques

Technologies

Les PALs

Les C.P.L.D.s

Les F.P.G.A.s

Dveloppement des CPLDs et FPGAs

Circuits numriques

3

Nous nous intresserons surtout aux circuits architecture programmable

faible temps de dveloppement.

Prsentation de la logique programme

Une fonction logique est dfinie par les interconnexions entre des

oprateurs combinatoires et des bascules, et par les quations des

oprateurs combinatoires. Ce qui est programmable dans un circuit

concerne donc les interconnexions et les oprateurs combinatoires.

4

Donc un circuit programmable est un assemblage doprateurs logiques

combinatoires et de bascules, prsentes physiquement sur le circuit, dans

lequel la fonction ralise nest pas fixe lors de la fabrication.

Classification des PLDs

PAL

GAL Effaable

Electriquement

PAL Effaable

LCA

FPGA

PLD

CPLD

6

P.A.L. signifie Programmable Array Logic, c- -d rseau logique

programmable. La programmation de ces circuits s'effectue par

destruction de fusibles. Une fois programms on ne peut plus les effacer.

Classification des PLDs

On distingue deux sous familles:

Les P.A.L. combinatoires ou P.A.L. simples. Ils sont constitus de

fonctions de logique combinatoire.

Les P.A.L. registres ou F.P.L.S. (Field Programmable Logic

Sequencer) pour squenceur logique programmable. Ils sont constitus

de logique combinatoire et squentielle (Registre).

P.A.L. effaables: E.P.L.D.

Les E.P.L.D. (Erasable Programmable Logic Device), c'est dire circuit

logique programmable et effaable par UV ou lectriquement.

7

Les G.A.L.(Generic Array Logic) ou encore rseau logique gnrique. Le

nom de G.A.L. a t dpos par LATTICE SEMICONDUCTOR. Leur

fonctionnement est identique aux EPLD, ils sont programmables et

effaables lectriquement.

Classification des PLDs

Les C.P.L.D.(Complex Programmable Logic Device). Ces circuits sont

composs de plusieurs P.A.L.s lmentaires relis entre eux par une zone

dinterconnexion.

Grce cette architecture, on peut atteindre des vitesses de fonctionnement

leves (plusieurs centaine de Mhz).

8

Les L.C.A. & F.P.G.A. anti-fusible.

Les L.C.A. (Logic Cell Array) ou encore rseau de cellules logiques.

Ces circuits sont composs de blocs logiques lmentaires de 2000

10000 portes que l'utilisateur peut interconnecter.

Classification des PLDs

Les F.P.G.A. (Field Programmable Gate Array) anti fusibles sont

identiques aux L.C.A sauf qu'ils permettent une plus grande intgration de

portes et ils ne sont pas effaables lectriquement. Le nom anti-fusible vient

de la programmation des connexions qui s'effectue par fermeture de

circuits, compar aux fusibles o l'on ouvre les circuits.

Oprateurs gnriques

1) Rseaux Logique Programmables:

N'importe quelle fonction peut tre code par une somme de produit,

par un produit de somme ou un mlange des deux. On peut

immdiatement en dduire une structure de circuits, appel matrice PLA

(Programmable Logic Array).

La figure suivante reprsente une matrice PLA 4 entres et 4 sorties :

9

10

Le principe de ralisation des fonctions de la matrice ET et de OU est le

suivant :

11

Chaque croix reprsentant une connexion programmable (un fusible par

exemple).

Oprateurs gnriques

a) PAL simple :

La programmation du circuit consiste supprimer certaines des

connexions marques dune croix.

Le schma ci-dessus permet de raliser nimporte quelle fonction

boolenne s(e1,e2), de deux variables binaires e1 et e2, pourvu quelle ne

dpasse pas deux termes.

Structure simplifie dun PAL(2 entres et 1 sortie)

Oprateurs gnriques

b) PAL ralisant un XOR:

Reprsentation de la structure interne de loprateur XOR dun P.A.L.

Les croix reprsentent les fusibles intacts.

Oprateurs gnriques

Le plus simple des PLDs, un 16L8 par exemple, utilise des oprateurs

ET 32 entres et des oprateurs OU 8 entres. Un schma tel que

celui des figures prcdentes deviendrait illisible.

Pour viter cet cueil, les notices de circuits utilisent des symboles

simplifis, pour reprsenter les rseaux logiques programmables:

14

symbole d'un PLA 24

Oprateurs gnriques

Le schma de loprateur ou exclusif devient:

15

Oprateurs gnriques

2) Multiplexeurs:

16

Le multiplexeur permet galement de coder une fonction combinatoire,

comme le montre la figure suivante :

Multiplexeur lmentaire

Oprateurs gnriques

On peut dcrire la fonction XOR sous forme algorithmique :

17

ou exclusif ralis par un multiplexeur

Donc un multiplexeur est un oprateur gnrique.

Exemple: Un multiplexeur n entres de slection, soit 2

n

entres de donnes, permet

de raliser nimporte quelle fonction combinatoire de n + 1 entres.

Oprateurs gnriques

3) Porte XOR:

La reprsentation des fonctions combinatoires : additions et soustractions,

contrles derreurs, cryptages, etc se prtent mal en somme de produits, car

elles ne conduisent aucune minimisation de leurs quations.

De nombreuses familles de circuits programmables disposent, en plus des

PLAs, doprateurs ou exclusifs pour faciliter la ralisation de ces fonctions

arithmtiques.

18

Oprateurs gnriques

4) Bascules:

Les circuits programmables actuels offrent tous la possibilit de crer

des fonctions squentielles, synchrones dans leur immense majorit.

les trois types fondamentaux de bascules:

19

Les optimiseurs dterminent automatiquement le type de bascule le

mieux adapt lapplication.

Oprateurs gnriques

Technologies

Le premier choix dun circuit programmable dpond de la technologie

utilise pour matrialiser les interconnexions:

maintien (ou non) de la fonction programme en labsence dalimentation,

possibilit (ou non) de modifier la fonction programme,

ncessit (ou non) dutiliser un programmateur.

20

1) Fusibles:

On ne la rencontre plus que dans quelques circuits de faible densit, de

conception ancienne.

Lors de la programmation le circuit est plac dans un mode, dans lequel des

impulsions de courant sont aiguilles successivement vers les fusibles

dtruire.

21

PLD lmentaire fusibles

Technologies

Pour programmer un circuit, il faut transfrer dans le programmateur

une table des fusibles qui indique par un chiffre binaire ltat de chaque

fusible. Cette table est gnralement transfre entre le systme de CAO

et le programmateur sous forme dun fichier au format normalis : le

format JEDEC.

Lexemple suivant prsente limplmentation dun compteur binaire 10

bits dans un circuit de type 22V10 :

22

Technologies

23

Inconvnients:

La programmation dtruit plus de fusibles quelle nen conserve.

Cela se traduit par une mauvaise utilisation du silicium, un temps de

programmation important (quelques secondes) et des contraintes

thermiques svres imposes au circuit lors de lopration.

Cette technologie nest donc pas gnralisable des circuits dpassant

quelques centaines de portes quivalentes.

24

Technologies

2) MOS grille flottante:

Les fusibles sont remplacs par des transistors grille isole (technologie FLASH).

Le transistor MOS grille flottante a permis de rendre le composant bloqu ou

passant sans application permanente d'une tension de commande. Le principe

consiste piger ou non ( l'aide d'une tension suprieure la tension d'alimentation)

des lectrons dans la grille.

Les Cellules transistor MOS grille flottante sont des cellules reprogrammables.

25

Technologies

3) Antifusibles: Linverse dun fusible

Un point dinterconnexion est ralis au croisement de deux pistes

conductrices, spares par un isolant de faible paisseur.

Une surtension applique entre les deux pistes provoque un perage

dfinitif du dilectrique, ce qui tablit la connexion.

Les points dinterconnexions ont un diamtre de lordre de la largeur

dune piste, cest dire de lordre du micron; il est donc possible de

prvoir un trs grand nombre dinterconnexions programmables. La

rsistance du contact cr est trs faible, de lordre dune cinquantaine

dohms (dix fois moins que celle dun transistor MOS), do des retards

lis aux interconnexions trs faibles galement.

Ces circuits ne sont programmables quune fois.

26

Technologies

Les cellules de connexion sont aujourd'hui ralises en technologie

MOS grille flottante. La structure de base comprend un circuit PLA

dont seule la matrice ET est programmable.

27

Architectures utilises

Structure dune PLD

La partie nomme OLMC (Output Logic MacroCell) sur la figure peut tre:

Combinatoire

Squentielle

Versatile

Combinatoire : une simple connexion relie alors la sortie du

OU l'entre du buffer de sortie, dont la sortie est rinjecte sur

le rseau programmable.

Les PALs

Squentielle: le bloc OLMC tant alors une simple bascule D ;

Il existe trois types:

R (Register):

Les PALs

Squentielle:

X (Register Or Exclusif):

Les PALs

Squentielle:

RA (Register Asynchron):

Les PALs

32

Les PALs

Les quatre configurations possible:

Versatile: il est possible par programmation de choisir entre les deux

configurations prcdentes.

Les PALs

f1 f0 Configuration des sorties

0 0 Combinatoire, actif bas

0 1 Combinatoire, actif haut

1 0 Registre, actif bas

1 1 Registre, actif haut

Macrocellule configurable

Dsignation:

Elle est de la forme : PAL EE T SS

o EE reprsente le nombre d'entres,

SS le nombre de sorties

et T le type du PAL

exemple : PAL 22V10.

Pour les dernires gnrations, on trouvera plutt la rfrence de type

GAL EE T SS, (GAL pour Generic Array Logic) pour dsigner un circuit

transistor MOS grille flottante, donc reprogrammable lectriquement.

34

Les PALs

Schma interne dun PAL 22V10 de AMD:

Les PALs

Structure gnrale

Symbolisation normalise

Les PALs

Structure et symbole:

Les CPLDs (Complex Programmable Logic Device)

Structure gnrale dun CPLD:

Ces circuits ont une capacit en nombre de portes et en possibilits de

configuration trs suprieure celle des PALs. Leurs architectures sont

bases sur celles des PALS. Un CPLD cest lquivalent de plusieurs PALs

mis dans le mme circuit associ une zone dinterconnexion. Le nombres

de portes peut varier entre 100 et 100 000 portes logiques et entre 16 et 1000

bascules voir plus.

38

Les FPGAs sont assimilables des ASIC (Application Specific Integrated

Circuit) programmables par lutilisateur. La puissance de ces circuits est

telle quils peuvent tre composs de plusieurs milliers voire millions de

portes logiques et de bascules structurs sous forme de matrices.

Les dernires gnrations de FPGA intgrent mme de la mmoire RAM.

Les deux plus grands constructeurs de FPGA sont XILINX et ALTERA.

Les FPGAs (Fields Programmable Gate Array)

Structure dun circuit FPGA :

39

Structure dun circuit FPGA

Les FPGAs

La structure du FPGA prsente est compose :

De cellules dE/S modifiables qui servent dinterfaces entre les broches

du circuit et le cur du FPGA pour adapter les signaux suivants :

Alimentation

Signaux dhorloge

Signaux de configuration du FPGA

Signaux de test

40

Les FPGAs

De blocs logiques: contenant les fonctions logiques combinatoires et

squentielles.

41

Les FPGAs

Exemple de blocs logiques de diffrents fabricants:

De rseaux dinterconnexions. Ces rseaux relient entre eux les

blocs logiques et les blocs dE/S.

42

Les FPGAs

Microprocesseur:

La prsence dun processeur est indispensable pour ordonnancer les

commandes reues par le FPGA.

Habituellement, ce processeur se trouve lextrieur du FPGA, mais des

constructeurs ont intgr ces systmes directement dans le FPGA. Il

sagit de processeur soft-core on parle aussi de systme sur puce

programmable (SOPC).

Il communique avec le FPGA grce au langage de description matrielle

VHDL. Ce processeur est donc reconfigurable pouvant ainsi dadapter

aux contraintes de chaque utilisation.

43

Les FPGAs

Avantages des FPGAs

Un circuit reprogrammable : modifier le programme gnrique de

base afin de le rendre spcifique au circuit utilis.

Un investissement rentable dans la dure : une rutilisation

destination dautres projets.

Une reprogrammation quasi-instantane du circuit. Rapide

implmenter un programme valider. A titre de comparaison, la

fabrication dun circuit ASIC peut prendre plusieurs semaines.

44

45

Ils sont composs en gnral de deux outils:

Le systme de dveloppement.

Le programmateur.

Le systme de dveloppement:

Ces systmes produisent une table reprsentant les fusibles

dtruire en fonction des quations logiques, diagramme d'tats et

tables de vrits crit dans le langage propre au systme, c'est le rle

du compilateur ou synthtiseur.

Les outils de dveloppements

46

La description du fonctionnement des circuits peut se faire de plusieurs

faons, soit :

Par un schma base de fonctions logique lmentaires (Portes,

bascules, compteurs, registres dcalages).

En utilisant un langage de description matriel HDL (Hardware

Description Language).

Par lutilisation de graphes dtats(FSM : Flow States Machines)

Les outils de dveloppements

Dveloppement des CPLDs et FPGAs

Vous aimerez peut-être aussi

- Rework - Réussir AutrementDocument236 pagesRework - Réussir Autrementforge209967% (6)

- Récupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriqueD'EverandRécupération D'Énergie: Transformer l'énergie ambiante présente dans l'environnement en énergie électriquePas encore d'évaluation

- MAITRISER Python : De l'Apprentissage aux Projets ProfessionnelsD'EverandMAITRISER Python : De l'Apprentissage aux Projets ProfessionnelsPas encore d'évaluation

- Apprendre et enseigner sur le Web: quelle ingénierie pédagogique?D'EverandApprendre et enseigner sur le Web: quelle ingénierie pédagogique?Pas encore d'évaluation

- Assemblages FiletésDocument33 pagesAssemblages FiletésLuka ModrićPas encore d'évaluation

- Cours4-Alternateur SynchroneDocument14 pagesCours4-Alternateur SynchroneChebbi GhaziPas encore d'évaluation

- 306 Diesel HDIDocument40 pages306 Diesel HDIcubhw100% (4)

- Gilet Rosa 2021 FR S1mhy6Document9 pagesGilet Rosa 2021 FR S1mhy6Annie LabiauPas encore d'évaluation

- Gestion Des RisquesDocument178 pagesGestion Des RisquesElbahaoui Abdel100% (1)

- Stage D'observation - GHAZY CHAIMAADocument42 pagesStage D'observation - GHAZY CHAIMAAMohammed NaouriPas encore d'évaluation

- Chap III LesmemoiresDocument12 pagesChap III LesmemoiresElbahaoui AbdelPas encore d'évaluation

- Lecture Schema Electrique BepDocument4 pagesLecture Schema Electrique BepMBIA FIDELIN YVES100% (2)

- Assembleur ExerciceDocument15 pagesAssembleur ExerciceMeryeme Bayri100% (1)

- Chapitre 5 VHDLDocument91 pagesChapitre 5 VHDLdhdhPas encore d'évaluation

- Schindler Bionic BXDocument228 pagesSchindler Bionic BXRaoul PetitPas encore d'évaluation

- Guide de Programmation Des DSPIC V1Document8 pagesGuide de Programmation Des DSPIC V1Elbahaoui AbdelPas encore d'évaluation

- Informatique Industrielle L3 SPI EEADocument44 pagesInformatique Industrielle L3 SPI EEALkhaybPas encore d'évaluation

- Telecharger-livre-Programmation Des PIC en CDocument39 pagesTelecharger-livre-Programmation Des PIC en CarnaudmarielPas encore d'évaluation

- Ondes AntennesDocument21 pagesOndes AntennesAziz YahyaPas encore d'évaluation

- Microsoft Word - Moteur Pas A PasDocument8 pagesMicrosoft Word - Moteur Pas A PasBa ChirPas encore d'évaluation

- Partie 7 initiationVHDLDocument17 pagesPartie 7 initiationVHDLMeriem MeriemPas encore d'évaluation

- Qcm2 AntenneDocument5 pagesQcm2 AntenneElbahaoui AbdelPas encore d'évaluation

- TD Réseau Correction PDFDocument10 pagesTD Réseau Correction PDFSarah BelemkaddemPas encore d'évaluation

- E2i3 Tp1 Cod Sopc Builder 2012Document27 pagesE2i3 Tp1 Cod Sopc Builder 2012Elbahaoui Abdel100% (1)

- FPGADocument49 pagesFPGAkachPas encore d'évaluation

- Chapitre 21 Fpga+VhdlDocument99 pagesChapitre 21 Fpga+VhdlnourPas encore d'évaluation

- 3cours FpgaDocument29 pages3cours Fpgabouda sofianePas encore d'évaluation

- TP PROTEUS - 3 - Logique Combinatoire (PB) - Doc RéponseDocument10 pagesTP PROTEUS - 3 - Logique Combinatoire (PB) - Doc RéponseerwPas encore d'évaluation

- Linux EmbarqueDocument338 pagesLinux EmbarqueAnthony GoninPas encore d'évaluation

- Architecture Des FPGADocument81 pagesArchitecture Des FPGARamzi Trabelsi100% (1)

- TP1 Info Indu Meca 2Document4 pagesTP1 Info Indu Meca 2Lotfi BoussaidPas encore d'évaluation

- Ex Corriges Oop w01Document13 pagesEx Corriges Oop w01FSE TICE100% (1)

- TP1: Configuration Et Utilisation Du CODEC ButDocument2 pagesTP1: Configuration Et Utilisation Du CODEC ButNinå Så50% (2)

- Lin BusDocument2 pagesLin Busachraf chbabPas encore d'évaluation

- Rapport FinalDocument88 pagesRapport FinalMaryem MhamdiPas encore d'évaluation

- TP Traitement Du Signal Sous Matlabv2Document23 pagesTP Traitement Du Signal Sous Matlabv2Razak TraorePas encore d'évaluation

- Algorithmique Et ProgrammationDocument15 pagesAlgorithmique Et ProgrammationLarbi BadrourPas encore d'évaluation

- FPGA VHDL TP3 SirineDocument15 pagesFPGA VHDL TP3 SirineGliouez SirinePas encore d'évaluation

- Cours SM en Ligne-ConvertiDocument72 pagesCours SM en Ligne-ConvertiAnfel CPas encore d'évaluation

- Cours VHDLDocument28 pagesCours VHDLRabhiHoucemPas encore d'évaluation

- Presentation VendredipptxDocument37 pagesPresentation VendredipptxaminaPas encore d'évaluation

- Chapitre 2 Caractéristiques Et Format de Calcul Des DSPDocument11 pagesChapitre 2 Caractéristiques Et Format de Calcul Des DSPHadjer BouPas encore d'évaluation

- 02 - Microcontroleur de La Famille PIC PDFDocument59 pages02 - Microcontroleur de La Famille PIC PDFFarid Afifi100% (1)

- Cours VHDL Fpga 1Document24 pagesCours VHDL Fpga 1BassoumaHhmdiPas encore d'évaluation

- Chapitre 4 Technologies Circuits Integres NumeriquesDocument8 pagesChapitre 4 Technologies Circuits Integres NumeriquesSOUKAINA AKHRAISPas encore d'évaluation

- Temporisation Logicielle 68HC11 PDFDocument2 pagesTemporisation Logicielle 68HC11 PDFTOUFIQPas encore d'évaluation

- TP7 - Modélisation en VHDL (2 Séances) : Exercice 7.1 - Un Additionneur/soustracteur 4 Bits (Séance 1)Document1 pageTP7 - Modélisation en VHDL (2 Séances) : Exercice 7.1 - Un Additionneur/soustracteur 4 Bits (Séance 1)Mohammed Es.slimaniPas encore d'évaluation

- Résumé Les Microcontrôleurs PIC 16f84 de Microchip 2 Bac Science DingenieurDocument2 pagesRésumé Les Microcontrôleurs PIC 16f84 de Microchip 2 Bac Science DingenieurTahiri Mehdi0% (1)

- RE Chap1 ENSATe - 2010 2011Document87 pagesRE Chap1 ENSATe - 2010 2011Med Reda CheffiPas encore d'évaluation

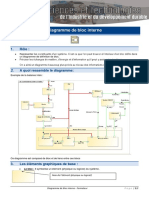

- 6 Diagramme de Bloc InterneDocument3 pages6 Diagramme de Bloc InternekamalPas encore d'évaluation

- ECos PresentationDocument18 pagesECos Presentationmalek hajjajiPas encore d'évaluation

- Dossier de Candidature Pour Un Poste de TechnologueDocument17 pagesDossier de Candidature Pour Un Poste de TechnologueMayssa RjaibiaPas encore d'évaluation

- PFCchapitre 2 Et 3Document24 pagesPFCchapitre 2 Et 3aaaa bbbb100% (1)

- Exam - ARCHITECTURE - Jan - 2021-V3 - CorrigéDocument2 pagesExam - ARCHITECTURE - Jan - 2021-V3 - CorrigéGANG SHOOTPas encore d'évaluation

- Les Metiers Mecatronique ConvertiDocument38 pagesLes Metiers Mecatronique ConvertiAmin ChabchoubPas encore d'évaluation

- Chapitre 3 l10-SystemCDocument170 pagesChapitre 3 l10-SystemCFaten ChebbiPas encore d'évaluation

- TD N°1 D'algorithmique AvancéeDocument1 pageTD N°1 D'algorithmique Avancéeimane taaPas encore d'évaluation

- Chapitre 0 Rappels Robotique PDFDocument63 pagesChapitre 0 Rappels Robotique PDFPaulHochonPas encore d'évaluation

- Exercices Rli 1Document7 pagesExercices Rli 1alex bbapPas encore d'évaluation

- TP - Outil de Simulation MATLABDocument17 pagesTP - Outil de Simulation MATLABRaphael RAKOTOARIVELOPas encore d'évaluation

- Tuto LogisimDocument12 pagesTuto Logisimadel ebrPas encore d'évaluation

- Rlire FipDocument23 pagesRlire FipOussama ObPas encore d'évaluation

- CoursAssembleur - Chap1 Et 2Document28 pagesCoursAssembleur - Chap1 Et 2Achraf ElkhodariPas encore d'évaluation

- Abaque SmithDocument9 pagesAbaque SmithNourdine Cherabit100% (2)

- Cours 68 HC 11 V 31Document55 pagesCours 68 HC 11 V 31Zineddine El Mehdi MustaphaPas encore d'évaluation

- Cours MicrocontrrolleurDocument65 pagesCours MicrocontrrolleurCrypto Sylvain100% (1)

- TP2 Automatisme Additionneur 4bitsDocument4 pagesTP2 Automatisme Additionneur 4bitsMed EL JaouhariPas encore d'évaluation

- Corrigé - TD N°2 - VHDL - VEtudDocument3 pagesCorrigé - TD N°2 - VHDL - VEtudhurnelPas encore d'évaluation

- Cours Microcontrôleur Microprocesseur 66 PDFDocument28 pagesCours Microcontrôleur Microprocesseur 66 PDFAbderrahim RiadPas encore d'évaluation

- Sujet C6Document39 pagesSujet C6Md AhmedPas encore d'évaluation

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesD'EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesPas encore d'évaluation

- Formation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesD'EverandFormation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesPas encore d'évaluation

- Etude de Cas LafargeDocument2 pagesEtude de Cas LafargeElbahaoui AbdelPas encore d'évaluation

- AbelVhdl IntetessantDocument69 pagesAbelVhdl IntetessantnoussaierPas encore d'évaluation

- Guide URKUND Pour Les EtudiantsDocument16 pagesGuide URKUND Pour Les EtudiantsElbahaoui AbdelPas encore d'évaluation

- Les Relations UE Chine PDFDocument11 pagesLes Relations UE Chine PDFElbahaoui AbdelPas encore d'évaluation

- Guide Redaction BiblioDocument14 pagesGuide Redaction BiblioMohamed Anouar BarkiPas encore d'évaluation

- Réduction D'ordre de Modèle D'un Phénomène D'amortissement Nonlinéaire Dans Le Cadre Des Microsystèmes.Document181 pagesRéduction D'ordre de Modèle D'un Phénomène D'amortissement Nonlinéaire Dans Le Cadre Des Microsystèmes.Elbahaoui AbdelPas encore d'évaluation

- Maintenance IndusDocument148 pagesMaintenance IndusElbahaoui Abdel100% (2)

- Freinage ElectriqueDocument1 pageFreinage ElectriqueElbahaoui AbdelPas encore d'évaluation

- 2-Principe de Programmation GrafcetDocument16 pages2-Principe de Programmation GrafcetElmokh LassaadPas encore d'évaluation

- Tic Trav07Document14 pagesTic Trav07Elbahaoui AbdelPas encore d'évaluation

- FSM VHDLDocument3 pagesFSM VHDLElbahaoui AbdelPas encore d'évaluation

- CoursMATLAB 1GET 2Document42 pagesCoursMATLAB 1GET 2Elbahaoui AbdelPas encore d'évaluation

- Theorie de L Information Et CodageDocument151 pagesTheorie de L Information Et CodageHisham BaskyPas encore d'évaluation

- 1l Cours StatistiquesDocument4 pages1l Cours StatistiquesElbahaoui AbdelPas encore d'évaluation

- Cours LangagecDocument259 pagesCours LangagecLounes MarmouchiPas encore d'évaluation

- Trans PC Reaction 2 e Me PartieDocument27 pagesTrans PC Reaction 2 e Me PartieElbahaoui AbdelPas encore d'évaluation

- Trame RC5Document7 pagesTrame RC5Elbahaoui AbdelPas encore d'évaluation

- GMAODocument4 pagesGMAOElbahaoui AbdelPas encore d'évaluation

- Schema Sonde Pression HulkDocument1 pageSchema Sonde Pression HulkElbahaoui AbdelPas encore d'évaluation

- PIC16F84Document22 pagesPIC16F84Elbahaoui AbdelPas encore d'évaluation

- Brochure Hyundai I20 FRDocument3 pagesBrochure Hyundai I20 FRMarc-Rémy N'driPas encore d'évaluation

- 1 Methodologie de DiagnosticDocument14 pages1 Methodologie de DiagnosticABDELALI SALAMPas encore d'évaluation

- Devoir de Contrôle N°1 - Technologie - Poste Automatique de Tronçonnage - 1ère AS (2013-2014) MR Chokri MessaoudDocument2 pagesDevoir de Contrôle N°1 - Technologie - Poste Automatique de Tronçonnage - 1ère AS (2013-2014) MR Chokri MessaoudKamel Tayahi100% (1)

- EP1340612A1Document15 pagesEP1340612A1IFOM IndusPas encore d'évaluation

- Les Machines ÉlectriquesDocument9 pagesLes Machines ÉlectriquesGildas HognonPas encore d'évaluation

- Fiches de ControleDocument16 pagesFiches de ControleNyangono SofyPas encore d'évaluation

- Avis D'agrement ReviseDocument7 pagesAvis D'agrement ReviseHama MaigaPas encore d'évaluation

- Audi Q3 SportbackDocument4 pagesAudi Q3 SportbackaminelahPas encore d'évaluation

- Peugeot 307: Graissage EntretienDocument1 pagePeugeot 307: Graissage EntretienECUSERVICE VIÑA DEL MARPas encore d'évaluation

- Brochure-TP EPuissDocument43 pagesBrochure-TP EPuissBousmaha Youcef100% (1)

- Exercice 8Document12 pagesExercice 8akouPas encore d'évaluation

- SSP 299 La Boîte Mécanique 6 Vitesses 08DDocument44 pagesSSP 299 La Boîte Mécanique 6 Vitesses 08DRatin RakotoarisonPas encore d'évaluation

- 77exposee EnglaisDocument3 pages77exposee EnglaisLamine MbayePas encore d'évaluation

- C Module AC03Document53 pagesC Module AC03LWAMBWA LandryPas encore d'évaluation

- Notice Reglage Wellcom X3DDocument8 pagesNotice Reglage Wellcom X3Dremi-93Pas encore d'évaluation

- CT-2019-CANAL - FAST Jia f25Document3 pagesCT-2019-CANAL - FAST Jia f25Amine FarsiPas encore d'évaluation

- Machine Synchrone: I. DescriptionDocument1 pageMachine Synchrone: I. DescriptionKawther BenPas encore d'évaluation

- Livre de L'enseignant 2ADocument110 pagesLivre de L'enseignant 2ACharles Steven MbomPas encore d'évaluation

- Formulaire Demande Attestation RemplissableDocument4 pagesFormulaire Demande Attestation RemplissableolivierPas encore d'évaluation

- Var FRDocument132 pagesVar FROnian HassanePas encore d'évaluation

- Schema ElectriqueDocument41 pagesSchema Electriqueben chrifa hamzaPas encore d'évaluation

- Disjoncteur de Branchement Erdf Fiche Technique Legrand DomomatDocument6 pagesDisjoncteur de Branchement Erdf Fiche Technique Legrand Domomatle.brieyPas encore d'évaluation